在現代電子設計中,電源完整性是PCB設計不可或缺的一部分。為了確保電子設備有穩定性能,從電源的源頭到接收端,我們都必須全面考慮和設計。如電源模塊、內層平面以及供電芯片等,通過精心設計和優化,才能實現真正意義上的電源完整性。本文將深入探討這三個關鍵方面,為PCB設計提供實用的指導和策略。

一、電源模塊布局布線

電源模塊是電子設備的能量來源,其性能與布局直接影響到整個系統的穩定性和效率。正確的布局和走線不僅能減少噪聲干擾,還能確保電流的順暢流通,從而提高整體性能。

1、電源模塊布局

● 源頭處理:電源模塊作為電源的起始點,布局時應特別注意,為了減小噪聲引入,應確保電源模塊的周圍環境盡量清潔,避免與其他高頻或噪聲敏感元件相鄰。

●靠近供電芯片:電源模塊應盡量靠近供電的芯片放置,這樣可以減小電流傳輸過程中的損耗,并降低內層平面的面積需求。

●散熱考慮:電源模塊在工作時可能會產生熱量,因此應確保其上方沒有遮擋物,以便于散熱,如有必要,可以加入散熱片或風扇進行散熱。

●避免環路:走線時應避免形成電流環路,以減少電磁干擾的可能性。

2、電源模塊走線

●寬度與電流:電源線的寬度應根據其所需承載的電流大小來確定,較大的電流需要更寬的線寬以確保電流能力。

●過孔數量:在電源線的走線過程中,如果需要穿越層面,應確保有足夠的過孔來承載電流,避免過孔過熱。

●距離與耦合:電源線與其他信號線之間的距離應適當,避免過于接近導致耦合效應。

●地線處理:地線作為回流路徑,應盡量確保地線的連續性,避免地線斷裂或突然變窄。

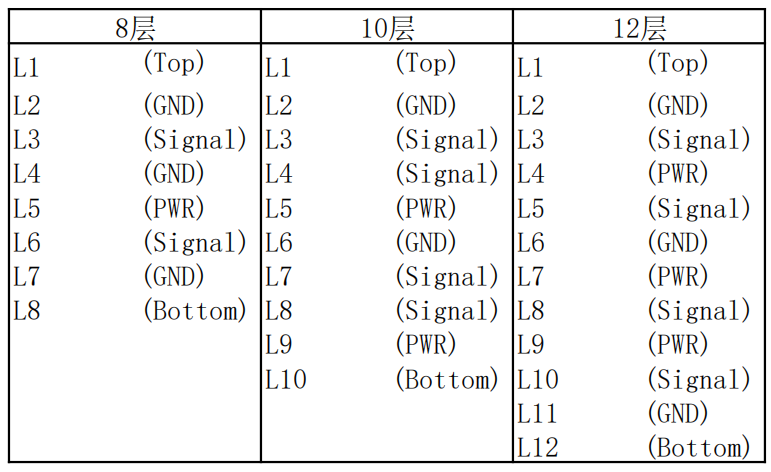

二、內層平面設計規劃

1、疊層設計

在PCB的EMC設計中,疊層設計是關鍵環節,需考慮布線與電源分割。

●為確保電源平面的低阻抗特性及電源噪聲的地耦合吸收,電源與地層間距應不大于10mil,通常建議小于5mil。

●若單一電源平面無法實現,可利用表層鋪設電源平面,緊相鄰的電源和地平面形成了一個具有最小交流阻抗的平面電容,具有優異的高頻特性。

●避免相鄰的兩個電源層過近(特別是電壓差異大的),以防止噪聲互相耦合,如不可避免,應盡量增加兩電源層間的間距。

●參考平面,特別是電源參考平面,應保持低阻抗特性,可通過旁路電容和疊層調整來優化。

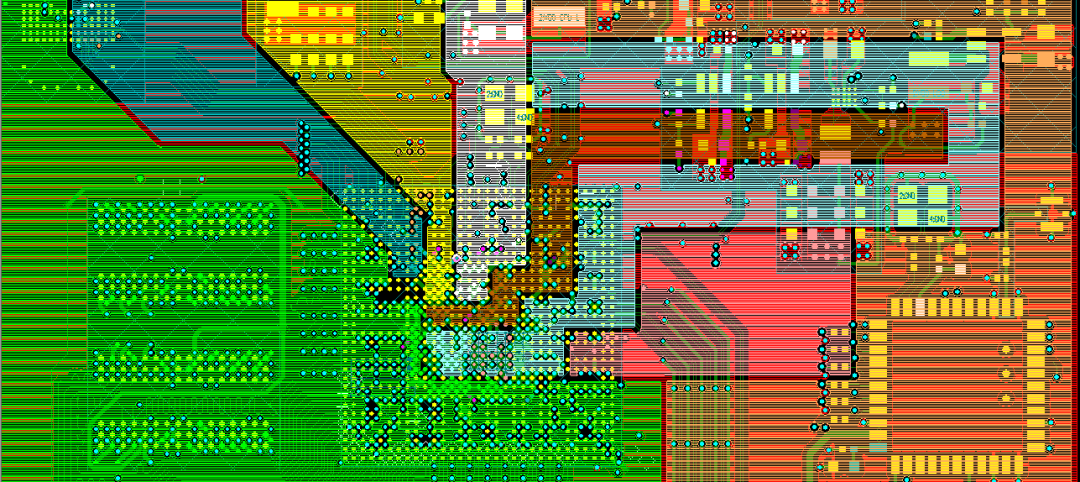

2、多種電源的分割

●對于小范圍的特定電源,如某IC芯片的核心工作電壓,盡量在信號層上敷銅,以確保電源層的完整性,但避免在表層敷電源銅皮,減少噪聲輻射。

●分割寬度選擇應適當,電壓大于12V時,寬度可為20-30mil;反之選12-20mil,模擬與數字電源的分割寬度需加大,防止數字電源對模擬電源的噪聲干擾。

●簡潔的電源網絡應在走線層完成,而較長的電源網絡需加濾波電容。

●分割后的電源平面應保持規則,避免不規則形狀導致諧振和電源阻抗增加,不允許有細長條和啞鈴形分割。

3、平面濾波

●電源平面應與地平面緊密耦合。

●工作頻率超過500MHz的芯片,應主要依靠平面電容濾波,并采用組合電容濾波,濾波效果需通過電源完整性仿真確認。

●控制平面去耦電容的安裝電感,如加寬電容引線、加大電容過孔等,確保電源地阻抗低于目標阻抗。

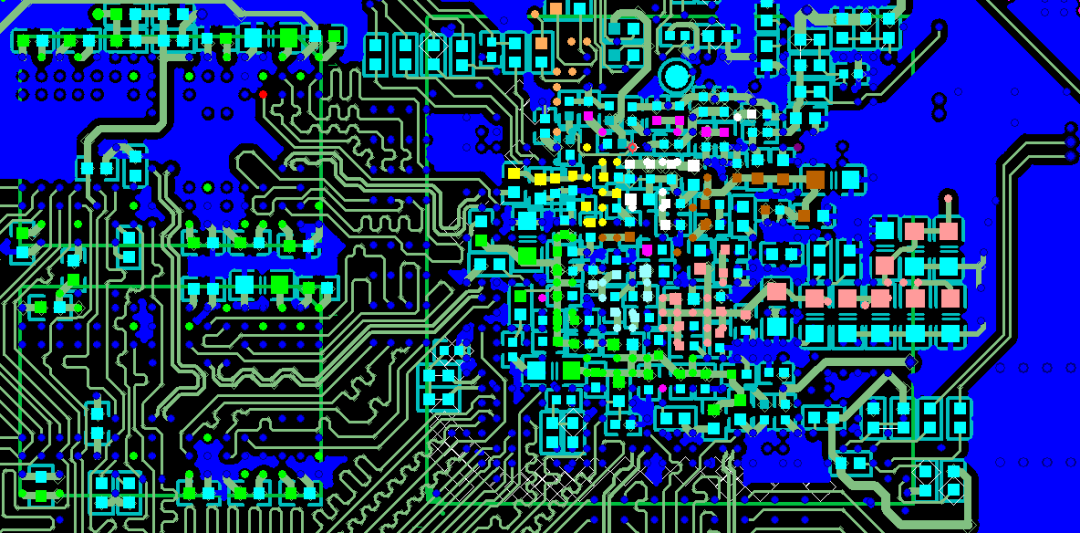

三、供電芯片布局布線

供電芯片是電子設備的核心,確保其電源完整性是提高設備性能與穩定性的關鍵,以下展開說明。

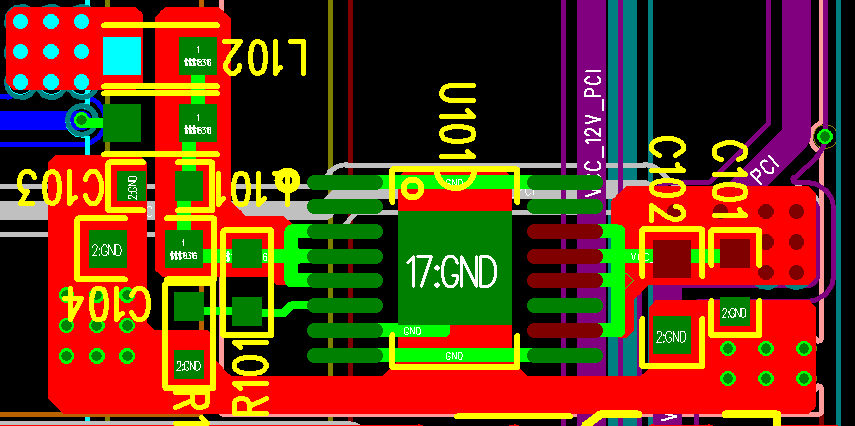

1、芯片電源管腳的走線處理

為了提供穩定的電流供應,建議將電源管腳走線加粗,一般應加粗至與芯片管腳相同的寬度。

通常,最小的寬度不應小于8mil,但為了達到更佳的效果,盡量將寬度做到10mil。

通過增加走線寬度,可以降低阻抗,從而減少電源噪聲,并確保足夠的電流供應給芯片。

2、去耦電容的布局與布線

去耦電容在供電芯片的電源完整性控制中發揮著重要作用,根據電容的特性和應用需求,去耦電容一般分為大電容和小電容兩種。

●大電容:大電容通常均勻分布在芯片周圍,由于其諧振頻率較低,濾波半徑較大,它們能夠有效地濾除低頻噪聲,并提供穩定的電源供應。

●小電容:小電容的諧振頻率較高,濾波半徑較小,因此應該盡量靠近芯片管腳放置,如果放置過遠,可能無法有效濾除高頻噪聲,失去去耦的作用。

3、并聯多個去耦電容的布線方式

為了進一步提高電源完整性,通常會采用并聯多個去耦電容的方式,這樣可以利用電容的并聯,來降低單個電容的等效串聯電感(ESL)。

在并聯多個去耦電容時,需要注意電容的打孔方式:將電源和地的過孔相互錯開打孔。這樣可以降低去耦電容之間的互感,確保互感遠小于單個電容的ESL,從而實現并聯多個去耦電容后,整體ESL的阻抗為1/N,同時通過降低互感,可以有效地提高濾波效果,并確保電源穩定性的提升。

在實踐中,我們需要綜合考慮各種因素,如電流大小、走線寬度、過孔數量、耦合效應等,以做出合理的布局和走線決策。同時,遵循設計規范和最佳實踐,確保電源完整性的控制和優化。使用華秋DFM軟件,可以檢查最小線寬、線距等多項工藝問題,簡單便捷使PCB設計規范化。

華秋DFM軟件是國內首款免費PCB可制造性和裝配分析軟件,擁有300萬+元件庫,可輕松高效完成裝配分析。其PCB裸板的分析功能,開發了19大項,52細項檢查規則,PCBA組裝的分析功能,開發了10大項,234細項檢查規則。

基本可涵蓋所有可能發生的制造性問題,能幫助設計工程師在生產前檢查出可制造性問題,且能夠滿足工程師需要的多種場景,將產品研制的迭代次數降到最低,減少成本。

華秋DFM軟件下載地址(復制到電腦瀏覽器打開):

https://dfm.elecfans.com/dl/software/hqdfm.zip?from=fsyzlh

● 微信搜索【華秋DFM】公眾號,關注獲取最新可制造性干貨合集

-

電源

+關注

關注

185文章

18840瀏覽量

263499 -

PCB設計

+關注

關注

396文章

4920瀏覽量

95234 -

PCB

+關注

關注

1文章

2307瀏覽量

13204

發布評論請先 登錄

Cadence工具如何解決芯粒設計中的信號完整性挑戰

是德DSOX1204A示波器在電源完整性測試中的關鍵優勢

信號完整性(SI)/ 電源完整性(PI)工程師的核心技能樹體系

了解信號完整性的基本原理

Samtec虎家大咖說 | 淺談信號完整性以及電源完整性

電源完整性基礎知識

各種常用電路模塊設計原則:電源完整性

受控阻抗布線技術確保信號完整性

信號完整性測試基礎知識

電源完整性分析及其應用

普源示波器在信號完整性分析中的應用研究

電源完整性設計的重要三步講解!

電源完整性設計的重要三步講解!

評論