?鋪銅Plane

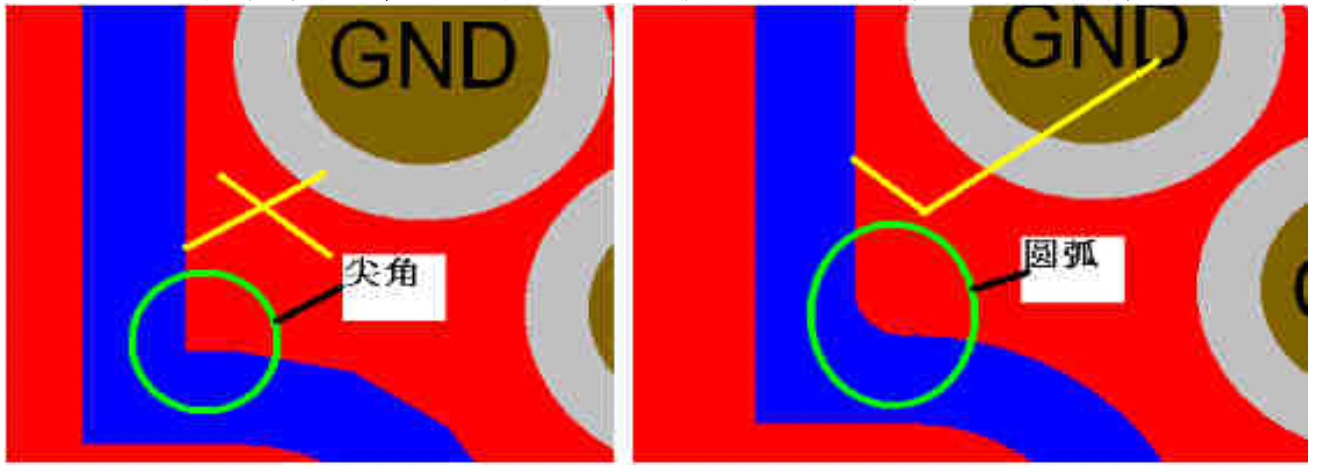

1.1 不要鋪成尖角出現,會變成電磁波的能量輻射出去,請將鋪成弧!

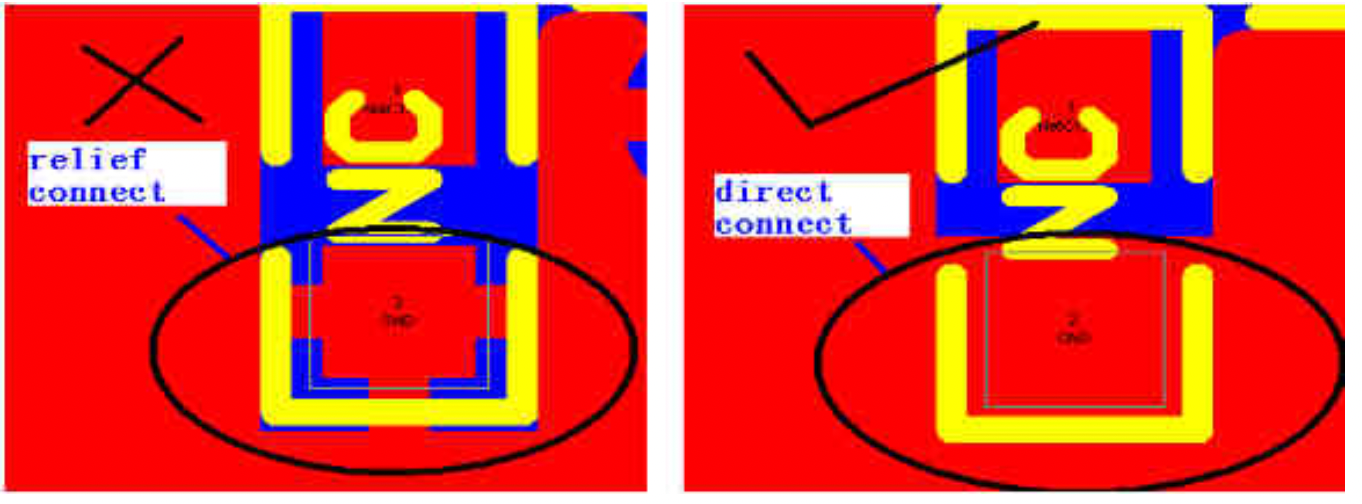

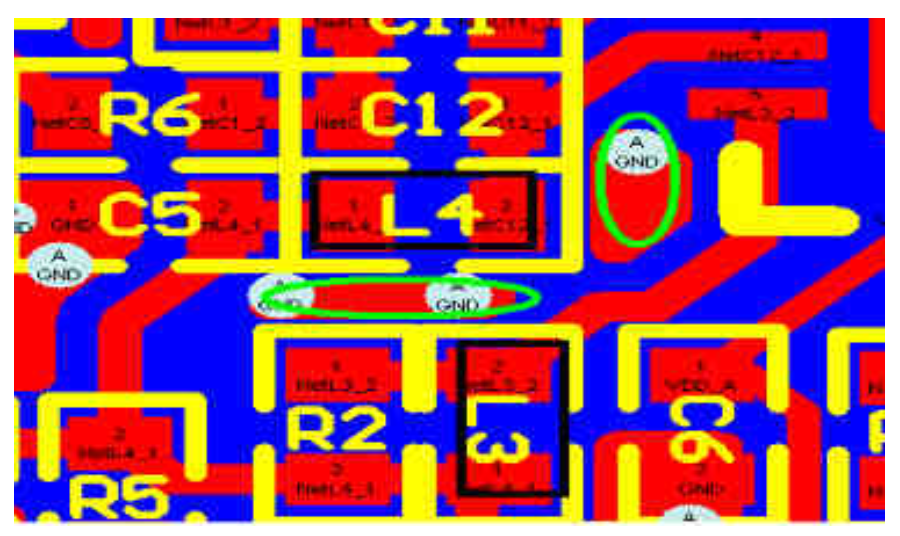

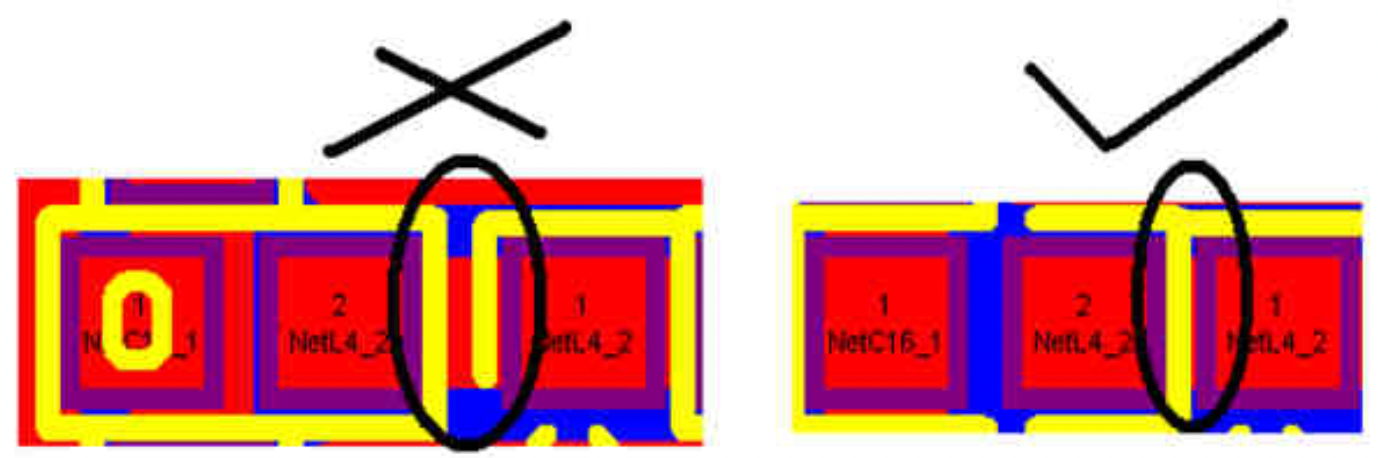

1.2 鋪銅連接方式,請設定為direct connect ,不要設定relief connect;目的為增加下地PAD的接地面積

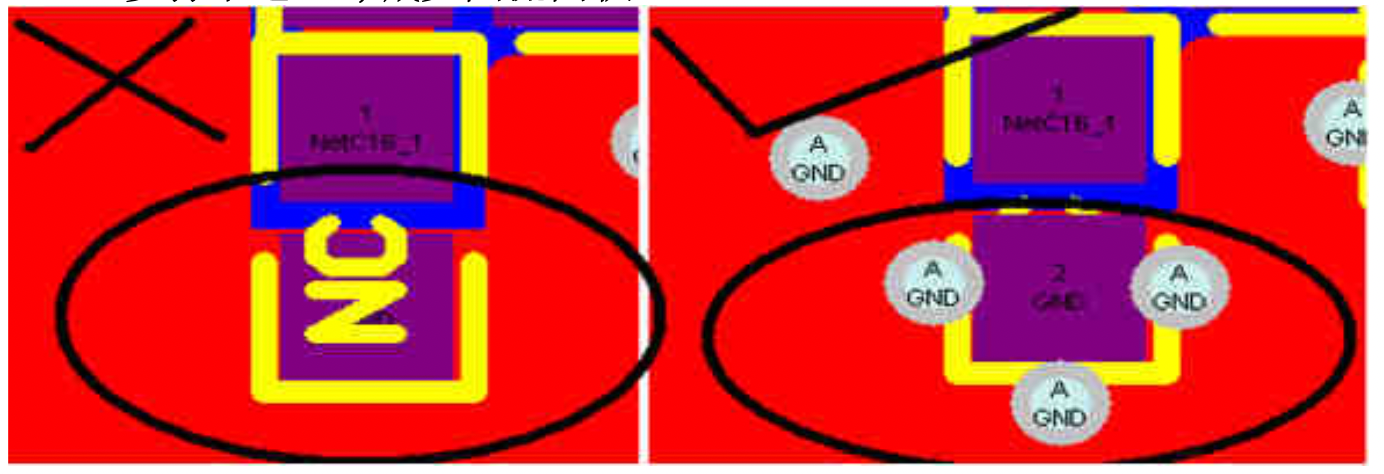

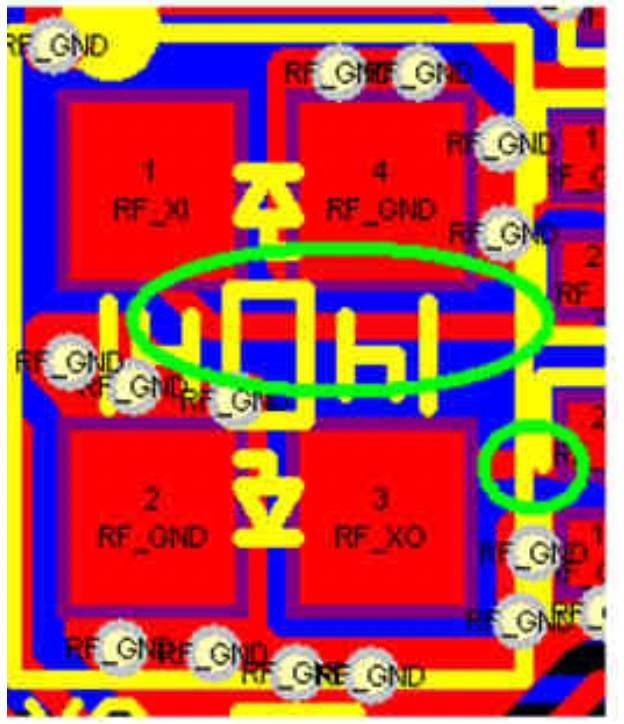

2.元器件接地的腳周圍的盡量多打下地via

2.1多打via,減少寄生電感的影響,增加接地性

2.2Via要打得巧,緊靠下地pad(切記打在pad上面,防止元件吃錫不足)

2.3多打下地via,減少回流面積。

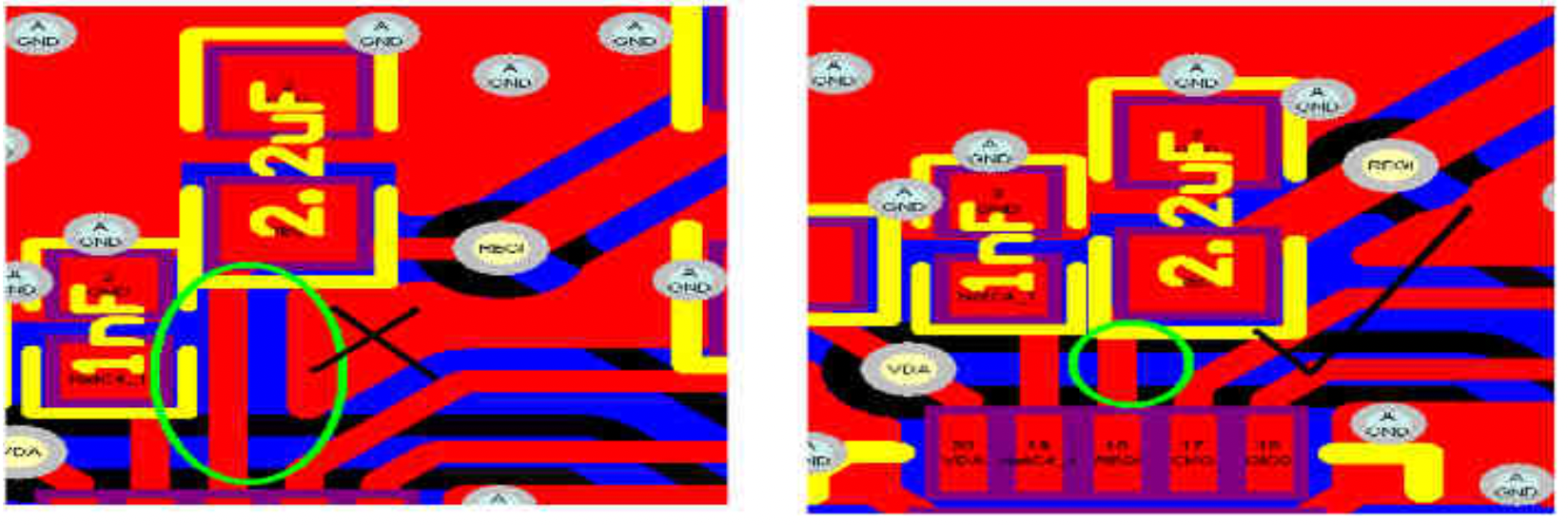

3.RF輸入輸出(pin3 & pin4)電路中下方不能有電源走線

3.1:高頻線與 電源會相互干擾,會影響power 及感度 輸出

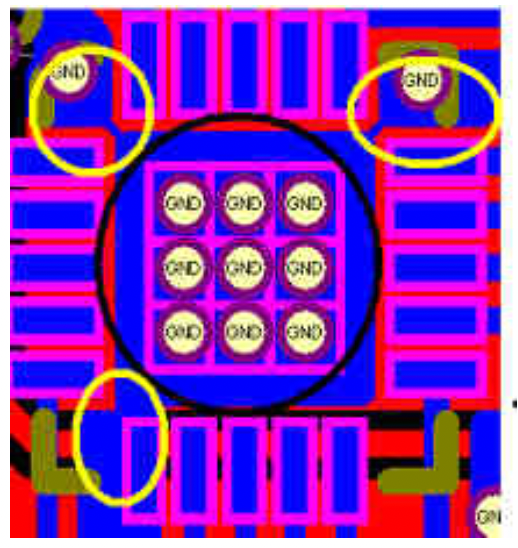

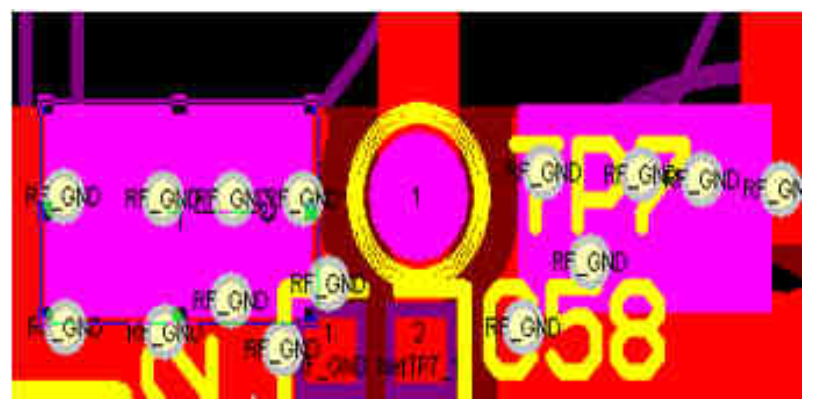

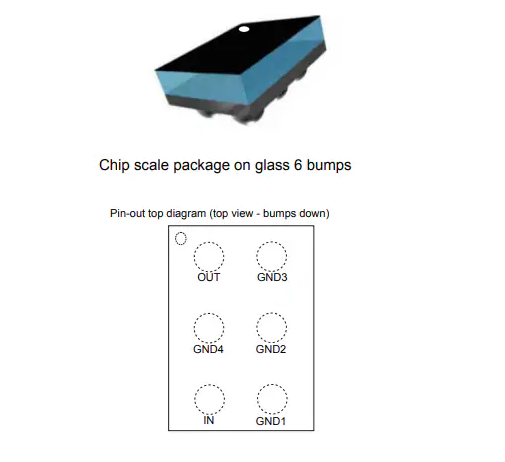

4.IC PCB 封裝底部請打九個via下地

4.1QFN封裝,底部為地,必須通過一些via將芯片地與PCB地很好的結合起來

4.2IC背面接地區域四角盡量延伸與toplayer大地相連,增加IC底部接地面積

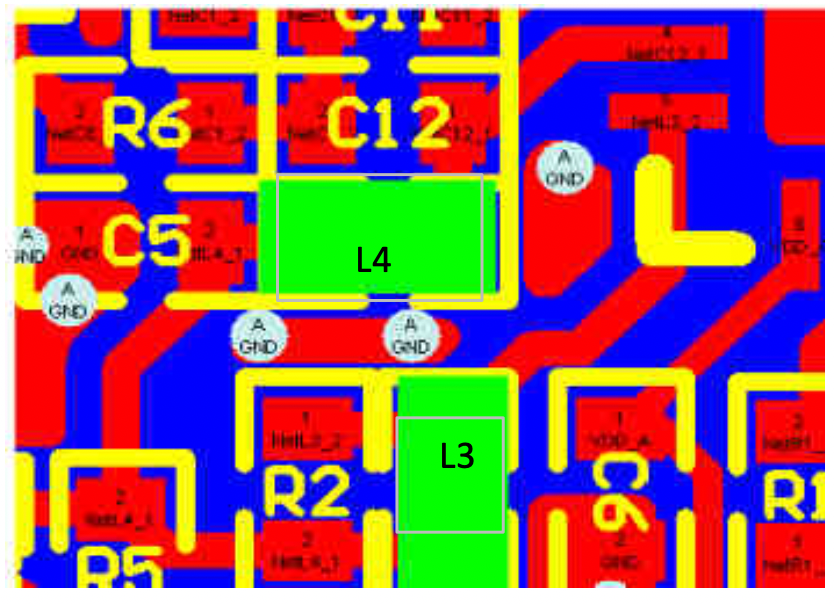

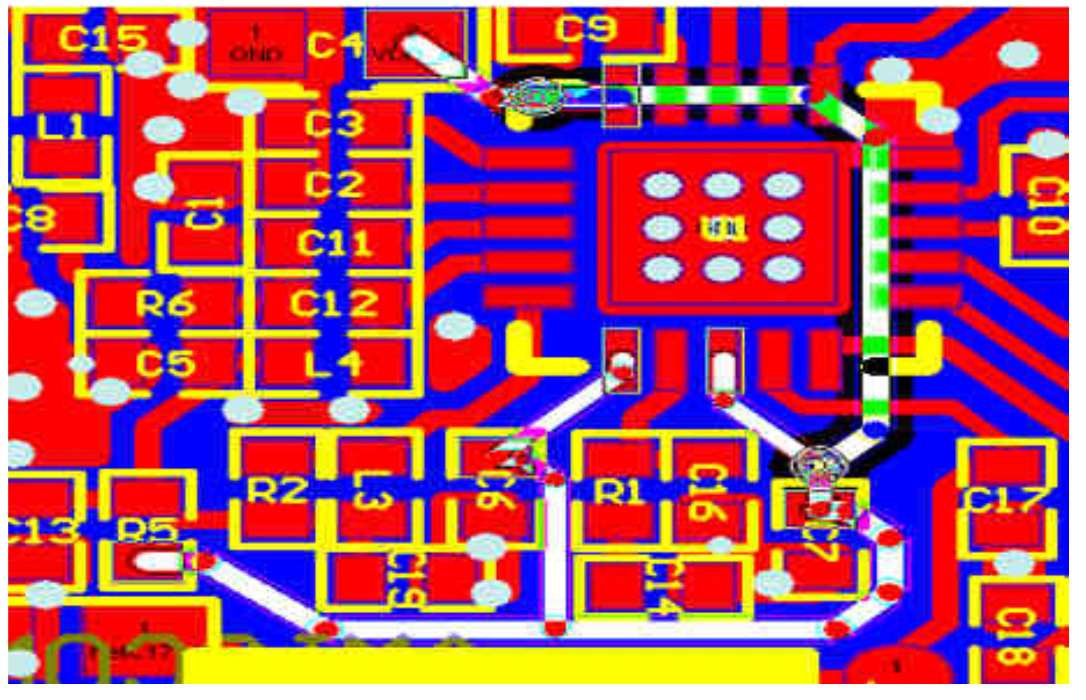

5.在射頻前端電路,相鄰電感要相互垂直放置,以避免互感,減少耦合

5.1L3與L4之間之間打via走一段地線做隔離

5.2Pin4與pin5之間打via走一段地線做隔離

5.3由于L3與R2并聯,L3應該選擇更靠近IC pin腳

6.電路元器件,盡量絲印緊靠,并使用較小封裝

6.1目的是減少兩元件之間的走線,減少走線的電感量產生

7電源走線

7.1電源濾波電路中的電容盡量靠近VDD pin腳,以確保濾波電容與進入VDD的環路面積最小

7.1.1強調一點:參考電路中的電源濾波電容一個都不能少,每個電容都有其不同的作用,少了會有死機或振蕩現象

7.1.2進入IC之前,電源先經過大電容,再經過小電容濾波(小電容靠近IC pin,大電容放外面)

8.晶振

8.1晶振size3225,PCB封裝中間是可以走線的

8.1.1晶振有49S插件;還有size更小的2520貼片封裝

8.2晶振盡量靠近IC,減少晶振走線長度,同時晶振及其晶振走線下方不要走任何走線

8.3晶振接地PAD,請在PAD邊緣多打下地via,(切記不要打在pad上面,防止晶振吃錫不足)

9.務必要留出測試點,為了for研發調試及治具測試 測試點size直徑最少大于1.5mm 兩測試點之間大于2.0mm

9.1留出SPI測試點 (SCS SCK SDIO GIO1 GIO2)

9.2 留出REGI(電源)及GND測試點

9.3留出RF測試點及RF參考地測試點

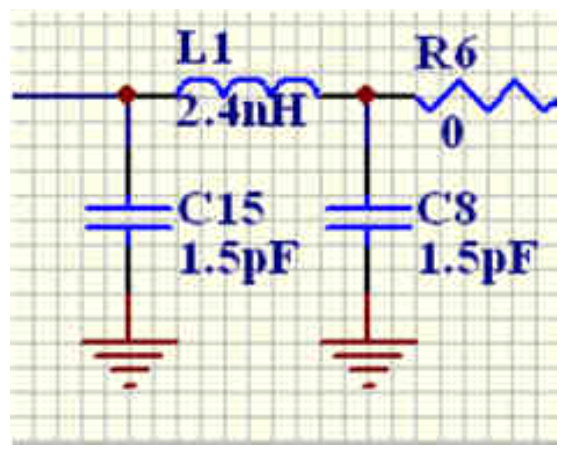

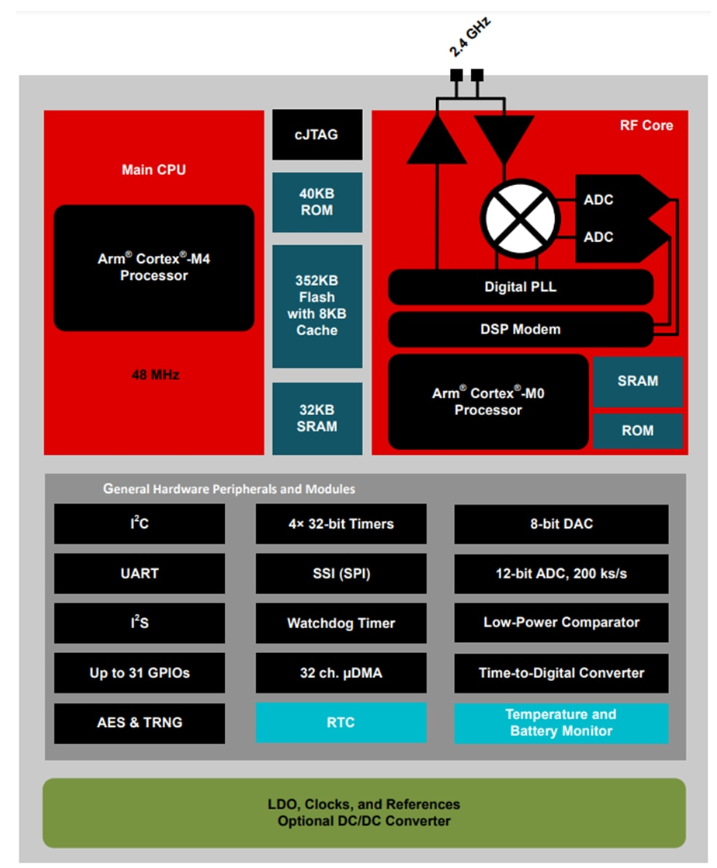

10.濾波器架構

10.1:濾波器架構是為了for法規使用,如果不過法規,濾波電路可以省掉,或者用來調適與天線的50ohm匹配

11.電源VDDA走線

11.1電源VDDA走線建議下圖

11.2Pin7為鎖相環電路,VDDA走線請遠離鎖相電路,不要走在其下方

11.3不建議電源VDDA走線走IC正下面,請走IC外圍

12.洗板

12.1板厚:0.8mm

12.2板材:FR-4

12.3表面:鍍化金

12.4Via :蓋油

13.畫板時: 有時候因為面積限制,元器件不見得都要90度擺放(垂直或水平), 可以用任意角度(ex: 45, 30度)來擺放

?審核編輯 黃宇

-

pcb

+關注

關注

4404文章

23877瀏覽量

424226 -

RF

+關注

關注

66文章

3201瀏覽量

171794 -

2.4GHz

+關注

關注

0文章

49瀏覽量

18857

發布評論請先 登錄

CC2520 2.4GHz IEEE 802.15.4/ZigBee? RF收發器深度解析

探索CC2590:2.4GHz RF前端的卓越之選

探索CC2531:2.4GHz IEEE 802.15.4與ZigBee應用的理想之選

CC2543:2.4GHz RF應用的集成化解決方案

深入解析CC2545:2.4GHz RF應用的理想片上系統解決方案

內置2.4GHz有源模塊PDA手持終端深度評測

?MLPF-WB-01D3 2.4GHz低通濾波器技術解析與應用指南

Texas Instruments CC2651R3 SimpleLink? 2.4GHz無線MCU技術解析

2.4GHz 高功率 802.11n WLAN 線性功率放大器 skyworksinc

CMOS 2.4GHZ 發射/接收 WLAN RFeIC skyworksinc

2.4GHZ 發送/接收 ZIGBEE RFEIC,帶分集開關 skyworksinc

2.4GHZ CMOS WLAN/BT 雙模 RFEIC,帶 PA、LNA skyworksinc

CMOS 2.4GHZ ZIGBEE/ISM 發射/接收 RFeIC skyworksinc

2.4GHz?RF?IC 布局指導

2.4GHz?RF?IC 布局指導

評論