新思科技攜手Ansys針對三星晶圓代工14LPU工藝開發全新射頻集成電路設計參考流程

該合作讓新思科技領先的定制設計流程和Ansys黃金簽核電磁(EM)分析工具強強聯手實現預測精度,為共同客戶提供全球領先的設計結果質量

新思科技(Synopsy)近日宣布,攜手Ansys 、三星半導體晶圓代工(以下簡稱“三星”)共同開發了面向三星14LPU工藝的全新射頻集成電路(RFIC)設計參考流程,助力5G/6G片上系統(SoC)和自動駕駛系統開發者應對日益增加的設計挑戰。該參考流程讓共同客戶能夠采用Ansys的黃金簽核精度電磁分析和新思科技的綜合模擬/射頻和混合信號設計及驗證解決方案,以更好地優化其RFIC設計。

下一代無線通信和傳感器系統必須滿足一系列要求,包括更高的帶寬、更低的延遲、更好的覆蓋率,并支持互聯設備的擴展。高頻設計要經過設計元素之間的電磁(EM)耦合,需要非常高精度的建模引擎才能實現準確預測。電磁建模必須與版圖開發平臺緊密結合,以確保實現快速的數據共享、易于調試、高生產率和清晰的可視化結果。

該參考流程的關鍵組件包括新思科技定制設計系列產品,其中包括新思科技PrimeSim電路仿真解決方案,以及由Ansys RaptorX電磁建模系列、Ansys Exalto電磁提取和簽核和Ansys VeloceRF電感器和變壓器設計工具提供的電磁簽核收分析。

“高頻和無線電應用正在向智能手機、5G/6G、自動駕駛、可穿戴設備和物聯網等更廣的工業和消費應用領域擴展。隨著越來越多的客戶開始進行射頻和電磁設計,我們與新思科技和Ansys推出的全新14LPU參考流程提供了一條順暢且全面的路徑,可以充分利用三星第四代14納米工藝的速度和性能優勢,助力客戶更快、更可靠地完成設計。”

“隨著頻率攀升到射頻范圍,為了優化芯片的功率、面積、性能和可靠性,我們的客戶正面臨著全新的多物理場挑戰。我們與新思科技緊密合作,因此在針對三星客戶需求而創建的完整定制設計流程中,能夠便捷使用我們業界領先的電磁建模技術。”

“新思科技和Ansys基于數十年的半導體專長和發展經驗,攜手助力我們的共同客戶降低設計風險并加速成功。我們與Ansys針對三星14納米工藝節點推出的全新射頻設計參考流程,可提供一個開放和優化的流程,為先進的5G/6G無線系統交付出卓越的設計結果質量。”

審核編輯:劉清

-

無線通信

+關注

關注

58文章

4987瀏覽量

146882 -

片上系統

+關注

關注

0文章

202瀏覽量

27684 -

RFIC

+關注

關注

1文章

65瀏覽量

25295 -

新思科技

+關注

關注

5文章

956瀏覽量

52894 -

射頻設計

+關注

關注

0文章

59瀏覽量

9123

原文標題:新思科技攜手Ansys和三星,以14nm射頻設計加速6G到來

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PDK在集成電路領域的定義、組成和作用

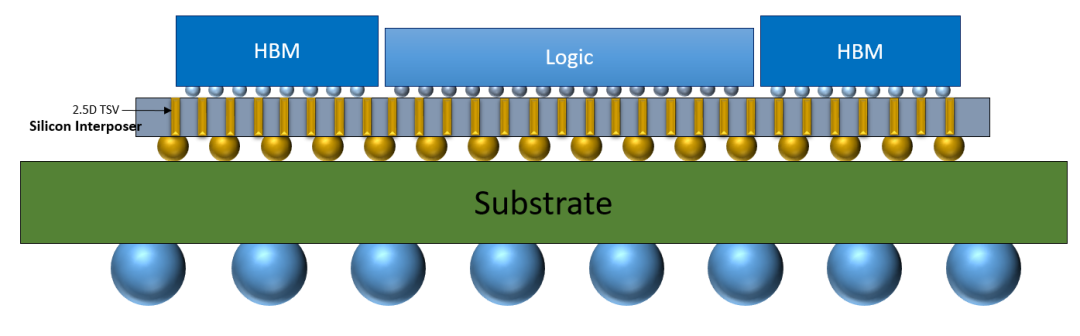

新思科技與三星深化合作加速AI和Multi-Die設計

新思科技完成對Ansys的收購

新思科技攜手是德科技推出AI驅動的射頻設計遷移流程

新思科技攜手深圳大學助力數字集成電路人才培養

外媒稱三星與英飛凌/恩智浦達成合作,共同研發下一代汽車芯片

回收三星S21指紋排線 適用于三星系列指紋模組

詳細解讀三星的先進封裝技術

中國集成電路大全 接口集成電路

法動科技EMOptimizer解決模擬/射頻集成電路設計難題

新思科技攜手Ansys和三星共同開發14LPU工藝的全新射頻集成電路設計

新思科技攜手Ansys和三星共同開發14LPU工藝的全新射頻集成電路設計

評論