電子發(fā)燒友網(wǎng)報道(文/李寧遠)在算力向更高水平發(fā)展的推動下,數(shù)據(jù)量在飛速膨脹,尤其是AI大模型、機器學習等新的數(shù)據(jù)中心業(yè)務流量正在推動端到端以及到用戶的成倍的數(shù)據(jù)增長。

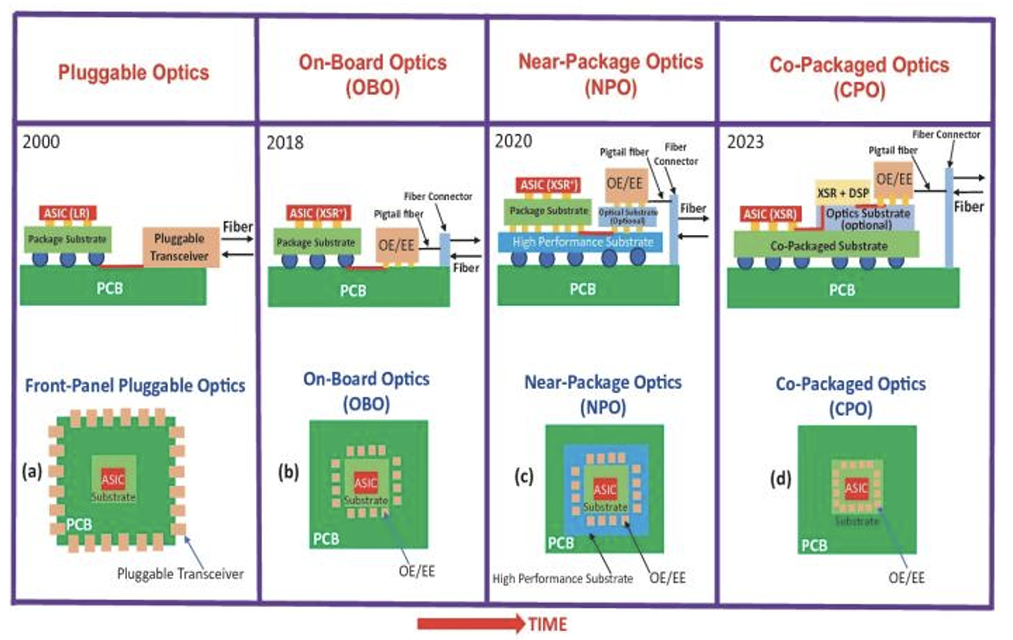

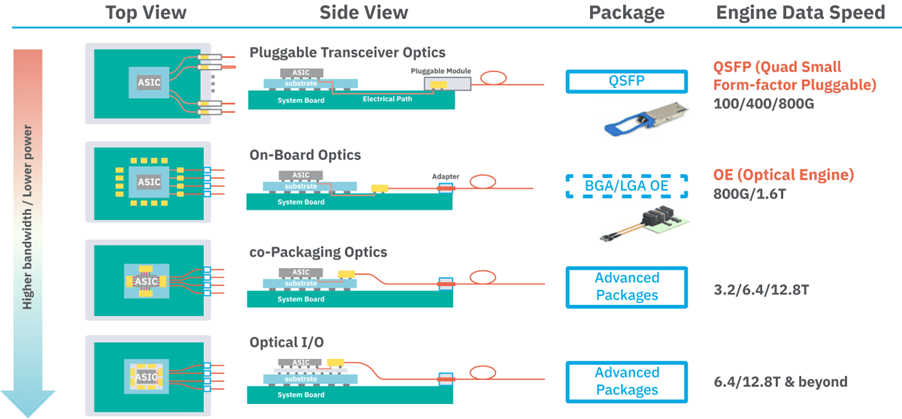

海量的數(shù)據(jù)需要迅速地流轉(zhuǎn)至各個角度,數(shù)據(jù)傳輸速率也從100GbE向400GbE,甚至800GbE的方向發(fā)展,以匹配暴增的算力和數(shù)據(jù)交互需求。線路速率的升級,相關(guān)硬件的板級復雜性大大增加,傳統(tǒng)I/O已經(jīng)無法應對將高速信號從ASIC傳輸?shù)角懊姘鍟r各種需求。在此背景下,CPO光電共封裝受到追捧。

數(shù)據(jù)處理需求激增,CPO光電共封受關(guān)注

在傳統(tǒng)的光通信系統(tǒng)中,光學模塊和AISC(網(wǎng)絡(luò)交換芯片)是分開封裝的,光模塊以可插拔的模式插在交換機的前面板上。可插拔的模式想必都不陌生,傳統(tǒng)的I/O連接很多都以可插拔的模式連接在一起。

雖然目前可插拔仍舊是技術(shù)路線上的首選,但可插拔模式已經(jīng)在高數(shù)據(jù)速率下暴露出一些問題,光器件和電路板之間的連接長度、信號傳輸損耗、功耗、質(zhì)量隨著數(shù)據(jù)處理速度需求的進一步增加都會受到制約。

為了解決傳統(tǒng)連接的制約,CPO光電共封裝開始受到關(guān)注。光電共封裝全稱Co-packaged optics,即將光模塊和AISC(網(wǎng)絡(luò)交換芯片)封裝在一起,通過短距離的電連接將它們連接起來,從而實現(xiàn)緊湊的光電一體化。

CPO光電共封裝帶來的尺寸和重量的優(yōu)勢是很明顯的,實現(xiàn)了高速光模塊的小型化和微型化。光模塊和AISC(網(wǎng)絡(luò)交換芯片)在板上更加集中,光纖長度可以大大減少,這就意味著可以降低傳輸時的損耗。

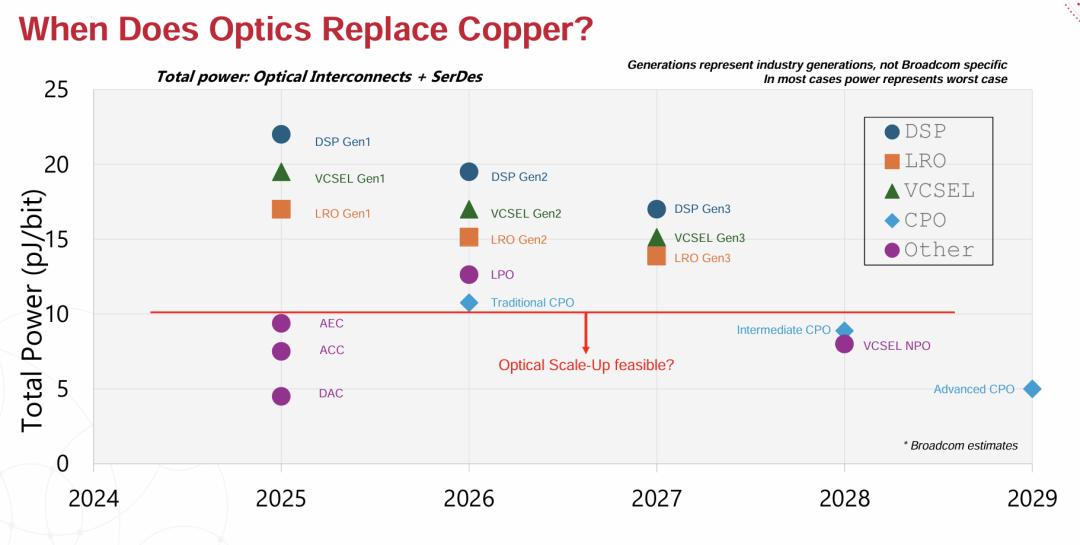

根據(jù)Ayar Labs的測試數(shù)據(jù),CPO光電共封裝甚至能夠相較于可插拔的光模塊直接把功耗降低一半。根據(jù)博通的測算,在400G可插拔光模塊上,CPO的方案在功耗上能節(jié)約50%左右,1600G可插拔光模塊相比,CPO方案能節(jié)約的功耗將更多。

更集中的布局也使得互連密度大幅提升,電信號的延遲和失真都會有所好轉(zhuǎn),傳輸速度的制約也不再像傳統(tǒng)可插拔模式。

還有一點則是成本,今天的人工智能、服務器和交換機系統(tǒng)要求極高的密度和速度,電流需求迅速增加,在不使用CPO共封裝的情況下,需要大量的高端連接器將光模塊連接起來,這是很大的成本。CPO共封裝可以減少的連接器也是降低BOM中的很大一部分。

CPO光電共封裝是實現(xiàn)高速率高帶寬低功耗網(wǎng)絡(luò)的必經(jīng)之路,這種將硅光電元件和電子組件封裝在一起的技術(shù),使得光模塊盡可能地靠近網(wǎng)絡(luò)交換芯片減少了通道損耗和阻抗不連續(xù)問題,大大提高了互連密度為未來更高速率數(shù)據(jù)連接提供了技術(shù)支持。

CPO光電共封裝技術(shù)演化與進展

光電共封裝其實并不是一個全新的技術(shù),其發(fā)展可以追溯至上世紀60年代,不過此時的光電共封裝還只是簡單地將光電子器件封裝在一起。到90年代,隨著光通信模塊產(chǎn)業(yè)起量,光電共封裝開始嶄露頭角。隨著今年高算力高帶寬需求的井噴,和其相關(guān)的分支技術(shù)光電共封裝也再次受到大量關(guān)注。

CPO光電共封裝在技術(shù)發(fā)展中,每一階段也有著不同的形式,對應20/50Tb/s需求的2.5D CPO,到對應50/100Tb/s需求的2.5D Chiplet CPO,最后實現(xiàn)對應100Tb/s速率以上的3D CPO。

2.5D CPO將光模塊與網(wǎng)絡(luò)交換芯片封裝在同一個基板上,縮短線距,增加I/O 密度,3D CPO則直接光學IC直接連接到中介層上,實現(xiàn)小于50um pitch的I/O間距的互連。其演進目標非常明確,就是要盡可能地將光電轉(zhuǎn)換模塊與網(wǎng)絡(luò)交換芯片之間的距離縮小。

目前CPO還處于起步階段,還存在良率過低、維護成本高等問題,市面上能完整提供CPO相關(guān)產(chǎn)品的廠商很少。市面上推出完整專有方案的也只有博通、Marvell、英特爾以及少數(shù)其他一些參與者。

Marvell去年就推出了一款采用VIA-LAST工藝的2.5D CPO技術(shù)的交換機,在硅光芯片加工完成后,借助OSAT的加工能力加工出TSV, 進而將電芯片flip-chip到硅光芯片上,將16個光模塊和交換芯片Marvell Teralynx7在PCB上互連形成交換機,可達到12.8Tbps 的交換速率。

今年的OFC上,博通和Marvell也都展示了各家最新一代采用光電共封裝技術(shù)的51.2Tbps交換機芯片。

從博通的最新一代CPO技術(shù)細節(jié)來看,CPO 3D封裝通過工藝的改進實現(xiàn)了更高的I/O密度,將CPO的功耗做到了5.5W/800G,能效比很高性能非常優(yōu)秀。同時博通也在向單波200Gbps、102.4T的CPO突破。

思科也加大了對CPO技術(shù)的投入,在今年OFC中做了CPO產(chǎn)品的演示,演示中展示其CPO技術(shù)積累,在集成度更高的多路復用器/解復用器上的應用。思科表示將在51.2Tb交換機中進行CPO的試驗性部署,然后在102.4Tb交換機周期內(nèi)進行大規(guī)模應用。

英特爾很早就推出了基于CPO的交換機,最近幾年英特爾也在持續(xù)Ayar Labs合作探索共封裝更高的帶寬信號互連方案,為光電共封裝和光互連器件的量產(chǎn)鋪平道路。

雖然目前可插拔模塊仍然是首選,但是CPO能帶來的整體能效的提升已經(jīng)吸引了越來越多廠商。根據(jù)光通訊調(diào)研機構(gòu)LightCounting預測,CPO出貨量將從800G和1.6T端口開始出現(xiàn)明顯增長,2024至2025年逐步開始商用,2026至2027年形成規(guī)模上量。同時CIR預計,2027年光電共封裝的市場收入將達到54 億美元。

這一預期與臺積電對于CPO市場的判斷差不多,今年早些時候,臺積電宣布將攜手博通、英偉達等大客戶共同開發(fā)硅光子技術(shù)、共同封裝光學元件CPO等新產(chǎn)品,制程技術(shù)從45nm延伸到7nm,并表示最快明年下半年開始迎來大單,2025年左右達到放量階段。

國內(nèi)廠商也在緊鑼密鼓推進CPO技術(shù)應用,光迅、劍橋科技、博創(chuàng)科技、中際旭創(chuàng)等都有相關(guān)技術(shù)和產(chǎn)品的布局。

寫在最后

作為涉及光子器件、集成電路、封裝、建模仿真等方方面面的跨學科技術(shù)領(lǐng)域,CPO技術(shù)體現(xiàn)了光電融合帶來的改變,而且給數(shù)據(jù)傳輸帶來改變無疑是顛覆性的。雖然很長一點時間可能只有大型數(shù)據(jù)中心才能看到CPO的應用,但隨著大算力高帶寬需求的進一步擴張,CPO光電共封技術(shù)已經(jīng)成為新戰(zhàn)場。

可以看到在CPO耕耘的廠商普遍認為2025年會是一個關(guān)鍵節(jié)點,這也是交換速率達到102.4Tbps的節(jié)點,到時可插拔模塊的弊端將進一步放大。雖然CPO應用可能到來的會有些緩慢,但是光電共封裝毫無疑問實現(xiàn)高速率高帶寬低功耗網(wǎng)絡(luò)的必經(jīng)之路。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

光電

+關(guān)注

關(guān)注

8文章

841瀏覽量

83103 -

數(shù)據(jù)中心

+關(guān)注

關(guān)注

18文章

5651瀏覽量

75025 -

CPO

+關(guān)注

關(guān)注

0文章

47瀏覽量

702 -

先進封裝

+關(guān)注

關(guān)注

2文章

533瀏覽量

1027

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

AOC光纖跳線:高速數(shù)據(jù)傳輸的新引擎

的網(wǎng)絡(luò)連接。AOC(Active Optical Cable,有源光纜)光纖跳線作為一種新興的高速數(shù)據(jù)傳輸解決方案,正逐漸成為推動各行業(yè)數(shù)字化發(fā)展的新引擎。 AOC光纖跳線的原理與構(gòu)成 AOC光纖跳線是一種將光電子器件集成在光纜兩端的特殊光纜。它主

從可插拔模塊到光電共封裝技術(shù)的演進

人工智能、云計算和高性能計算的快速發(fā)展對現(xiàn)代數(shù)據(jù)中心的數(shù)據(jù)傳輸帶寬和能源效率提出了更高的要求。傳統(tǒng)的可插拔光學模塊雖然在維護和升級方面具有便利性,但隨著網(wǎng)絡(luò)交換機容量超過12.8太比特每秒,這些模塊

借助CXL和壓縮技術(shù)實現(xiàn)高效數(shù)據(jù)傳輸

AI、科學計算、海量內(nèi)存處理……這些硬核工作負載正在不斷挑戰(zhàn)系統(tǒng)極限。而 FPGA 異軍突起,成為了實現(xiàn)高效數(shù)據(jù)傳輸的“關(guān)鍵推手”。想知道怎么在不改變整體架構(gòu)的前提下,讓帶寬和能效實現(xiàn)“雙飛躍”?答案就藏在壓縮 IP 與基于 CXL(Compute Express Lin

CPO技術(shù)加速未來數(shù)據(jù)中心網(wǎng)絡(luò)發(fā)展

生成式 AI 的快速普及正在推動數(shù)據(jù)中心網(wǎng)絡(luò)需求的指數(shù)級增長。光電一體化封裝(CPO)技術(shù)以其高帶寬密度、低功耗和可靠性優(yōu)勢,成為滿足 AI 時代網(wǎng)絡(luò)性能需求的關(guān)鍵方案。

CPO技術(shù):毫米級傳輸、超50%降耗與1.6Tbps突破

電子發(fā)燒友網(wǎng)報道(文/李彎彎)在人工智能算力需求爆發(fā)與數(shù)據(jù)中心能效要求提升的雙重驅(qū)動下,光電共封裝(CPO)技術(shù)正從實驗室走向產(chǎn)業(yè)化前沿。這

光電共封裝技術(shù)的實現(xiàn)方案

數(shù)據(jù)中心網(wǎng)絡(luò)架構(gòu)正在經(jīng)歷向光電共封裝(CPO)交換機的根本性轉(zhuǎn)變,這種轉(zhuǎn)變主要由其顯著的功耗效率優(yōu)勢所驅(qū)動。在OFC 2025展會上,這一趨勢變得極為明顯,從Jensen Huang在

Broadcom光電共封裝技術(shù)解析

光電共封裝(Co-Packaged Optics,CPO)代表了光互連技術(shù)的新發(fā)展方向,這種技術(shù)將光學器件直接集成到電子線路的同一封裝內(nèi)。傳

燧原科技聯(lián)合曦智科技推出國內(nèi)首款xPU-CPO光電共封芯片

在今年的2025世界人工智能大會上,燧原科技聯(lián)合曦智科技推出了國內(nèi)首款xPU-CPO光電共封芯片,為本土的數(shù)據(jù)中心光互連技術(shù)樹立了一個新標桿

智慧光迅重磅推出光電融合新品

光電融合組網(wǎng)憑借技術(shù)顛覆性、政策紅利和市場需求三重驅(qū)動,正從“潛力賽道”加速邁向“主流選擇”成為網(wǎng)絡(luò)建設(shè)的新風口。智慧光迅一直致力于賦能泛住宿、安防、企業(yè)園區(qū)、教育行業(yè),為弱電集成商、運營商、生態(tài)合作伙伴提供多(利潤)、快(服務)、好(質(zhì)量)、省(降本增效)、全(全場景)

CPO光電共封裝如何破解數(shù)據(jù)中心“功耗-帶寬”困局?

電子發(fā)燒友網(wǎng)報道(文/李彎彎)CPO(Co-Packaged Optics,光電共封裝)是一種將光學器件與電子芯片直接集成在同一封裝內(nèi)的技術(shù),旨在解決傳統(tǒng)

SPI數(shù)據(jù)傳輸緩慢問題求解

我遇到了 SPI 數(shù)據(jù)傳輸速率問題。 盡管將 SPI 時鐘頻率設(shè)置為 20 MHz,但我只獲得了 2 Kbps 的數(shù)據(jù)傳輸速率。 我正在以 115200 的波特率通過 UART 監(jiān)控數(shù)據(jù)。

我正在 cyfxusbspidmamo

發(fā)表于 05-15 08:29

CPO光電共封即將放量,用光電融合技術(shù)解決海量數(shù)據(jù)傳輸

CPO光電共封即將放量,用光電融合技術(shù)解決海量數(shù)據(jù)傳輸

評論