上期我們介紹了什么是寄生電感,以及寄生電感對輸入端的影響,本期,我們來聊一下寄生電感對Buck電路中開關管的影響。

寄生電感對開關管的影響

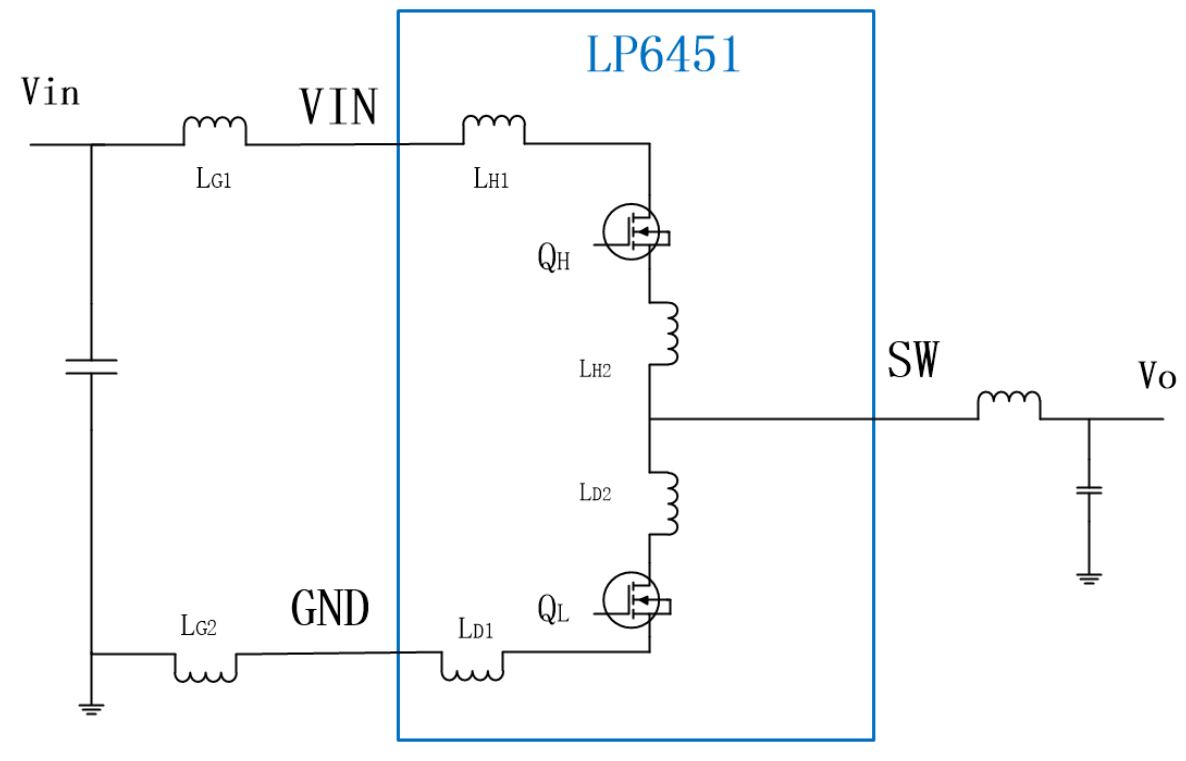

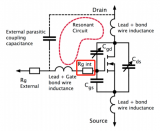

LP6451內部集成了兩個MOS管,構成同步Buck電路中所必須的上管和下管,同樣由于PCB上的走線,Die與芯片引腳之間Bonding線都會帶來寄生電感,我們在分析LP6451的MOS管應力時,就需要把這些寄生電感都考慮進來,而圖1就是LP6451功率部分的實際等效電路圖。

圖1:LP6451實際應用等效圖

其中,QH和QL分別為LP6451內部集成的Buck電路的上管和下管,而LG1和LG2為輸入電容到芯片VIN和GND引腳之間的PCB走線所帶來的寄生電感,LH1和LD1為LP6451的Bonding線帶來的寄生電感,LH2和LD2則分別為上下管到引腳SW的寄生電感。在上下管開關切換的過程中,這些寄生電感所產生的感應電壓都會對LP6451內部的MOS管帶來額外的電壓應力。

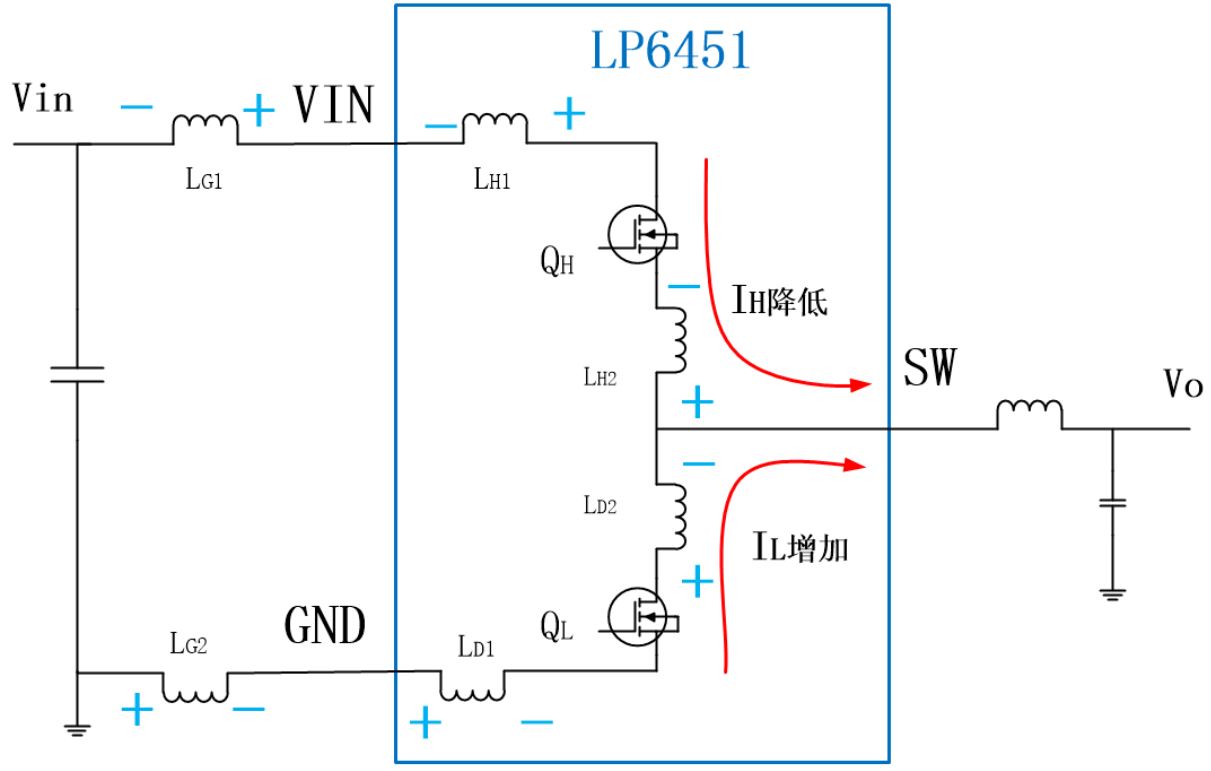

比如,當上管QH開始關斷,下管QL開始導通時,流經上管QH的電流IH逐漸減少,流經下管QL的電流IL逐漸增加,此時,在寄生電感LG2和LD1上會產生左高右低的感應電壓,寄生電感LD2上會產生下高上低的感應電壓,如圖7所示。此時,我們使用示波器探頭去測量LP6451的引腳SW的波形,探頭正端接LP6451的引腳SW,地線接輸入電容的地線,就會發現SW的最低電壓會比正常LD2體二極管導通時的電壓-0.7V還要更低。如果將輸入電容更加遠離LP6451,那么寄生電感LG2則會變得更大,產生的感應電壓也就越大,此時測試SW引腳的負壓值就會越大。如圖2所示,實測SW的電壓最低可以達到-4V左右。

圖2:下管開通時刻的感應電壓

同樣,當上管電流減小時,會使得寄生電感LG1和LH1產生左低右高的感應電壓,LH2產生上低下高的感應電壓,這些感應電壓連同輸入電壓Vin會共同加在上管QH的漏極和源極之間,使得上管QH實際承受的電壓要大于Buck電路的輸入電壓。如果這些寄生電感比較大的話,上管QH就會存在擊穿的風險。

下期我們將介紹寄生電感與哪些因素有關,以及我們該如何降低寄生電感對電路的影響。

文章來源:微源半導體

審核編輯 黃宇

-

芯片

+關注

關注

463文章

54007瀏覽量

465895 -

pcb

+關注

關注

4404文章

23877瀏覽量

424214 -

MOS管

+關注

關注

111文章

2786瀏覽量

76885 -

寄生電感

+關注

關注

1文章

166瀏覽量

15072

發布評論請先 登錄

基于SiC MOSFET和低寄生電感 PCB 層疊母排的 50kHz變頻器設計

PCB設計知識又增加了:聽都沒聽過的電容,濾波性能竟然這么好?

寄生電感致電流采樣失真:關鍵問題與解決辦法

信維高精度陶瓷電阻,精準調控電路參數

破局SiC高頻寄生電感難題,派恩杰推出嵌入式封裝方案

派恩杰PCB嵌入式功率模塊的性能優勢

一文帶你了解線路寄生電感對開關器件的影響及解決方案

電源功率器件篇:線路寄生電感對開關器件的影響

高壓單端探頭設計時,地線處理方法的研究

疊層母排在IGBT變流器中的應用(1)

SiC MOSFET 開關模塊RC緩沖吸收電路的參數優化設計

用NPN和PNP三極管搭建一個MOSFET驅動電路,1200字講透它!

一文詳解寄生參數對柵極震蕩的影響

寄生電感的影響

寄生電感的影響

評論