本文轉載自: 信號完整性微信公眾號

編者注:在高速PCB設計時,經常會遇到布線角度(圓弧、45°和直角)的問題,之前我們也有聊過這個問題。但是這一期我們更進一步地用仿真做了一些研究,研究的結果可能有的會出乎一些工程師的意料。讓Mosman帶你耐心地閱讀全文,希望會有所收獲!

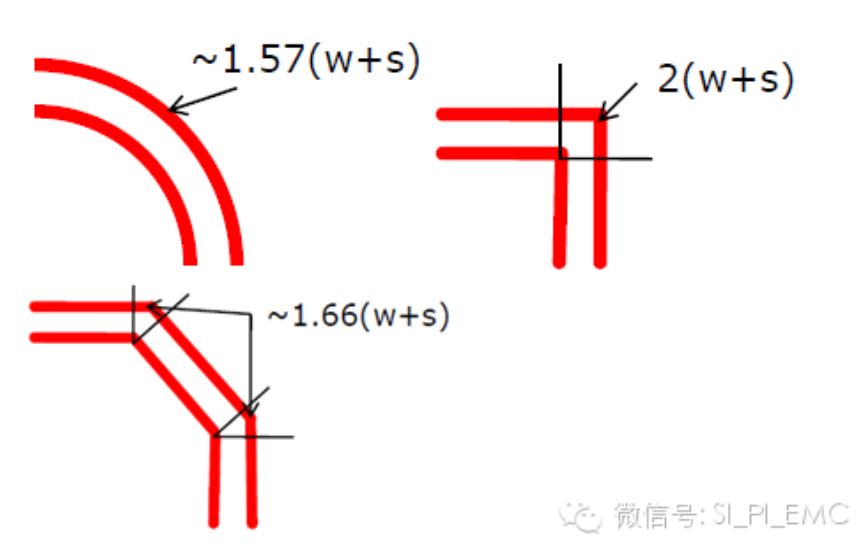

問題:在PCB布線中有三種常用的拐彎方式:直角、45度,圓弧(如下圖)。哪一種拐彎方式最好呢?這個問題根據經驗比較容易回答,大多數會是圓弧>雙45度>直角,但是經驗性的東西不能定性而且總是在一定范圍內有效,只有通過全波電磁場求解器才能準確地研究這個問題。單端走線拐彎不涉及到模態轉化,因此以差分線為例。

差分線拐彎時內側和外側的走線長度不一樣,信號的延遲也不一樣,這是信號中部分差模成分轉化為共模成分的主要原因,然而拐彎處造成的阻抗不連續性也不能忽略,2.5D的電磁場求解器沒有辦法計算這部分效應。

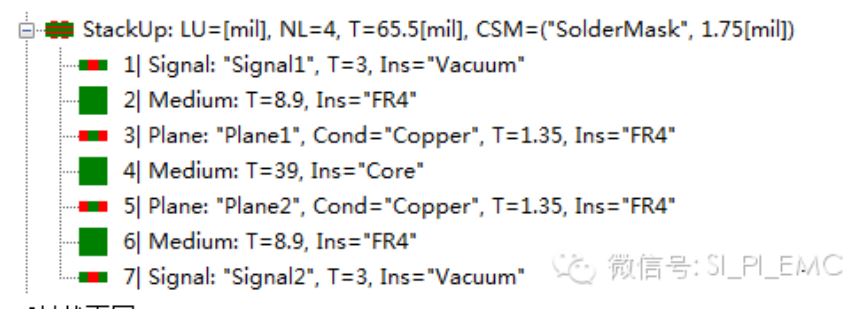

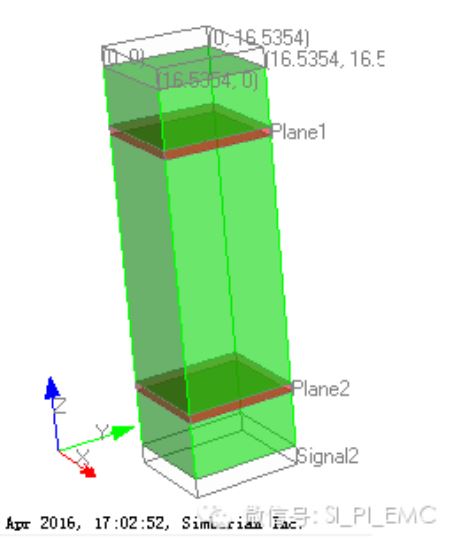

一、疊層

為了研究以上結構,在3D電磁場求解器Simbeor中創建所需要的模型。選擇常用的4層板,材料參數:阻焊DK=3.3,LT=0.02,PP板Dk=3.3,LT=0.02,core內芯DK=4.7,LT=0.02疊層設置如下

板材截面圖

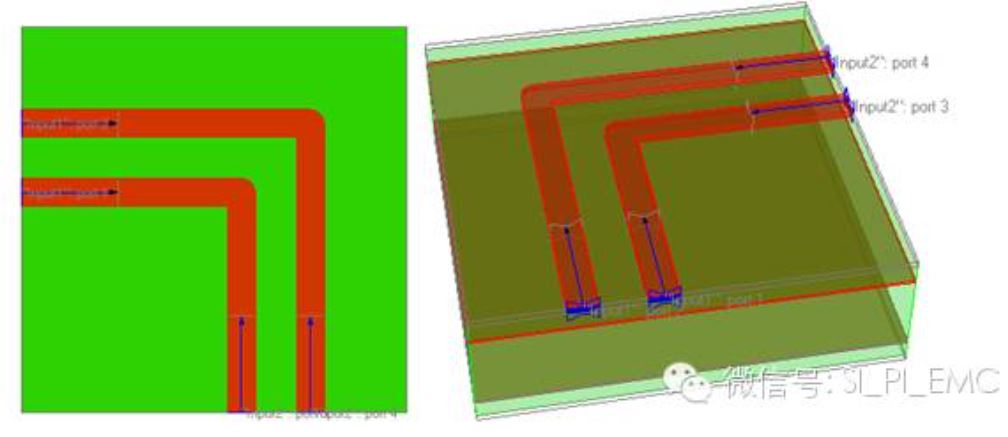

二、結構

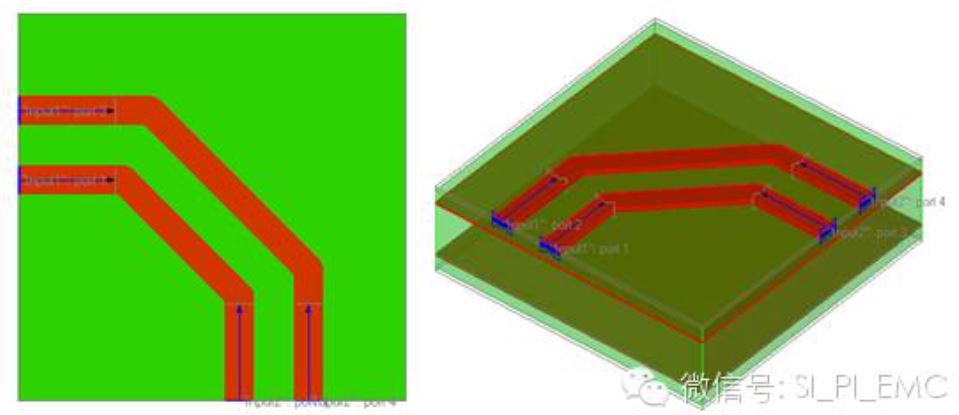

1、90度拐角:

微帶線線寬15mil,線距22mil,兩根線的長度差是209.5mil

2、45度拐角

微帶線線寬15mil,線距22mil,兩根線的長度差63mil

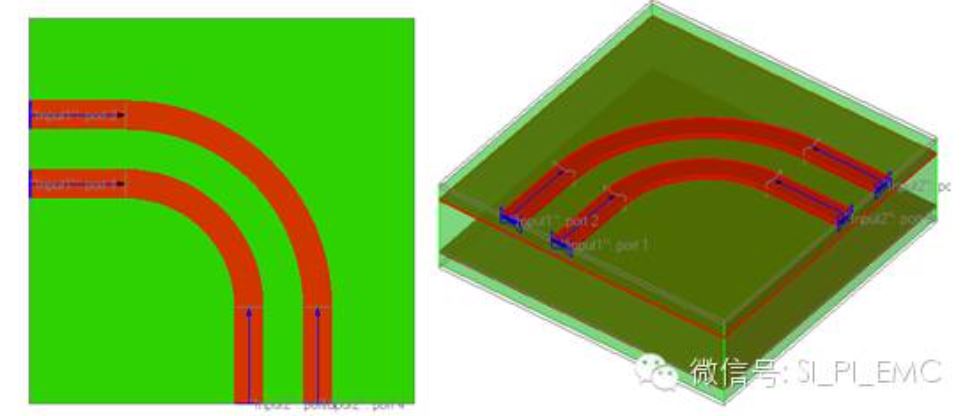

3、圓弧拐角

微帶線線寬15mil,線距22mil,兩根線的長度差59mil

三、仿真出結果

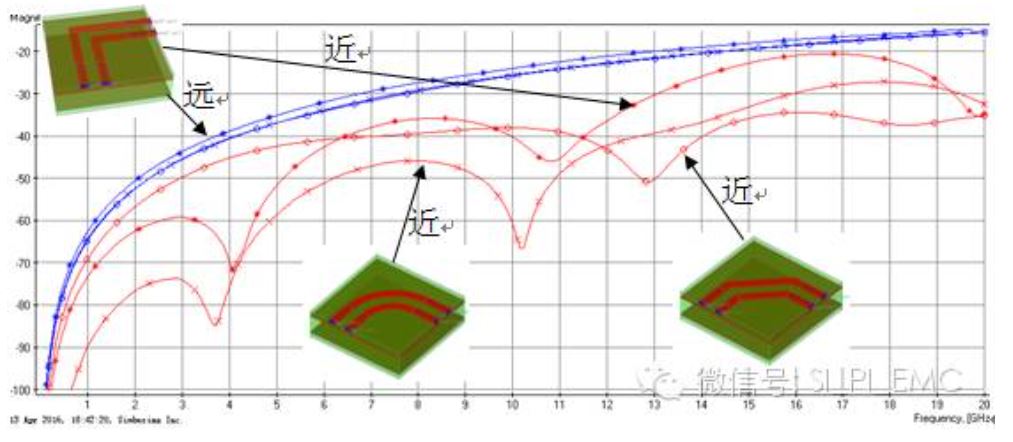

1、差模反射S[D1,D1]

2、差模插損S[D1,D2]

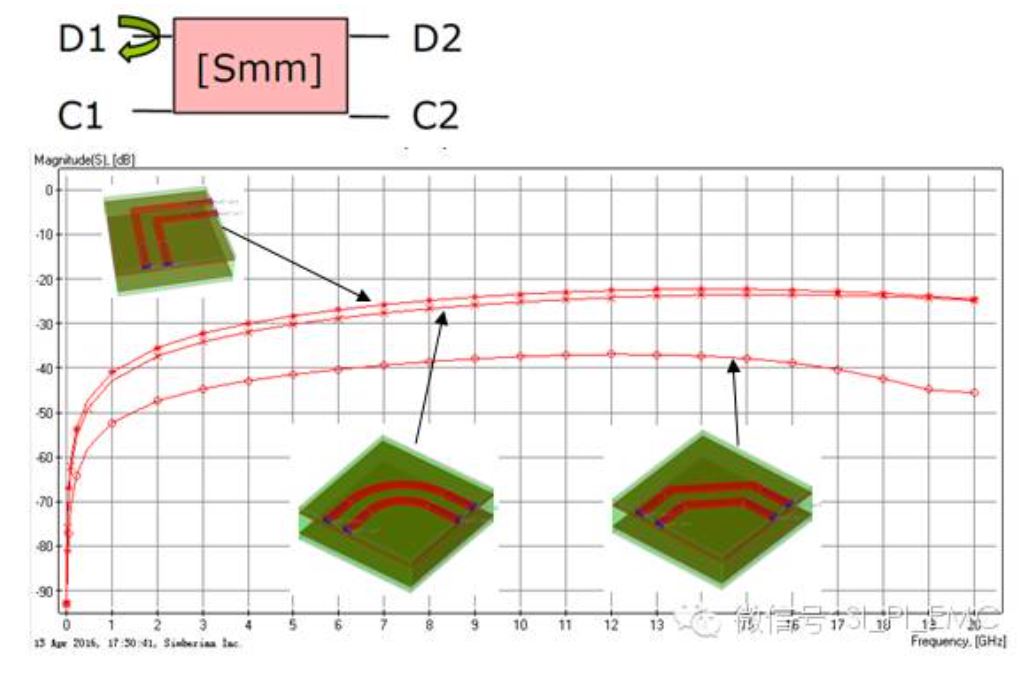

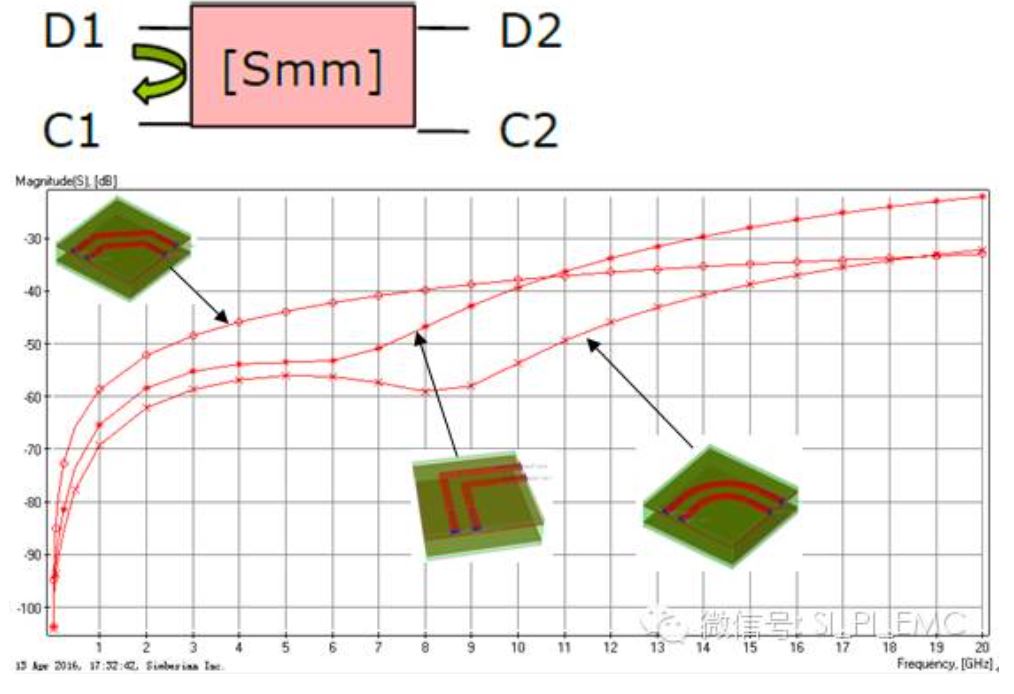

3、近端模態轉換S[D1,C1]

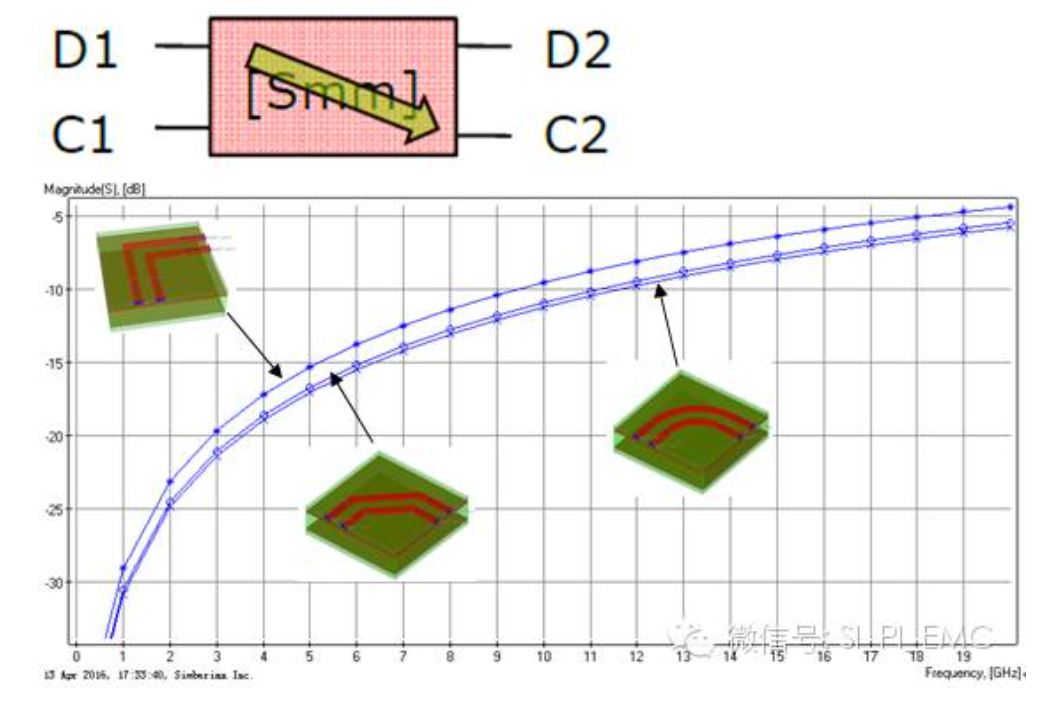

4、遠端模態轉換S[D1,C2]

四、結論:

1、差模回損反而是45度拐角最好(不是圓弧),這可能在很多人意料之外;

2、差模插損圓角拐彎最好,45度也差不到哪里去,90度最差,設計的時候盡量避免90度,主要;

3、近端模態轉換,這個時候圓角最好,出人意料的是在10GHz之前的頻段,直角居然比45度要好;

4、遠端模態轉換,這個時候直角最差,比另外兩種高出1.4dB,圓弧和45度很相近。但是不管是哪一種拐彎方式,到了20GHz的時候,遠端模態轉換達到了-5dB,在28Gbps/56Gbps的高速串行總線中要對這種拐彎進行補償。

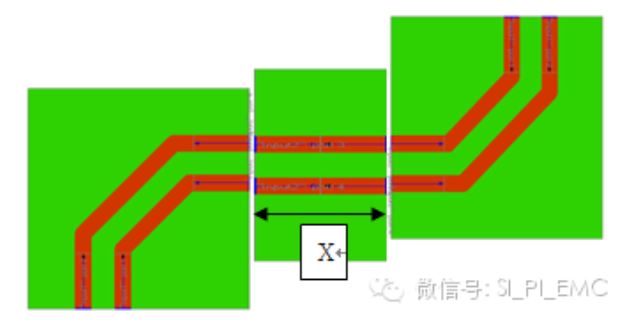

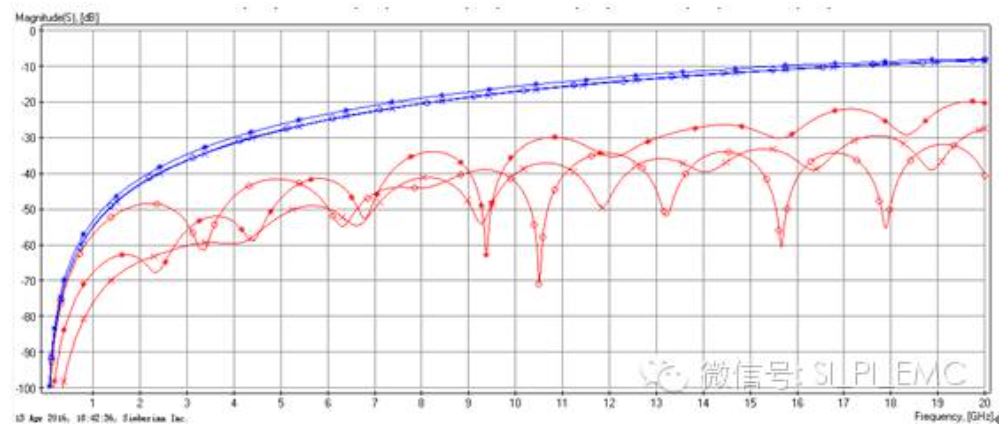

五、補償拐角帶來的遠端模態轉換的一種方式就是用另外一個轉向相反的拐彎來使得走線成一個中心對稱的形式。如下圖其中x=250mil,另外兩種拐角也做同樣的補償:

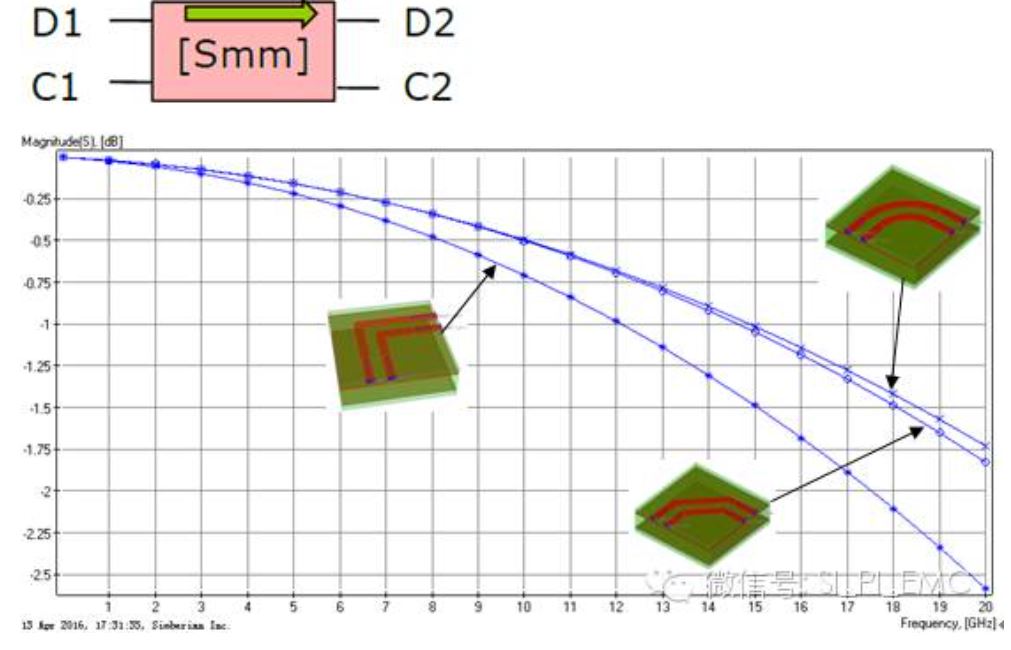

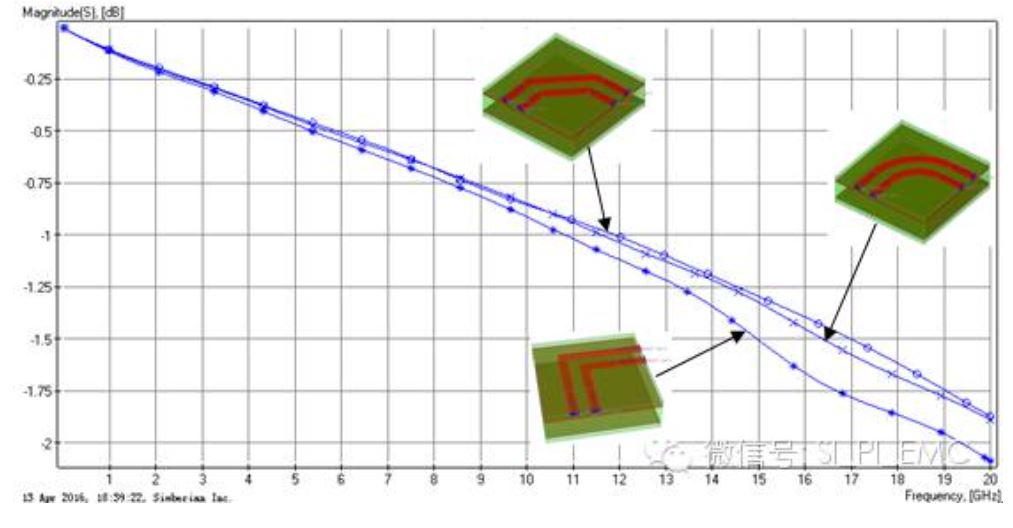

1、差模插損S[D1,D2]

2、模態轉換

以上總結:1、補償之后的差模插損45度拐角在所有頻段都要略微比圓弧的好,90度最差;

2、補償之后的遠端模態轉換達到了-16dB@20GHz,直角只比另外兩種稍微差一點。但是無論如何補償都不能降到很低以下了。這主要是因為一旦造成模態轉換,共模信號的傳播速度比差模要慢,相位可以補償,但是傳播速度用簡單的走線幾何結構補償不了。如果兩種模態的信號傳播速度相同(內部strip line),那么情況要好很多了。

如果讓x=1000mil呢?

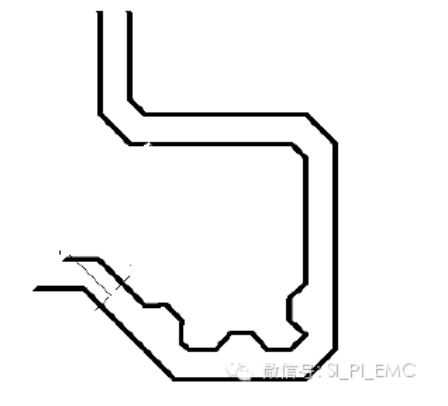

這個時候遠端模態轉換突然達到了-8dB,這已經很大了。說明如果因為走線造成差分線失配,必須盡快補償回來,x值越小,補償的效果越好。但是有的時候因為走線方向原因,只有一個拐角,這個時候可以做如下圖的處理,在內側繞蛇形線,快速將適配的補償回來。

審核編輯 黃宇

-

布線

+關注

關注

9文章

821瀏覽量

86135 -

高速信號

+關注

關注

1文章

267瀏覽量

18505

發布評論請先 登錄

如何判斷光柵尺是否需要清潔?

高頻PCB布線“避坑指南”:4大核心技巧讓信號完整性提升90%

PCB布局布線的相關基本原理和設計技巧

【書籍評測活動NO.65】ADS仿真實戰,破解高速設計信號瓶頸:《高速數字設計(基礎篇)》

Allegro Skill布線功能之刪除Dangling介紹

高速PCB設計挑戰 Allegro Skill布線功能 自動創建match_group

Allegro Skill布線功能-添加差分過孔禁布區

高速信號是否需要走圓弧布線

高速信號是否需要走圓弧布線

評論