作者:

柯春山,英飛凌電源與傳感系統事業部 高級主任工程師

在日常的電源設計中,半導體開關器件的雪崩能力、VDS電壓降額設計是工程師不得不面對的問題,本文旨在分析半導體器件擊穿原理、失效機制,以及在設計應用中注意事項。

一、半導體器件擊穿原理

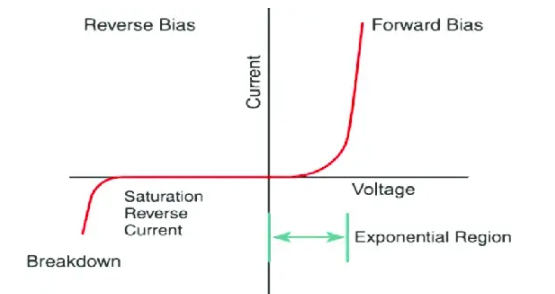

PN結I-V曲線如圖[1]所示:

PN結正向導通,反向截止;

反向電壓超過一定限值VBR,器件發生電擊穿;

正向導通時,電流超過一定限值(圖示綠色區域之外),器件發生熱燒毀。

圖[1]:PN結I-V曲線

PN結的擊穿原理分為:電擊穿和熱擊穿(二次擊穿)。

1)電擊穿

電擊穿:指強電場導致器件的擊穿,過程通常是可逆的。當電壓消失,器件電學特性恢復。電擊穿又分為:

a)雪崩倍增效應

雪崩倍增效應:(通常指電壓>6V時發生,)原理如下:

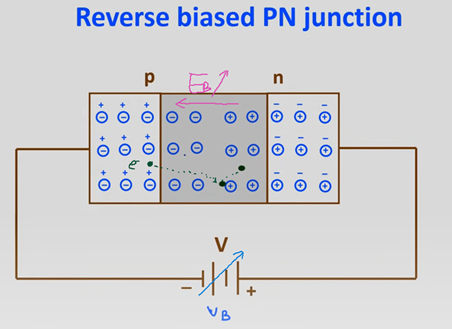

圖[2]:PN結反偏示意圖

如圖[2]所示:在PN結兩端加反向電壓,隨著反向電壓增加,PN結耗盡區反向電場增加,耗盡區中電子(或者空穴)從電場中獲得的能量增加。當電子(或者空穴)與晶格發生碰撞時傳遞給晶格的能量高于禁帶寬度能量(Eg),迫使被碰撞的價帶電子躍遷到導帶,從而產生一堆新的電子空穴對,該過程叫做碰撞電離;課本里把一個自由電子(或者空穴)在單位距離內通過碰撞電離產生的新的電子空穴對的數目稱為電子(或者空穴)的碰撞電離率,表示為αin(or αip)。

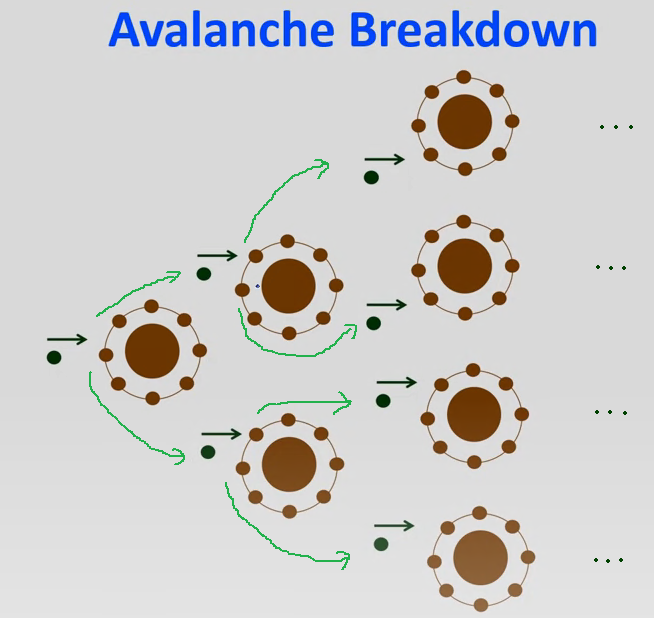

當耗盡區電場增加到一定程度,碰撞電離激發出的新電子-空穴對,即“二次載流子”,又可能繼續產生新的載流子,這個過程將不斷進行下去,稱為雪崩倍增。如果由于雪崩倍增效應導致流出PN結的電流趨于無窮大,則發生了所謂的雪崩擊穿,該過程簡單示意如圖[3]所示。

圖[3]:雪崩擊穿示意圖

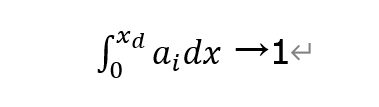

發生雪崩擊穿的條件是:

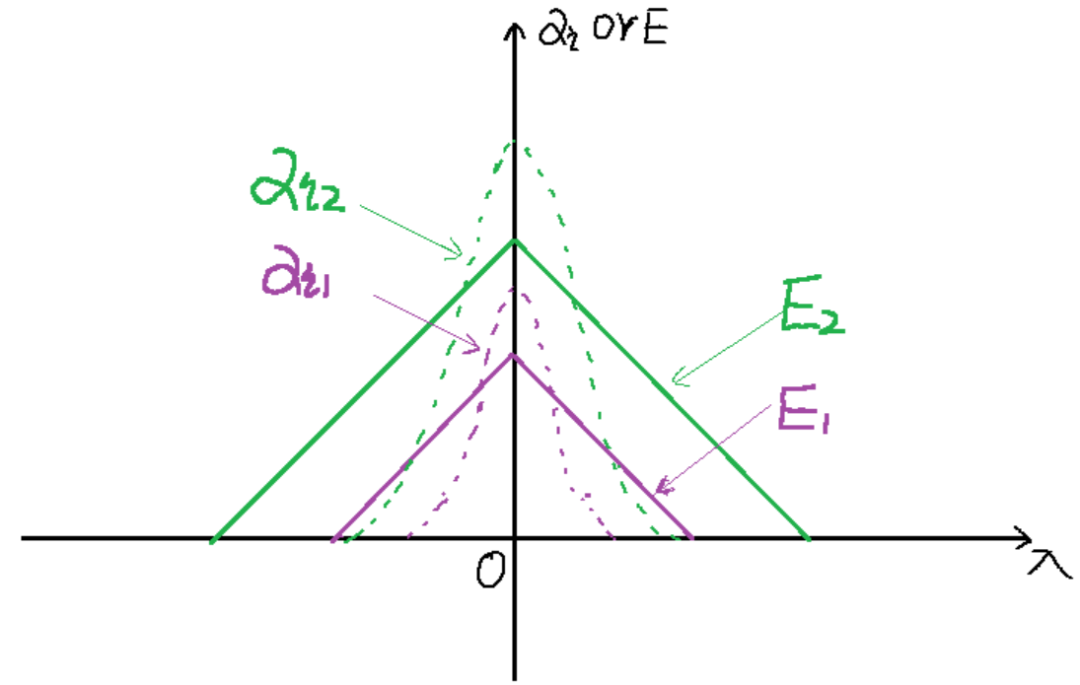

其物理意義是碰撞電離率在整個耗盡區積分趨于1。由于αi隨電場的變化強相關(如圖[4]所示),因此可以近似的認為當耗盡區最大電場EMAX達到某臨界電場Ec時,即發生雪崩擊穿。Ec與結的形式和摻雜濃度有一定關聯,硅PN結典型值為Ec = 2×105 V/cm。

圖[4]:電場的強相關函數圖

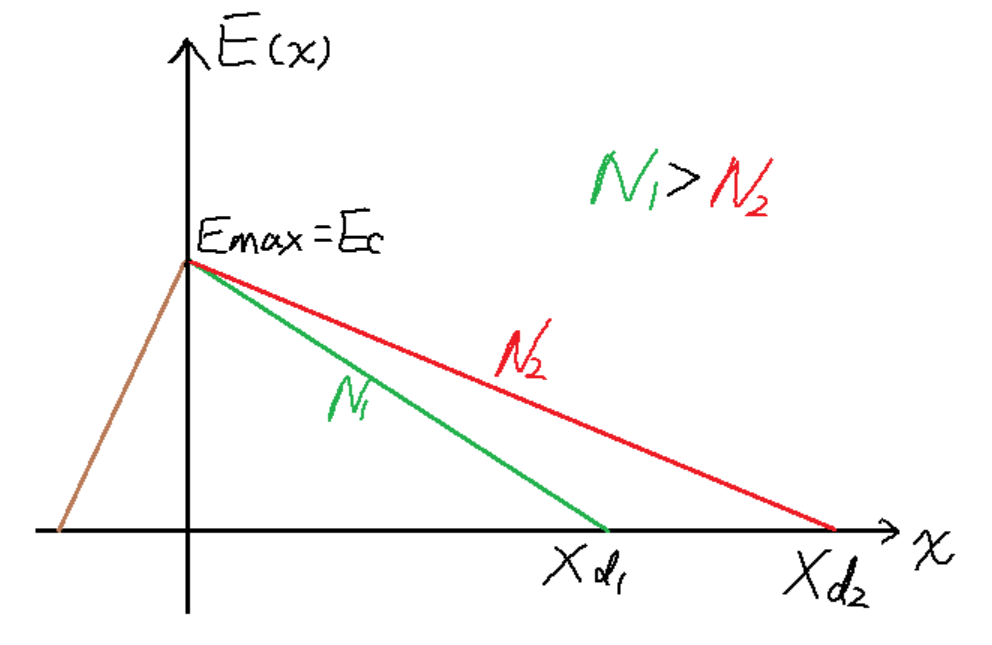

為了更好地理解PN結電場強度Ec隨耗盡區XD的關系,我們在這里簡單討論下泊松方程:在一維情況下(PN結/BJT)泊松方程的表達形式為:

等式右邊第一項“q”為電荷量,介電常數“εs”為電通量密度與電場的映射關系,括號內表示自由離子的加和。從直觀來看,該式反映電場(或者電通量密度,兩者從某種角度上可以理解為反映著同一種東西)的源是電荷,如果是記公式:泊松方程表示的是,單位體積內對電通量密度(電位移)求散度,結果為體積內的電荷。除了從電磁學理論出發的分析,該式從數學上也可以看成是:電場與位置的函數關系。通過解泊松方程,便可以得到隨著位置變化時,電場、電勢的變化情況。

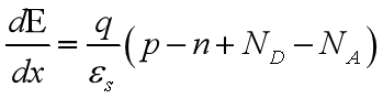

接下來我們通過舉例來看擊穿電壓VB與哪些因素相關:圖[5]所示為兩種摻雜濃度材料的Ec VS Xd曲線關系(其中,N1>N2)。

圖[5]不同摻雜濃度Ec VS Xd曲線關系

分析該圖可知:

1. 禁帶寬度Eg越大,則擊穿電壓VB越高;比如Si (Eg=1.12 eV) VS SiC (Eg=3.23 eV)

2. 摻雜濃度越低,VB越高;

3. 擊穿電壓主要取決于低摻雜一側,該側的雜質濃度越低,則VB越高。

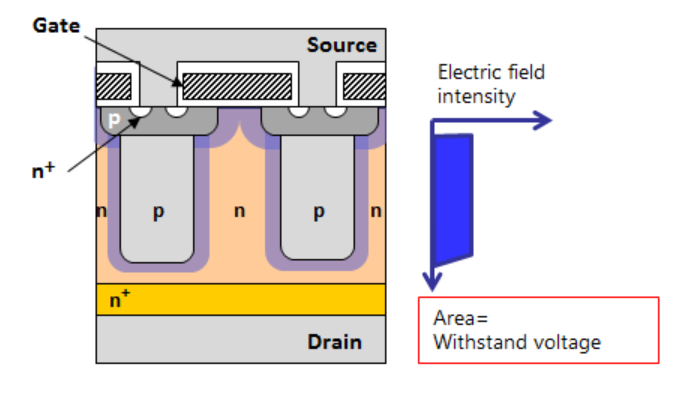

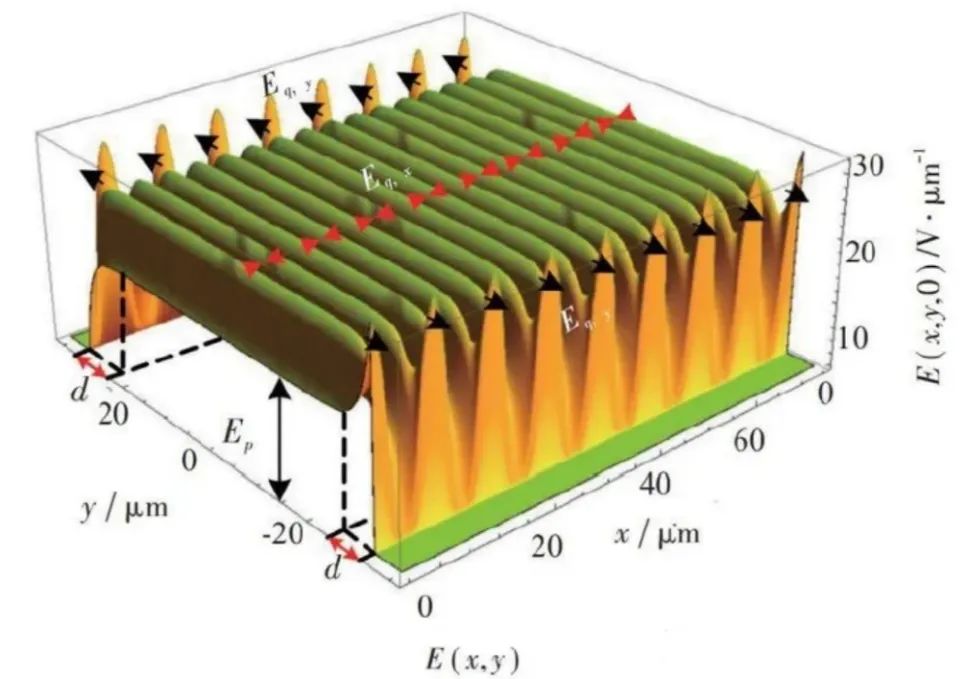

除了上述方法可以提高擊穿電壓VB,還可以通過增加電場維度,改變電場強度分布(如圖[6]、圖[7]所示):比如英飛凌的CoolMOSTM系列產品,通過在N-耗盡區摻入P柱結構(引入橫向電場分布),大幅提高VB。這里不再贅述其機理,感興趣的讀者可在英飛凌官網查閱相關文獻資料。

圖[6]SJ MOSFET剖面示意圖

圖[7]SJ MOSFET內部電場仿真示意圖

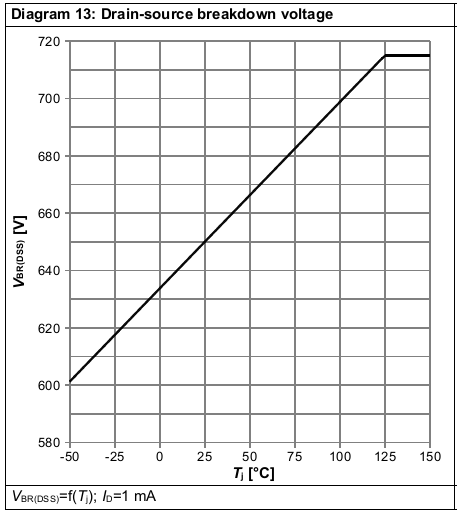

綜上所述,PN結的雪崩擊穿電壓VBR還與PN結結溫(Tj)呈現正相關性(如圖[8]):

圖[8]:IPL65R065CFD7 VBR(DSS) VS Tj

其主要原因是:隨著溫度升高,晶格振動加劇,價帶電子躍遷到導帶需要的能量Eg更高,因此需要更強的電場。

b)隧道效應

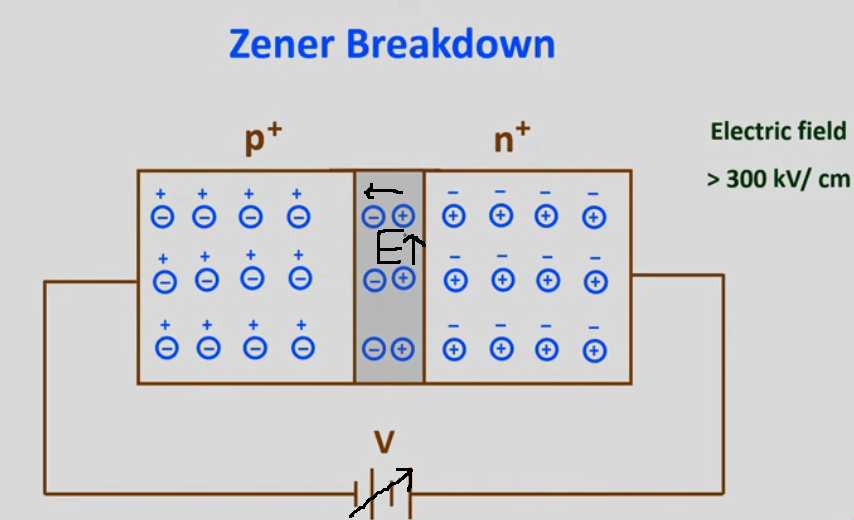

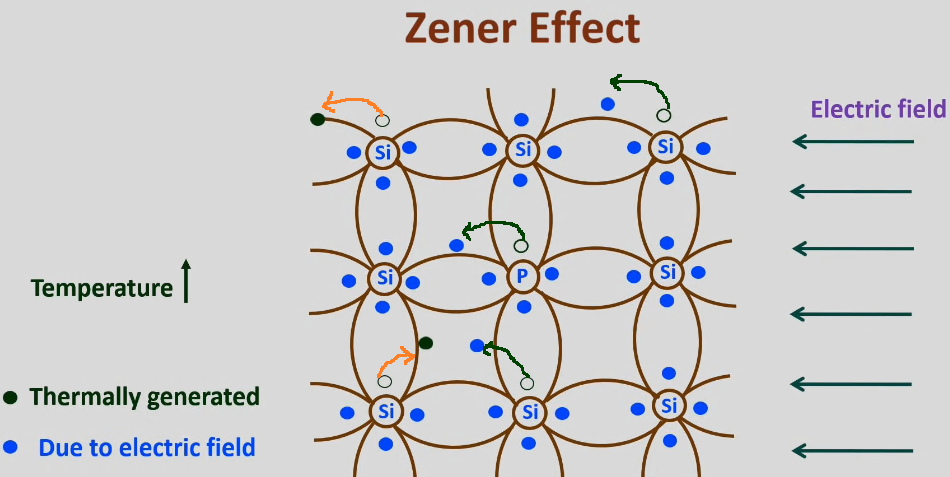

隧道效應又稱為齊納擊穿、隧道穿通,(一般發生在擊穿電壓VB<4V時,)其原理如下:

圖[9] P+N+結電壓反偏示意圖

將兩塊重摻雜的P+、N+半導體材料結合在一起,由于耗盡區兩側P+ 、N+載流子濃度更高,因此形成耗盡區寬度,較普通PN結更薄,耗盡區帶電離子濃度更高,內建電場Eb更強。當在PN結兩端加反向偏壓如圖[9]所示,該電壓產生的電場與內建電場同向疊加,當耗盡區電場強度>300kV/cm時,電子空穴對在電場力的作用下掙脫原子核束縛,自由的穿過耗盡區,形成電流。顧名思義:叫做隧穿效應,該過程微觀過程如圖[10]所示。當PN結兩端反向電壓進一步增加時,流過PN結電流增加,電壓基本保持不變。齊納二極管(穩壓二極管)即是利用該效應制作的一種穩壓元器件。

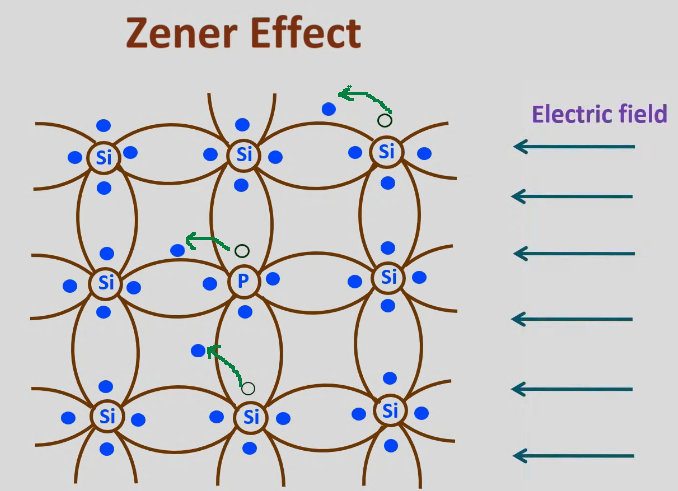

圖[10] 隧穿效應示意圖

由于隧穿效應的導電離子是來自于掙脫原子核束縛的電子(或者空穴),因此,隨著溫度的升高,PN結內部產生熱電子濃度增加,進而導致擊穿電壓VB降低,使得宏觀上擊穿電壓VB呈現負溫度特性。該過程微觀示意如圖[11]。

圖[11] 隧穿效應VS溫度示意圖

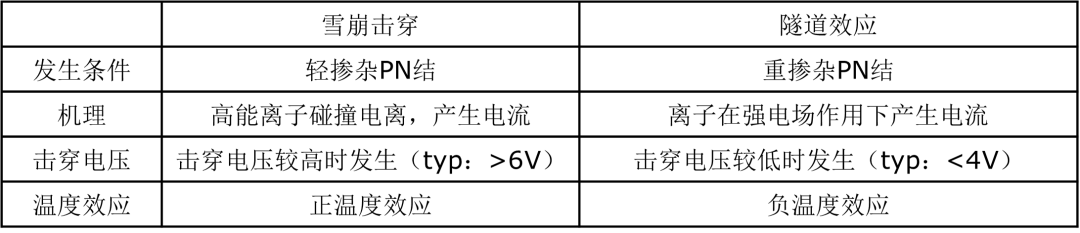

在這里簡單的對兩種電壓擊穿做對比總結以方便讀者記憶:

2)熱擊穿(二次擊穿)

熱擊穿(二次擊穿)指器件由于過電壓、過電流導致的損壞,結果不可逆。通常情況下是先發生了電擊穿,產生的高壓大電流沒有得到及時控制,進一步導致過熱使得器件發生燒毀。

二、設計應用注意事項

通過以上分析,我們可以得出結論:對于硅材料的半導體功率器件(碳化硅材料器件由于其原理、結構與硅材料相似,因此有著相似的物理規律,這里不再做分析,氮化鎵器件由于其器件結構與傳統硅差別較大,因此不具備類似的規律,后續文章可以涉及,敬請關注),在驅動電壓Vgs可控的情況下,主要失效模式兩種:

一種是:過電壓應力導致器件發生雪崩,雪崩過程本身是可逆的,但如果由于雪崩行為沒有被及時控制,導致器件出現過熱,進一步導致器件封裝燒毀、bonding材料或者結構毀壞、甚至芯片半導體結構損壞,該過程不可逆。

第二種是:過電流應力導致器件溫升超過其極限值,進一步導致器件封裝燒毀、bonding材料或者結構損壞、甚至芯片半導體結構破壞,該過程亦不可逆。

因此,我們在設計使用半導體功率器件電路時,必須嚴格的遵照相關的標準(例如IPC9592B-2012),規范化降額設計,以保證產品在整個生命周期內,半導體器件可以運行在規格書的范圍內,以顯著降低產品的失效率。更多的關于半導體器件雪崩設計應用指南請參考英飛凌應用筆記:AN_201611_PL11_002,本文不再贅述。

后記

隨著半導體產業競爭趨于白熱化,在半導體器件設計中,一個不爭的事實:對于相同的技術下,Rds(on)越小,芯片尺寸越大,器件熱阻越小,抗雪崩能力越強。但是對于半導體器件來講,并不是芯片尺寸越大越好,更大的尺寸意味著更大的寄生參數,更大的開關損耗,因此限制了電源朝著高頻高密的方向發展以進一步降低系統成本。因此,在設計器件過程中,需要綜合性的權衡各項參數,以設計出綜合能力更全面的產品。英飛凌公司作為全球功率器件的領頭羊,一直致力于設計更全面的產品以完成其“低碳化”的使命!

參考文獻:

[1]. 功率器件發展趨勢及前緣介紹 – 鄭敏,電子科技大學

[2]. Avalanche Breakdown and Zener Breakdown Effect Explained – allaboutelectronics, YouTube

[3]. AN-1005 - 功率MOSFET 雪崩設計指南–Tim McDonald、Marco Soldano、Anthony Murray、Teodor Avram,國際整流器

[4]. AN_201611_PL11_002 – 雪崩相關重要事實,Infineon AG Technologies

[5]. 微納電子與智能制造– 張波,章文通,蒲松,喬明,李肇基

[6]. 微電子器件– 陳星弼,陳勇,劉繼芝,任敏, 北京:電子工業出版社

審核編輯 黃宇

-

電源設計

+關注

關注

31文章

1824瀏覽量

69690 -

半導體器件

+關注

關注

12文章

807瀏覽量

34124

發布評論請先 登錄

使用熱電偶進行溫度測量時的注意事項

驅動板PCB布線的注意事項

是德科技Keysight B1500A 半導體器件參數分析儀/半導體表征系統主機

半導體制造防震基座安裝 RC 銑孔操作注意事項-江蘇泊蘇系統集成有限公司

別讓這些細節毀了PCBA!焊接注意事項清單

功率半導體器件——理論及應用

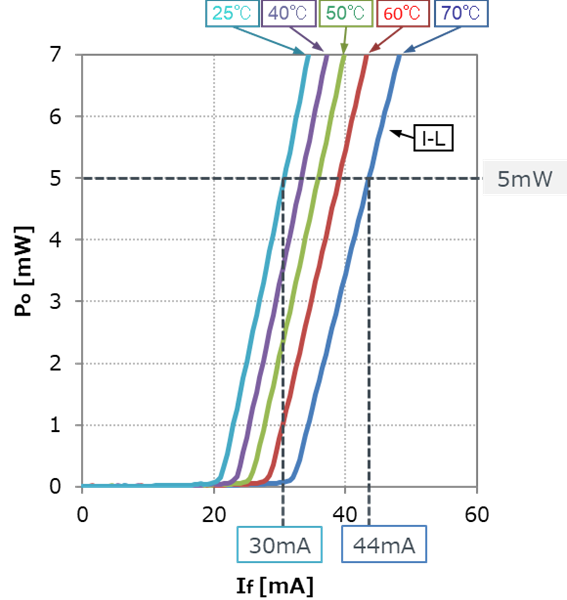

激光二極管的基本特性和使用注意事項

半導體器件擊穿機理分析及設計注意事項

半導體器件擊穿機理分析及設計注意事項

評論