一、SSC概述

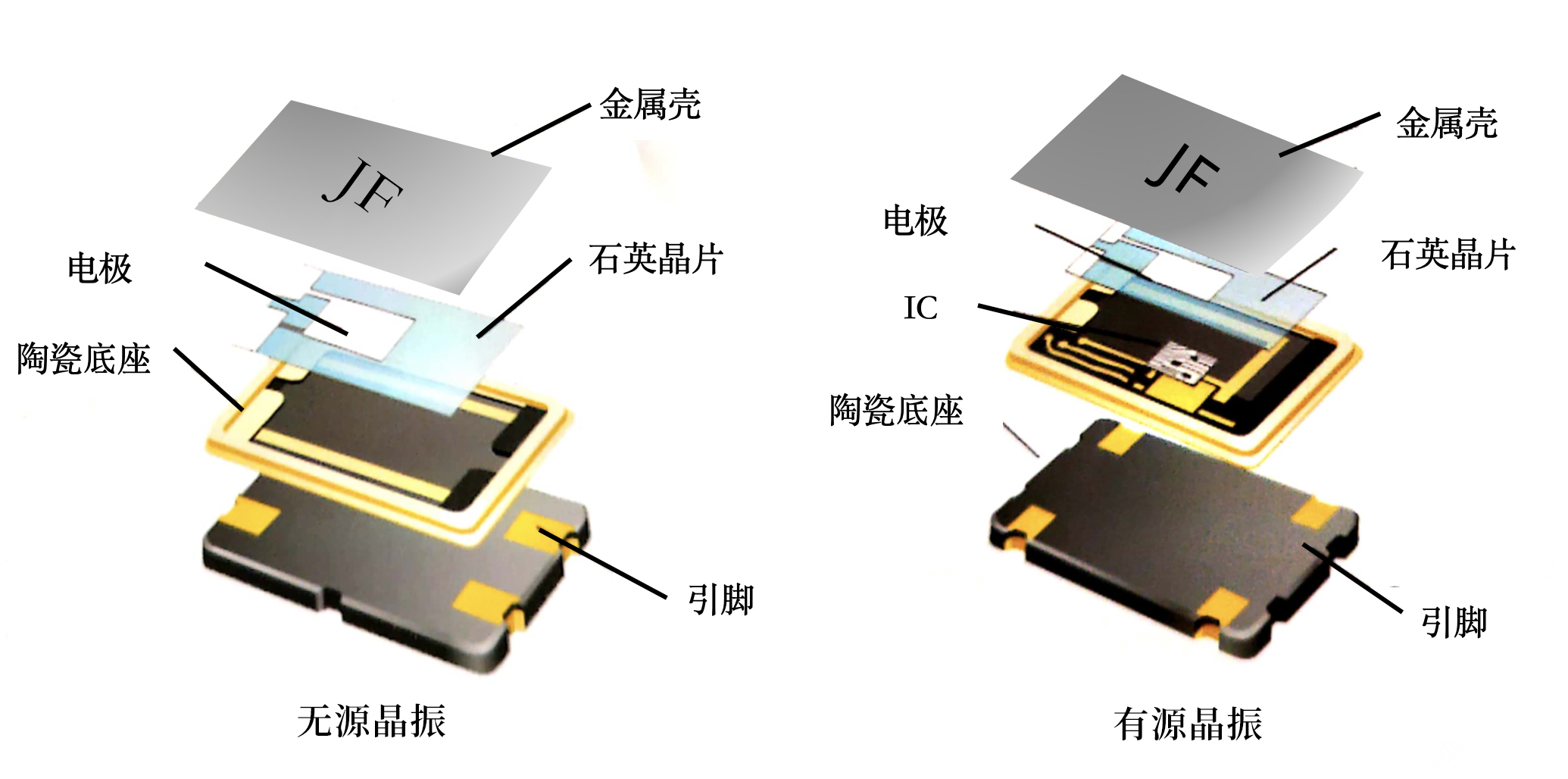

1)SSC英文全稱:Spread Spectrum Clocking,中文名擴頻時鐘。

2)SSC目的:為了降低與信號基頻相關(包含信號本身以及諧波)的EMI(Electromagnetic interference)輻射,以減少系統之間的干擾。

3)SSC手段:通過一個較低的頻率來調制信號,使得信號的頻譜在基頻附近被擴展,窄帶的周期信號被擴展為寬帶信號,且信號基頻和諧波的峰值能量顯著降低。

4)SSC缺點:擴頻信號比未擴頻信號增加了抖動。

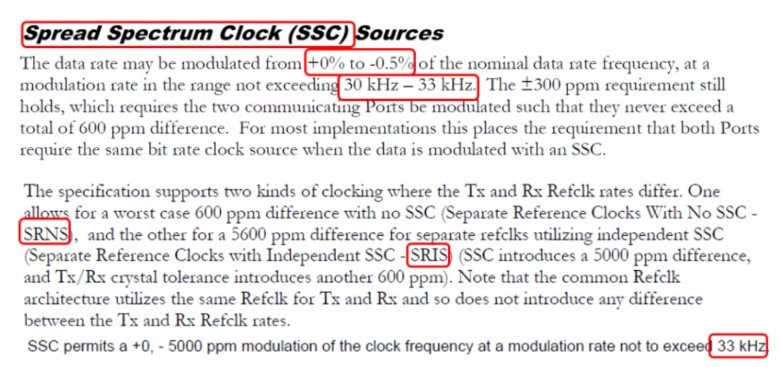

二、SSC擴頻時鐘主要參數

1)擴展率δ:頻率擴展變化的范圍Δf與原CLK頻率(fc)的比值,一方面,頻率變化范圍越大,其能量分布就越寬,EMI抑制能力會越強,但因為系統對于輸入時鐘有一定的頻率范圍要求,因此擴展率不宜過大,否則會使得實際時鐘超過系統額定頻率,一般δ在0.5%~2.5%之間;

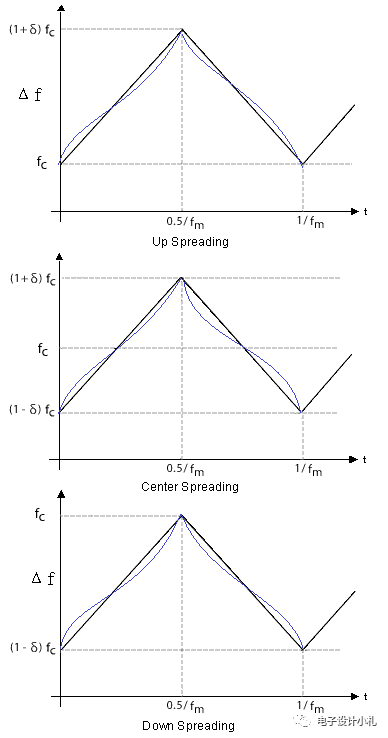

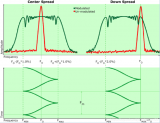

2)擴頻類型:向下擴頻、中心擴頻或向上擴頻,一般選擇向下擴頻,偶爾使用中心擴頻;

向下擴頻up spreading: δ = -Δf /fc x 100%,擴頻的頻率變化范圍≤基準頻率,其最大頻率等于基準頻率;

中心擴頻center spreading: δ = ±1/2Δf/fc x 100%,擴頻的頻率變化范圍圍繞基準頻率變化,其中間頻率等于基準頻率;

向上擴頻down spreading: δ = Δf/fc x 100%,擴頻的頻率變化范圍≥基準頻率,其最大頻率等于基準頻率;

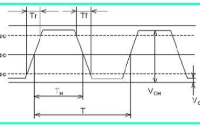

3)調制率fm:用于確定擴展時鐘頻率變化的周期/變化速度,在該周期內CLK頻率變化Δf 并返回到初始頻率fc,通常情況下調制率選擇33KHz。

4)調制波形:代表擴展時鐘頻率隨時間的變化曲線,可以為正弦波、三角波、非線性的Hershey kiss波等。

總結:如上圖所示,擴展率表征擴頻時鐘的頻率變化范圍;擴頻類型表征擴頻時鐘的頻率是往小了變化,還是往大了變化;調制率表征擴頻時鐘頻率變化的速度,多長時間從擴頻時鐘的頻率最小變為最大;調制波形表示擴頻時鐘的頻率變化不一定是線性的,可以是正弦波等非線性方式。

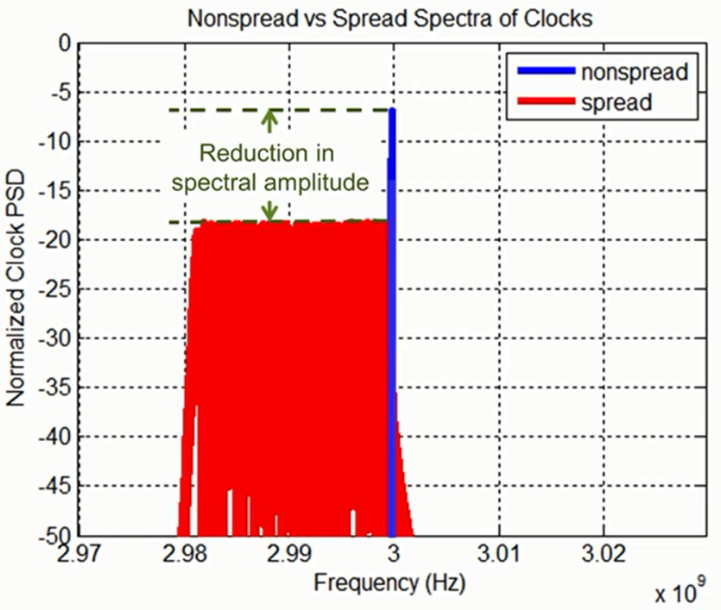

三、SSC擴頻時鐘抑制EMI示意

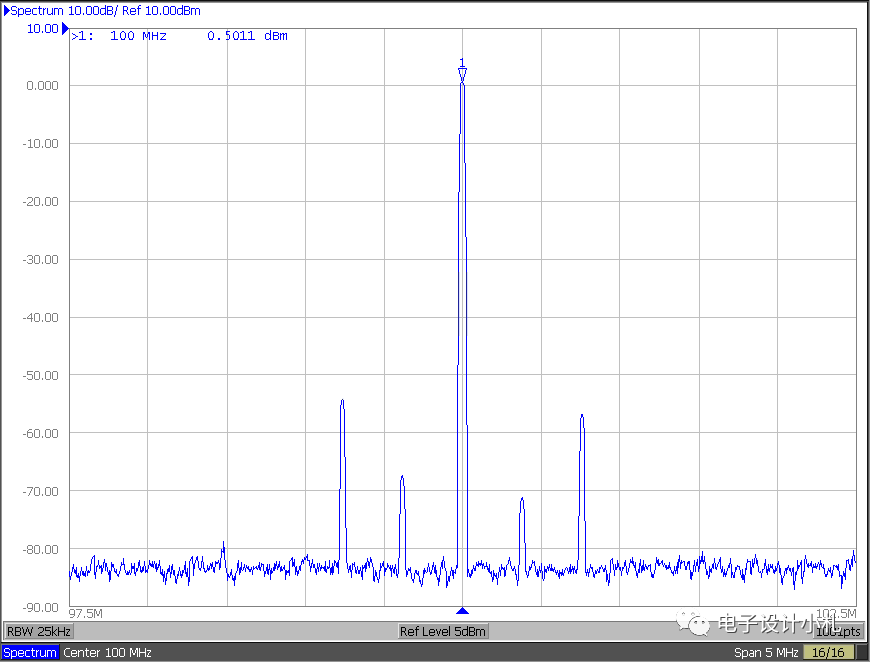

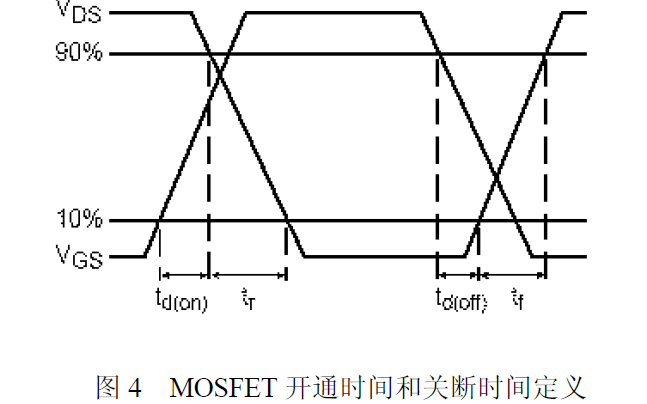

1)無擴頻信號-100MHz方波

如上圖所示,100MHz的方波其功率在0.5dBm,高功率的載波信號會導致輻射發送和電磁干擾,如果該信號的平衡或者端接匹配未做好,將進一步導致干擾加大。

對于降低EMI,通常做法比如修改局部電路,增加濾波、或者通過修改產品結構,增加接地屏蔽等,這些方法主要通過改變或者切斷輻射的路徑來降低,這些方法也會帶來額外的成本開銷,擴頻SSC技術是一種相對廉價的解決方案,其思路是用較寬頻上較低功耗的頻譜來替代較窄頻帶上較高功耗的頻譜,從而實現從能量源頭進行解決。

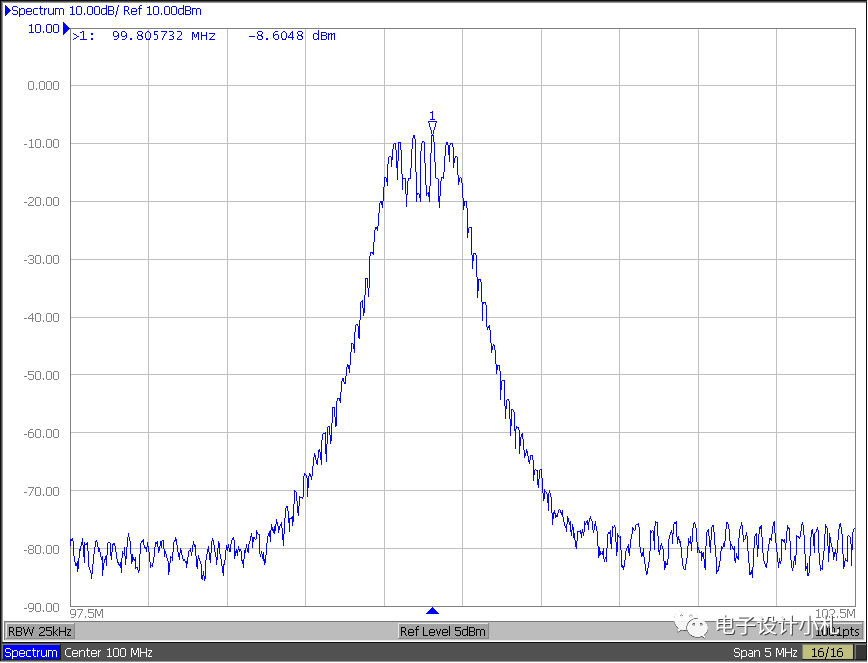

通過對該100MHz的方波進行擴頻,選用的擴頻率δ為0.5%,選用的擴頻類型為向下擴頻,選擇的擴頻調制率為33KHz,選用的調制波形為三角波,則其頻譜如上圖。

與原始信號相比,未加SSC時,信號能量非常集中,幅度較大,加了SSC后,信號能量被分散到一個頻帶范圍以內,信號能量的整體幅度也明顯降低,大約降低10dBm左右,這樣信號的EMI輻射發射就將會得到非常有效的抑制。

四、SSC擴頻時鐘應用

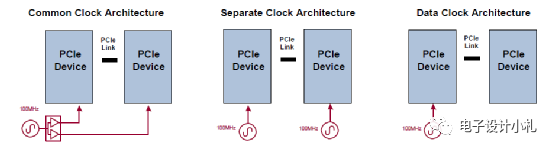

SSC擴頻時鐘在PCIe設備中應用廣泛,但需要注意下,PCIe的時鐘架構一般分為Common Clock Architecture(同源)、Separate Clock Architecture(獨立)、Data Clock Architecture(數據),其中Data Clock Architecture用的較少,只有PCIe Gen2和Gen3支持。

同源時鐘應用較為廣泛,其優點即其對時鐘的要求稍微低點,能夠支持SSC擴頻技術的應用,從而降低EMI;其缺點,其要求時鐘到各個PCIe設備的時鐘偏差小于12ns,這對于大背板應用存在困難。

獨立時鐘應用也蠻多,其優點即應用方便,時鐘不需要跨連接器和背板等;其缺點,對時鐘要求較高,一般不支持SSC擴頻,畢竟當時鐘信號被擴頻后,其實際信號相當于在原始信號上增加了抖動,這個量級的抖動對接收端時鐘的恢復有時會有較大困難。

五、SSC擴頻時鐘缺點

SSC會導致信號的頻率產生波動,相當于在原始信號上增加了抖動,因此從示波器看,如果以某一個邊沿進行采樣基準,會發現其他波形的邊沿會左右變化,累加波形余暉顯示很粗的其他波形邊沿。

-

emi

+關注

關注

54文章

3896瀏覽量

135683 -

時鐘頻率

+關注

關注

0文章

73瀏覽量

21144 -

擴頻時鐘

+關注

關注

0文章

13瀏覽量

10919 -

ssc

+關注

關注

0文章

26瀏覽量

11870 -

寬帶信號

+關注

關注

1文章

26瀏覽量

11530

發布評論請先 登錄

擴頻時鐘技術分享:SSC技術是什么、SSC對測試高速總線信號的影響

555時基電路的主要參數

MOSFET的主要參數理解和特點概述

SSC擴頻時鐘概述和主要參數

SSC擴頻時鐘概述和主要參數

評論