如何具體實現輸出信號的分頻和倍頻?

在現代電子系統中,信號分頻和倍頻是非常常見的技術。它們可以幫助電子設備在處理信號時具有更高的精度和準確性。下面我將詳細介紹如何實現輸出信號的分頻和倍頻。

一、分頻

1. 什么是分頻?

分頻是一種將一個信號分成多個周期的技術。簡單來說,就是使輸出信號的周期數變為輸入信號的周期數的整數倍。當信號進行分頻后,頻率就會降低,而信號卻保持原來的形態(波形)。

2. 如何實現分頻?

實現分頻的方案有很多,其中常用的有如下幾種:

(1)分頻器

分頻器是最常見的分頻方案之一。它通常采用計數器/定時器來實現。在分頻器的輸出中,一個周期包含的時鐘脈沖數量是輸入的周期數的整數倍。例如,如果輸入信號的頻率為1kHz,要將其分成1/10,則分頻器每10個輸入周期輸出1個時鐘脈沖,就像下面這樣:

(2)PLL

PLL(Phase-Locked Loop)是一種以輸入信號為參考信號,在輸出信號中保持相位,同時放大和分頻信號的技術。在使用PLL實現分頻時,輸入的參考信號在PLL內部被倍頻或分頻。背后的基本原理是相位檢測環路,這是一個閉環反饋系統,它將參考信號與PLL內部產生的信號進行比較并調整輸出信號的相位和頻率,使得輸出信號的頻率是參考信號的整數分頻倍數。

二、倍頻

1. 什么是倍頻?

倍頻是一種將輸入信號的頻率乘以整數的技術。換句話說,在輸出信號中,每個周期包含的時鐘脈沖數量是輸入的周期數的整數倍。倍頻技術通常用于高頻率信號的產生,例如,將本來的低頻信號經過倍頻后,可以得到更高的頻率信號。

2. 如何實現倍頻?

實現倍頻的方案也有很多,其中常用的有如下幾種:

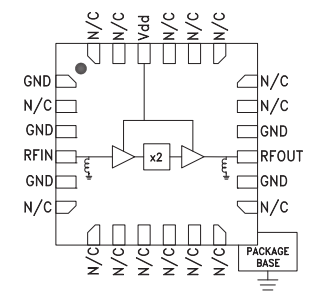

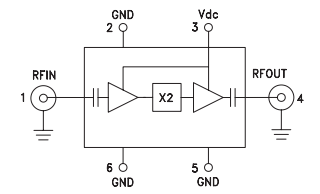

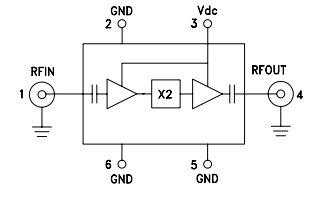

(1)倍頻器

倍頻器可以將輸入信號的頻率提高一個整數倍。它通常是由一個振蕩器和一個頻率加倍電路組成。在輸出中,時鐘脈沖的數量比輸入的周期數多。例如,將輸入信號頻率倍增成2MHz,輸出的時鐘脈沖的數量是輸入信號的周期數的兩倍。

(2)鎖相環倍頻器

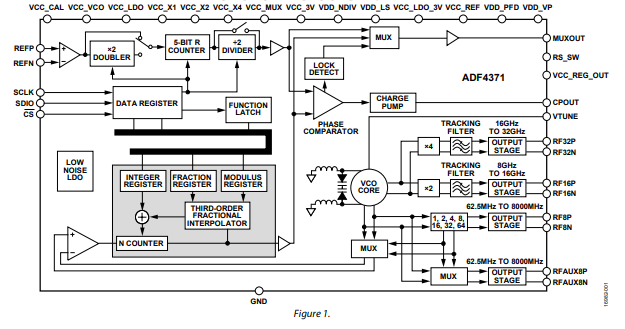

鎖相環倍頻器(PLL)是一種基于相位鎖定環路的技術,它可以將輸入信號的頻率倍增。PLL系統由幾個重要的組件組成,如分頻器、相位檢測器、VCO(Voltage Controlled Oscillator)等。

輸入信號經過分頻器后,變成PLL系統的參考頻率,反饋給相位檢測器。相位檢測器輸出的信號會驅動VCO發生變動。當經過一段時間后,VCO輸出信號的頻率和輸入信號的頻率趨于一致和穩定,PLL系統達到相位鎖定的效果。此時輸出信號的頻率為輸入信號的頻率的整數倍。例如,輸入信號的頻率為1MHz,通過PLL技術倍增10倍后,輸出的信號頻率為10MHz。

以上是分頻和倍頻技術的實現方案。在實際應用中,可以根據具體的需求來選擇適合的技術方案。同時,設計者也應注意到不同技術方案的優缺點,從而合理利用,提高電子系統的性能。

-

分頻器

+關注

關注

43文章

536瀏覽量

53361 -

pll

+關注

關注

6文章

982瀏覽量

138175 -

倍頻器

+關注

關注

8文章

124瀏覽量

37370

發布評論請先 登錄

CDC5801A:低抖動時鐘倍頻器與分頻器的卓越之選

音響中軟件分頻和硬件分頻區別解析以及對音質和成本的影響

?CDC5801A低抖動時鐘倍頻/分頻器技術文檔總結

LMX1204低噪聲高頻JESD緩沖器/倍頻器/分頻器技術解析

24V、1000MHz 高輸出功率倍頻器線路放大器 MMIC skyworksinc

Analog Devices Inc. ADF4382x小數N分頻鎖相環 (PLL)數據手冊

ADF4371帶集成VCO的微波寬帶合成器技術手冊

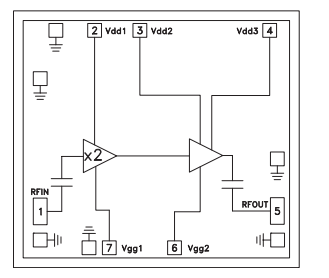

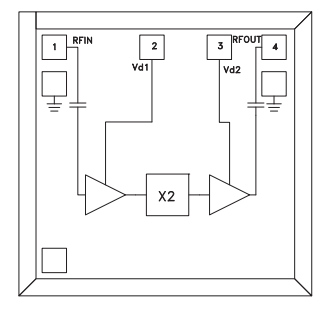

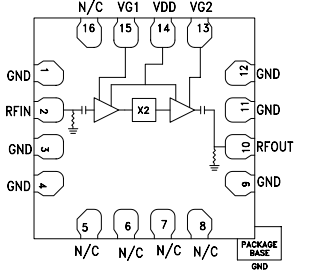

HMC942LP4E x2有源倍頻器,25-31GHz輸出技術手冊

HMC598 x2有源倍頻器芯片技術手冊

HMC448 x2有源倍頻器芯片技術手冊

HMC1096LP3E GaAs pHEMT MMIC x2有源倍頻器,3.8-5.6GHz輸出技術手冊

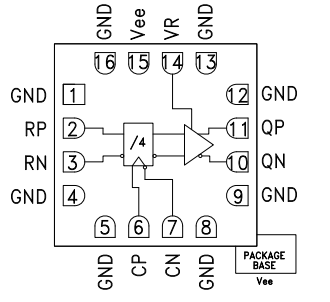

HMC959LC3提供復位功能和可編程輸出電壓的26GHz 4分頻器件,采用SMT封裝技術手冊

HMC-C034 x2有源倍頻器模塊技術手冊

HMC-C033 x2有源倍頻器模塊技術手冊

如何具體實現輸出信號的分頻和倍頻?

如何具體實現輸出信號的分頻和倍頻?

評論