看完了flush,再看下flushNext的用法

》flushNext

在Stage里,有關(guān)flushNext提供的API有:

defflushNext():Unit = flushNext(ConditionalContext.isTrue)

defflushNext(cond : Bool):Unit = internals.request.flushNext += cond

調(diào)用flushNext,最終會(huì)將flushNext的需求暫存到internals.request.flushNext中。

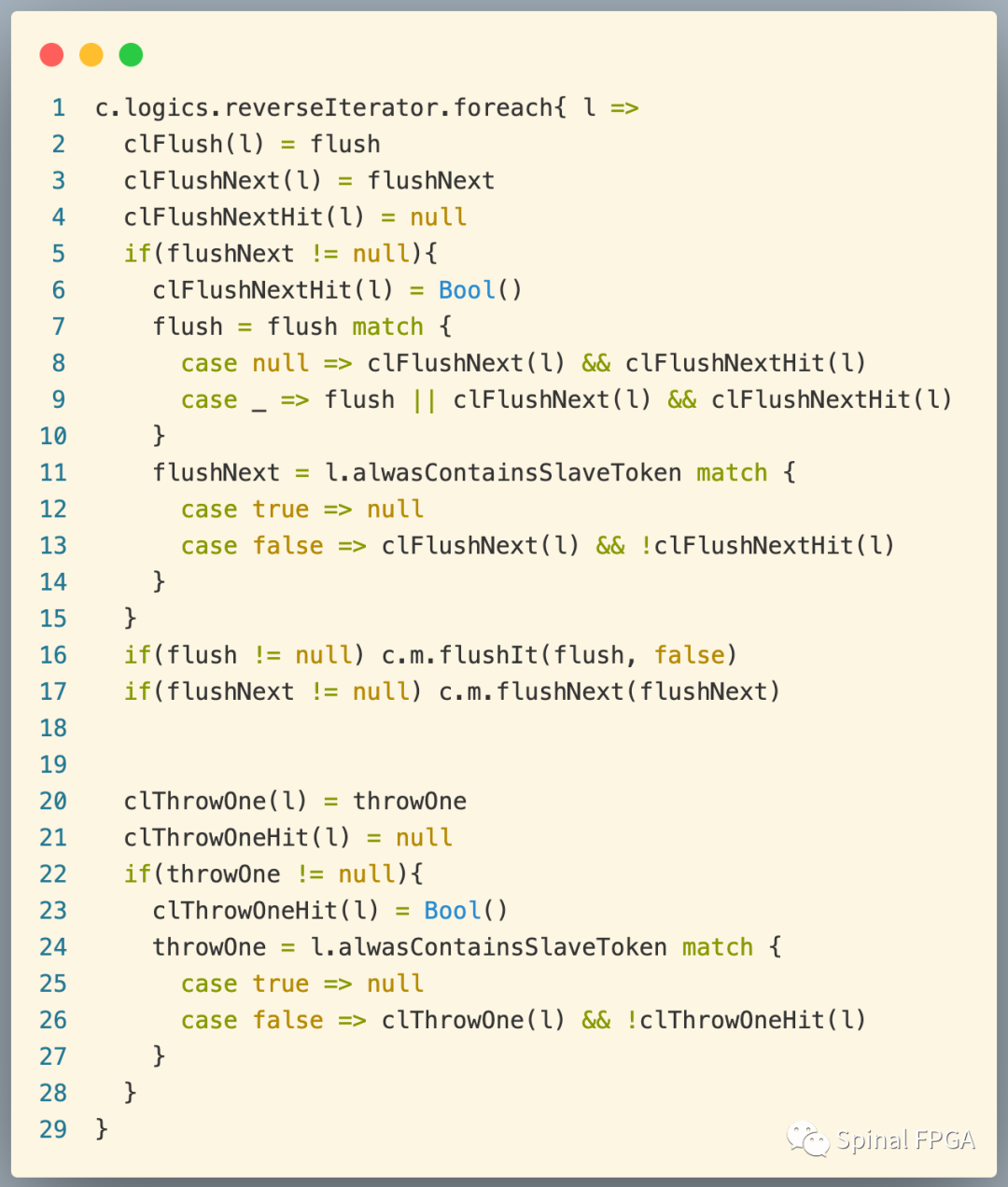

在Pipeline中,propagateRequirements函數(shù)中對(duì)于每一級(jí)Stage的處理:

varflushNext = stage.internals.request.flushNext.nonEmpty generate orR(stage.internals.request.flushNext)

如果flushNext不為空,則將所有條件或后得到flushNext電路對(duì)象。

在上面的這段描述中,針對(duì)驅(qū)動(dòng)當(dāng)前Stage的Conntection處理,flushNext電路將會(huì)被存儲(chǔ)在clFlushNext(l)中。如果flushNext不為空(line:5),可以看到在line7:9行處理時(shí),不管flush是存在,都會(huì)創(chuàng)建一個(gè)flush電路對(duì)象,也就意味著一般情況下flush,flushNext不需要同時(shí)使用。

而在line11:14中,以M2S為例,alwasContainsSlaveToken為True,會(huì)將flushNext清空。此時(shí)在line16:17時(shí),僅會(huì)對(duì)驅(qū)動(dòng)當(dāng)前Stage的Stage Master調(diào)動(dòng)flushIt函數(shù),也就意味著flushNext將會(huì)向前傳播,前級(jí)相當(dāng)于執(zhí)行flushIt。

clFlushNext的使用僅在Connection中使用到。還是以M2S為例,其處理邏輯為:

if(flushNext != null&& !flushPreserveInput) s.valid clearWhen(flushNext && s.ready)

在這里,如果flushNext不為空(flushPreserveInput默認(rèn)為true),s.valid僅會(huì)在slave端ready和flushNext同時(shí)為高時(shí)才會(huì)清零。對(duì)比f(wàn)lush操作:

if (flush!= null&& !flushPreserveInput) s.valid clearWhen(flush)

也就意味著flushNext存在ready的情況下才具有意義。

》example

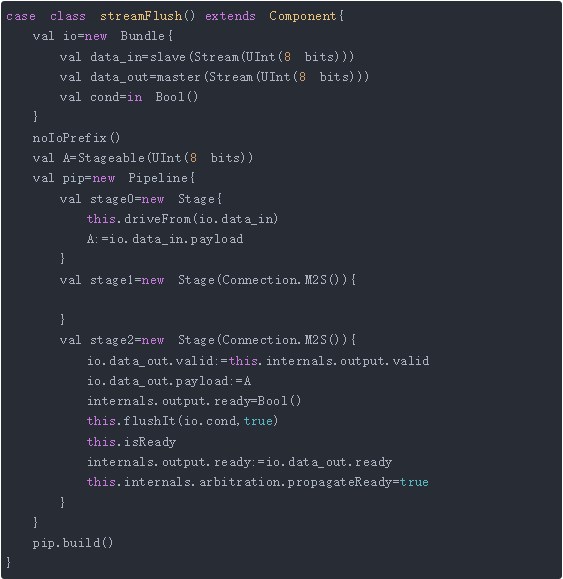

結(jié)合上面的分析,flushNext與flush的最大區(qū)別在于存在ready傳播的情況。這里先給出一個(gè)flsuhIt的例子:

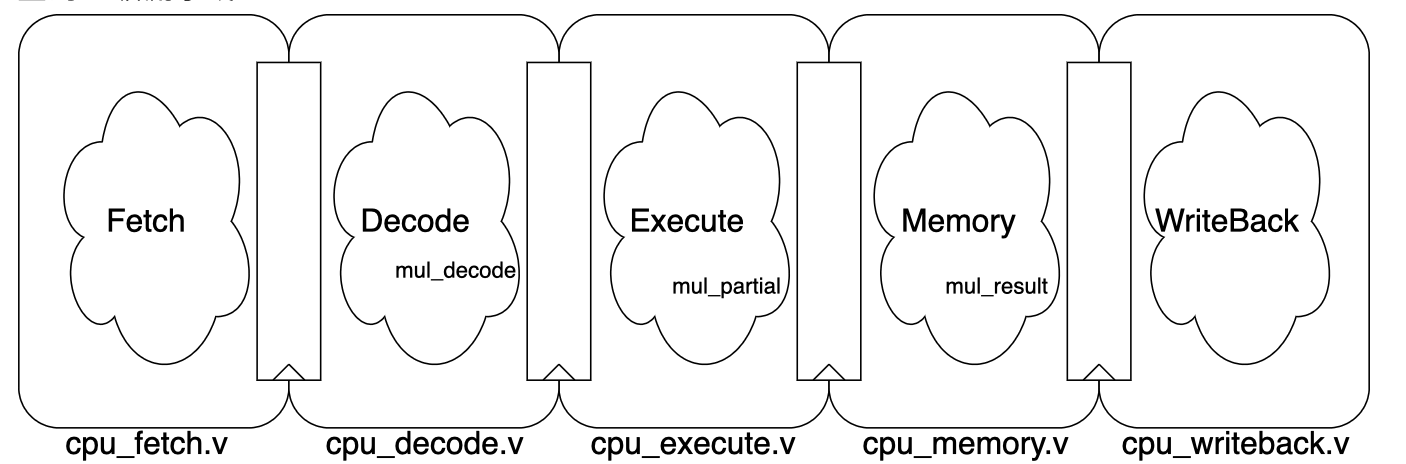

這里是一個(gè)三級(jí)pipeline,最后一級(jí)調(diào)用flushIt操作,flushRoot參數(shù)傳遞為true。

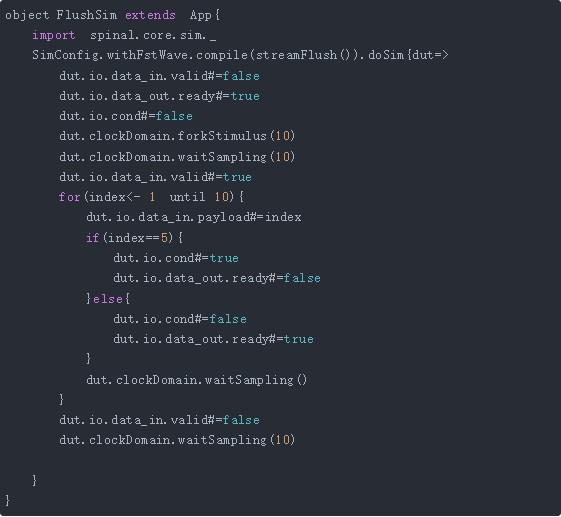

采用下面的仿真代碼:

我們這里在index==5時(shí)將cond拉高一拍,data_out.ready拉低一拍。

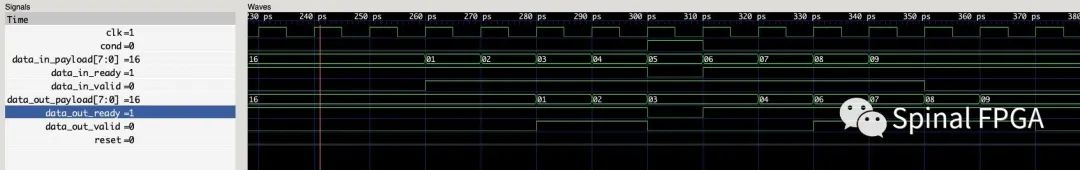

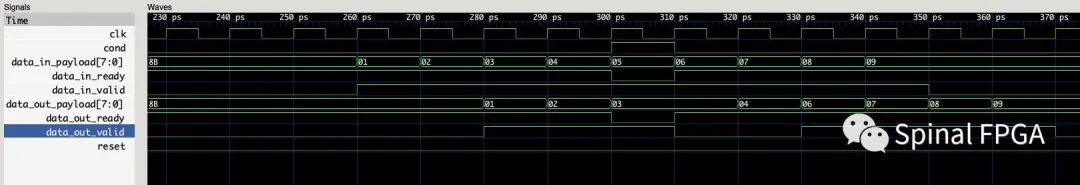

仿真波形如下:

可以看到,由于這里流水線為3級(jí),在index=5時(shí)執(zhí)行flush數(shù)據(jù)3,4,5不會(huì)從data_out有效輸出。

將flushRoot參數(shù)修改為false:

cond為高時(shí)data_out.valid仍然為高電平,下一個(gè)時(shí)鐘周期拉低。雖然此時(shí)ready為低電平,這個(gè)數(shù)據(jù)沒(méi)有被消耗,但其拉低時(shí)間不考慮ready信號(hào)的高低電平。

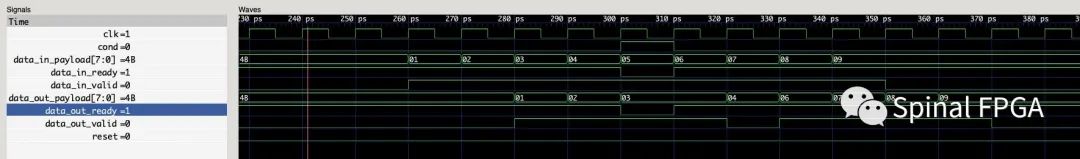

再將上面的代碼換成flushNext:

可以看到,雖然cond為高,但其仍會(huì)堅(jiān)持將此時(shí)已經(jīng)傳播到stage2的3給穩(wěn)定傳輸出去,僅有4,5不會(huì)被data_out輸出。

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

20250瀏覽量

252225 -

仿真器

+關(guān)注

關(guān)注

14文章

1051瀏覽量

87263 -

Pipeline

+關(guān)注

關(guān)注

0文章

29瀏覽量

9960

原文標(biāo)題:pipeline高端玩法(八)—FlushNext

文章出處:【微信號(hào):Spinal FPGA,微信公眾號(hào):Spinal FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Pipeline ADCs Come of Age

Pipeline ADCs Come of Age

流水線模數(shù)轉(zhuǎn)換器的時(shí)代-Pipeline ADCs Come

如何降低開(kāi)發(fā)門檻助力音視頻創(chuàng)新玩法

修改V4L2的Video Pipeline的devicetree

Ping命令的7個(gè)基礎(chǔ)用法

SpinalHDL里pipeline的設(shè)計(jì)思路

pipeline高端玩法—優(yōu)先級(jí)介紹

pipeline高端玩法—看下FlushNext的用法

pipeline高端玩法—看下FlushNext的用法

評(píng)論