點擊上方藍字關注我們

低采樣速率ADC仍然采用逐次逼近(SAR)、積分型結構以及最近推出的過采樣ΣΔADC,而高采樣速率(幾百MSPS以上)大多用閃速ADC及其各種變型電路。然而,最近幾年各種各樣的流水線ADC已經在速度、分辨率、動態性能和功耗方面有了很大的提高。對于幾Msps到100Msps的8位高速和16位低速模數轉換器(ADC),流水線已經成為最流行的模數轉換器結構,它可以涵蓋很廣的應用范圍,包括CCD成像、超聲成像、數字接收、基站、數字視頻(如HDTV)、xDSL、線纜調制解調器以及快速以太網。本文介紹了流水線ADC的內部結構和工作原理。

一、流水線ADC結構

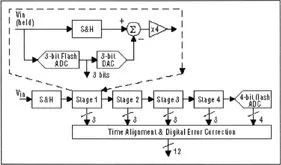

圖1為12位流水線ADC的結構圖。輸入Vin首先被采樣/保持(S&H)電路所采樣,同時第一級的閃速ADC把它量化為3位,此3位輸出送給一3位的DAC(具有12位精度),輸入信號減去此DAC的輸出,放大4倍送給下一級(第二級),繼續重復上述過程,每級提供3位,直到最后一級4位閃速ADC。對應某一次采樣,由于每級在不同的時間得到變換結果,因此在進行數字誤差校正前用移位寄存器對各級的結果先按時間對準。注意只要某一級完成了某一采樣的變換,得到結果并把差值送給下一級,它就可以處理下一個采樣。因此流水線操作提高了處理能力。

1. 延遲時間

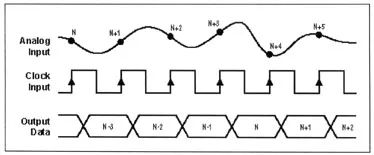

由于每個采樣必須通過整個流水線才能得到數字誤差校正所需的各個位,因此流水線ADC有數據延遲。在圖1的例子中,大約要延時3個周期(見圖2)。

2. 數字誤差校正

大多數現代流水線ADC采用“數字誤差校正”技術來大大降低對閃速ADC(即內部的每個比較器)的精度要求。圖1中,3位的差值輸出其動態范圍是輸入信號Vin的1/8,然而隨后的增益只有4,因此給第二級的輸入只有第二級ADC 3位范圍的一半(在第一級的3位變換沒有誤差的情況下)。

如果第一級的3位閃速ADC的某一個比較器有很大的失調,同時輸入電壓又正處于此比較點上,那么就會產生不正確3位碼和不正確的3位DAC輸出,此時產生了不同的差值。可以證明,只要放大后的差值沒有超出后續的3位ADC的范圍,以后產生的LSB碼加上前面不正確的3位MSB碼同樣能產生正確的ADC結果。實際上,四級流水線中的第一級3位閃速ADC只需4位的精度。數字誤差校正不能修正最后4位閃速轉換器產生的誤差。但是,這里產生的任何誤差要除以前面的累積增益(44),因此只要求最后一級的精度大于4位。

在圖1的例子中,雖然每級產生3位,但由于級間的增益是4,每級(第一級至第四級)的有效分辨率為2位。額外的位只是用于使尾數減半,使下一級3位ADC有額外的范圍進行數字校正。這種方法被稱之為級間“1位重疊”。因此整個ADC的有效位數是2+2+2+2+4=12位。

3. 元件精度

數字校正不能修正每個DAC和增益放大器的增益和線性特性。特別是前端的采樣保持電路,DAC需要12位的精度。但是隨后各級的元件只需較低的精度(如,第二級10位精度,第三級8位,等等),因為他們的誤差要除以前面的級間增益。通常利用這一事實把流水線逐級做小來進一步降低功耗。

在大多數采用CMOS和BiCMOS技術的流水線ADC中,采樣/保持、DAC、加法器和增益放大器通常用乘法DAC(MDAC)的單開關電容電路來實現。限制MDAC精度的主要因素是內在的電容不匹配。純雙極型實現方法更加復雜,主要受電流源DAC和級間增益放大器中電阻不匹配影響。通常12位或更高精度都需要阻容修正和數字校正,特別是第一級。

4. 數字標定

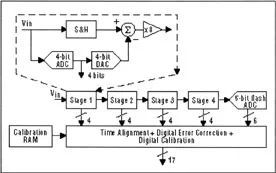

MAX1200/MAX1201/MAX1205系列(16位1Msps、14位1Msps和2Msps ADC)采用數字標定來保證其優越的精度和動態性能。MAX1200系列是CMOS流水線ADC,它由四級4位(其中一位重疊)和最后的5位閃速ADC構成,總位數是3+3+3+3+5=17位(參見圖3)。額外的1到3位是數字標定用來量化誤差項來達到更高的精度,舍掉它們后,最后得到14位或16位的精度。

標定從第三級的MDAC開始。第三級以上的MDAC誤差已經足夠小,不必標定。第三級的輸出經剩余的流水線ADC數字化后,誤差項存入片內的RAM中,第三級標定后,就可以用同樣的方式由第三級來標定第二級,同樣,第二級標定后,再標定第一級。為了使標定免受噪聲的影響,采用取平均的方法(特別是第一和第二級的MDAC)。在正常轉換期間,從RAM中取出標定的誤差項來調整數字誤差校正后的輸出結果。

二、各種變型電路

從圖1可以看出:根據每級的分辨率多少、最后閃速ADC的位數、是否采用數字標定和修正來提高最初幾級的精度可以衍生出各種各樣的流水線ADC。采樣速率和分辨率部分地決定了每級采用的位數。通常,高速CMOS流水線ADC每級一般用于低位數(甚至每級只有一位,級間增益只有2),原因是CMOS比較難實現很高增益的寬帶放大器。低采樣速率的CMOS流水線ADC和雙極型流水線ADC(即使采樣速率很高)每級常采用多位數,這同時也帶來了更小的數據延遲。

CMOS MAX1425/MAX1426 (10位10Msps和20Msps)系列使用流行的每級1.5位結構,每級只有1位分辨率和“0.5位重疊”,每級有一個1.5位的閃速ADC(只有2個比較器)。可以證明,利用數字誤差校準,可以達到2位閃速ADC和DAC的標準MDAC同樣的效果,這些轉換器以20Msps速率采樣10MHz輸入信號時可以達到高達59dB的SNR。

MAX1444/MAX1446/MAX1448/MAX1449系列(10位40/60/80/105Msps)是最新的采用每級1.5位結構的高速甚低功耗10位ADC。它們組合了寬帶低失真采樣保持放大器,在整個奈奎斯特頻率內以及高于奈奎斯特頻率內保證了卓越的動態性能。該系列產品可用于數字接收機中的欠采樣設計。

三、流水線ADC和其它ADC的比較

1. 與逐次逼近型比較

在逐次逼近(SAR)ADC中,用一個高速高精度比較器將模擬輸入和前一次得到的模數轉換結果通過DAC后的輸出相比較,依次得到MSB到LSB的每一位,逐漸逼近輸入模擬信號。SAR的這一串行工作方式從本質上限制了它的工作速度,最高約為幾Msps左右,對更高的分辨率(14到16位)速度就更低。流水線ADC則不同,它是并行結構,各級同時以逐次方式得到1位或幾位。雖然SAR中只需一個比較器,但是這個比較器必須高速工作(速率約為總位數×采樣速率),其精度必須與ADC本身一樣高,相反,流水線ADC內的比較器則不需要這一速度和精度。

當然,流水線ADC通常比相同位數的SAR占據更多的硅片面積。SAR只需一周期的延遲時間(=1/Fsample)就得到結果,而流水線ADC需要3或更多周期的延遲。與流水線ADC一樣,12位精度以上的SAR也需要某些形式的校正和標定。

2. 與閃速型比較

盡管流水線ADC是并行機制,但它還需要DAC的精密轉換和級間增益放大,因此存在建立時間問題。純閃速型ADC不同,它有大量的比較器,每個比較器由寬帶,低增益前置放大和鎖存器構成。該前置放大器不像流水線ADC中的放大器,它只需提供增益,不需要線性和精度,只是比較器的觸發點要很精確。因此流水線ADC速度根本比不上設計得很好的閃速型ADC.

雖然超高速8位閃速ADC(及各種合并/插值變體)的采樣速率高達1.5Gsps(比如MAX104/MAX106/MAX108),但是很難找到10位的閃速ADC,特別是12位及高于12位的ADC還沒有商用化。這是因為閃速ADC分辨率每增加1位,比較器數量就增加1倍,同時每個比較器的精度必須增加1倍。流水線ADC則不同,它的復雜性隨分辨率線性增加,不是指數增加。

在相同的采樣速率下,流水線ADC比閃速ADC消耗功率少得多。流水線ADC不易受比較器亞穩態的影響。閃速ADC中的比較器亞穩態會導致火花碼錯誤(即ADC輸出不可預測、不穩定結果的情況)。

3. 與Σ-Δ型比較

過采樣/Σ-Δ型ADC多用于帶寬限于22KHz以內的數字音響中。但是最近一些Σ-Δ型轉換器已經在12到16位的分辨率下達到了1至2MHz的帶寬。它們通常是高階的Σ-Δ調制器(比如4階或更高),同一個多位的ADC和多位的DAC一起工作,主要應用于ADSL。Σ-Δ型轉換器無需校正/標定,即使是16到18位分辨率,也不需要模擬輸入前的陡峭滾降的抗混疊濾波器,因為它的采樣頻率遠遠高于有效帶寬,它由后端的數字濾波器來處理混疊問題。Σ-Δ型轉換器的過采樣本質還把模擬輸入中的任何系統噪聲“平均濾除”。

但是Σ-Δ型轉換器是以犧牲速度換取分辨率的。每輸出一次采樣結果都需要對輸入采樣很多次(比如至少16次,甚至更多),這就需要Σ-Δ調制器中模擬元件的工作速率要比最終數據輸出速率快很多。數字濾波器的設計比較繁瑣,另外,它也占據了一些硅片面積。目前,最快的高分辨率Σ-Δ型轉換器還達不到幾MHz的帶寬。像流水線ADC一樣,Σ-Δ型轉換器也有延遲。

四、結論

流水線ADC結構適合于幾Msps到100Msps采樣速率,其復雜性隨分辨率的增加只是線性(而不是指數)增加,具有高速、高精度和低功耗特性,適用于各種場合,特別是數字通訊領域,在這些領域中轉換器的動態性能經常比微分非線性(DNL)和積分非線性等傳統的ADC特性更重要。在大多數的應用中,流水線ADC的數據延遲都無關緊要。

MAXIM一直致力于發展新型轉換器來增強其流水線ADC業務,包括馬上就要公布的高性能的12位20/40/60Msps轉換器MAX1420/MAX1421/MAX1422。MAXIM的流水線ADC使整個MAXIM的ADC系列更加豐富和完整。

有你想看的精彩 至芯科技FPGA就業培訓班——助你步入成功之路、9月23號北京中心開課、歡迎咨詢! 解析高速ADC和DAC與FPGA的配合使用 基于FPGA的圖像實時處理系統設計

掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

原文標題:流水線ADC的內部結構和工作原理是什么

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636247

發布評論請先 登錄

軟通動力ASDM AI優先軟件研發流水線助力軟件工程發展

Pipelined ADC流水線模數轉換器的工作原理

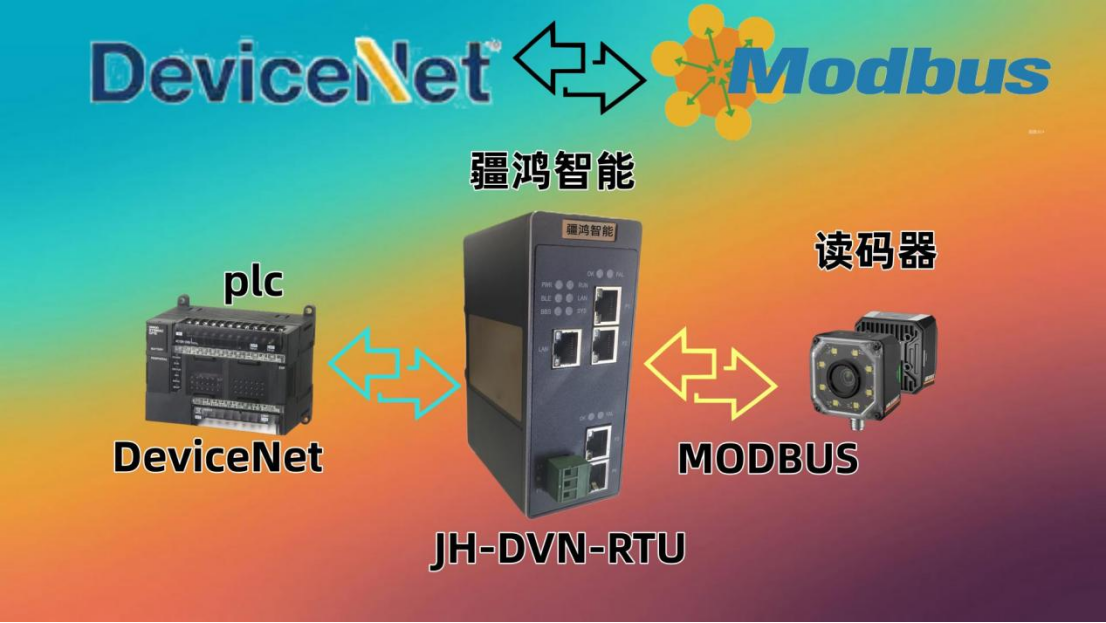

智造中樞:疆鴻智能DEVICENET轉MODBUS RTU網關在食品包裝流水線的融合之舞

流水線基本結構

如何更好地選擇工業流水線上用的條碼掃碼器?

流水線掃碼升級選NVF230!工業二維碼讀碼器方案實測

如何判斷感應電機內部結構的故障?

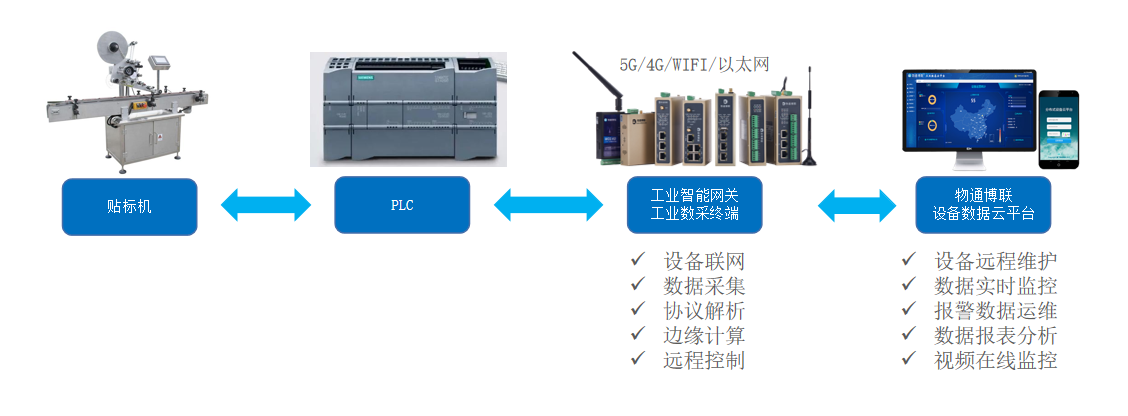

自動化開裝封碼流水線數據采集解決方案

面包成型流水線數據采集遠程監控系統

遠程io模塊在汽車流水線的應用

工業4.0時代,為什么你的流水線必須配備固定式掃碼器?

工業流水線上用的條碼掃碼器,如何選擇與使用?

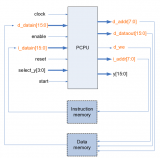

RISC-V五級流水線CPU設計

流水線ADC的內部結構和工作原理是什么

流水線ADC的內部結構和工作原理是什么

評論