寫在前面

之前曾經整理過verilog的各類運算符的表達方式,但是在學習的過程中并未深入研究關于邏輯運算符的相關知識,導致在實際使用過程中錯誤頻出,下面是我從網絡上整理的相關verilog的邏輯運算符的相關知識,希望對各位有所幫助。

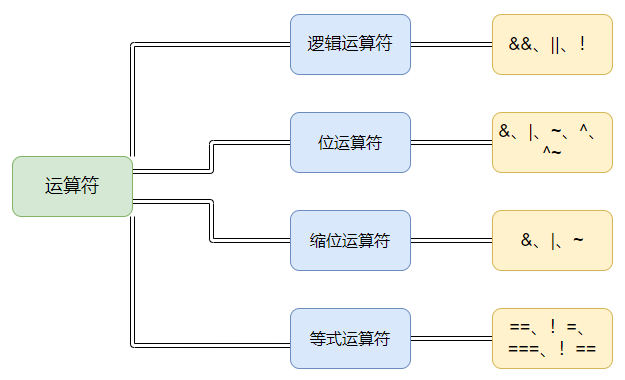

分類

按照常見的幾類verilog邏輯運算符可以將其分為以下幾類

邏輯運算符:&&、||、!

&&和||是雙目運算,用在兩個數之間;!為單目運算符用在數字之前

在N = A xx B的邏輯運算中,A、B、N都只存在兩個值:true or false,二者在機器中表示1和0;在進行操作時A與B的數據寬度可以不等

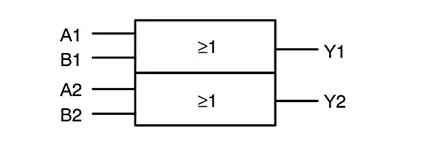

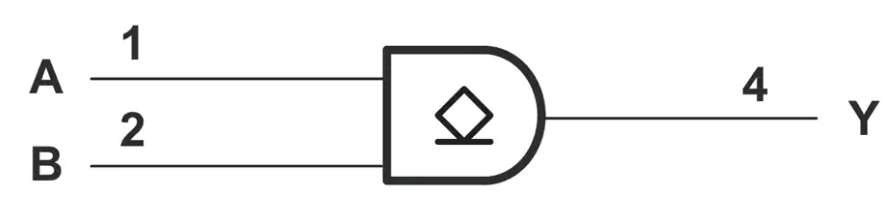

位運算符:&、|、~、^、 ^~

其中的&、|、^、 ^~ 均為雙目運算符,~為單目運算符;相較于邏輯運算符,位運算符的核心是按位,二者具體的區別可以通過綜合后的RTL視圖進行區分

需要注意的是位運算符與邏輯運算符一樣,兩個運算數可以是不同長度,在運算的過程中右對齊,且缺少的位數將用0補齊

縮位運算符:&、|、~

又稱為縮減運算符,為單目運算符;對單個操作數進行遞推運算,運算結果得到的是一位二進制數

補充:異或同或也可以進行縮位運算,其中的縮位異或常用于奇偶校驗

等式運算:==、 !=、=== 、 !==

進行數值的比較操作,相較于==而言===會更加嚴格;后者在比較時會對高阻態和不定態進行比較

以上便是關于verilog的邏輯運算符的一些基礎知識,歡迎各位交流學習。

審核編輯 黃宇

-

Verilog

+關注

關注

30文章

1374瀏覽量

114614 -

數字電路

+關注

關注

193文章

1662瀏覽量

83474 -

運算符

+關注

關注

0文章

173瀏覽量

12114

發布評論請先 登錄

FPGA 入門必看:Verilog 與 VHDL 編程基礎解析!

C語言主要特點

NL27WZ32雙路2輸入或邏輯門技術深度解析

C語言宏拼接運算符典型使用

復雜的軟件算法硬件IP核的實現

第4章 C語言基礎以及流水燈的實現(4.3 4.4)

AES加解密算法邏輯實現及其在蜂鳥E203SoC上的應用介紹

SN74AHC1G09 單路2輸入正邏輯與門(開漏輸出)技術解析與應用指南

協議分析儀支持哪些高級觸發選項?

基于LockAI視覺識別模塊:C++圖像的基本運算

基于LockAI視覺識別模塊:C++圖像的基本運算

verilog的邏輯運算符

verilog的邏輯運算符

評論