作者:Rob Bauer

Versal Premium 和 Versal HBM 系列高級產品營銷經理

縱觀各行各業與全球范圍,尖端技術都需要對海量數據的快速處理和傳輸。有線通信需要能夠支持網絡力量爆炸式增長的基礎設施,而隨著 800G 以太網乃至更高標準的引入,這種勢頭只會有增無減。在數據中心,功能強大的推薦引擎和金融科技( FinTech )軟件需要對大型數據集進行快速分析。對于測試工程師而言,當他們努力跟上新一代協議標準快速發展的腳步時,計算能力似乎永遠都尚有差距。

在這些用例中,是什么限制了性能的提升呢?答案通常是存儲器帶寬,而非底層計算技術。這些系統具有尺寸和功耗等約束條件,傳統的雙數據速率( DDR )存儲器技術很難提供足夠的帶寬。

相反,AMD Versal HBM 自適應 SoC 采用高帶寬存儲器( HBM )。這些自適應 SoC 可將快內存、自適應計算和安全連接合并到單個器件中,從而有助于消除內存瓶頸。與 DDR 等分立式存儲器解決方案相比,它們能夠簡化開發并提供更高的總存儲器帶寬1、 更小的封裝2、 以及更低的功耗3。

我很高興地告訴大家,Versal HBM 器件現已投入量產,準備好為您的新一代產品提供支持,并加速其推向市場。而且無需等待即可啟動設計。功能豐富的 VHK158 評估套件現已可供購買。

信心滿滿地為內存密集型應用設計系統

Versal HBM 自適應 SoC 的詳細介紹演示了它們如何將系統和應用從網絡基礎設施轉換為數據分析。Versal HBM 器件基于成熟的 Versal 架構而構建,采用第四代堆疊硅片互聯( SSI )技術,將多 Tbps HBM、硬化連接和其它 IP 以及密集的可編程邏輯集成在單個器件中。

這樣做的結果是,系統架構師能夠最大限度減少內存、計算和連接之間的瓶頸問題,為計算密集程度最高的應用釋放性能。與包含 4 個以 4266Mbps 運行的 LPDDR4 組件的典型實現方案相比,Versal HBM 系列可提供高達 6 倍的存儲器帶寬1,允許多個功能并行訪問存儲器和驅動器性能。此外,利用器件集成的 32GB 內存,Versal HBM 系列可提供的內存容量為 AMD Virtex UltraScale+ HBM 器件的 2 倍4。而且它具有 112G PAM4 和 32G NRZ 收發器,其收發器帶寬比 Virtex UltraScale+ HBM FPGA 多 1.8 倍5。

在系統設計中產生立竿見影的效果

與復雜的 DDR 接口相比,計算、內存和連接的緊密集成可簡化系統設計,有助于優化開發并加速產品上市進程。

-

節省功耗:與 DDR 相比,具有內存封裝的 Versal HBM 系列可節省高達 65% 的功耗 (pJ/bit)3,使其更易于實現設計的供電和冷卻。

-

獲得 PCB 設計靈活性:集成型內存較之 DDR 占用空間更少;一個 Versal HBM 自適應 SoC 可替代多達 24 個分立式 LPDDR4 組件。這有助于為電路板實現更多功能而釋放空間,并讓系統架構師能夠更靈活地專注于實現產品差異化。

-

簡化并加速設計:與需要精細調整物理接口才能實現高性能的 DDR 相比,Versal HBM 器件更易于使用。除了集成型內存以外,Versal HBM 器件還包括可編程片上網絡,其可以實現往返于硬化 HBM 控制器的數據路由,從而在器件的任何位置進行讀/寫訪問。

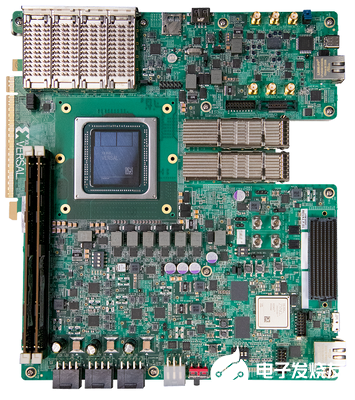

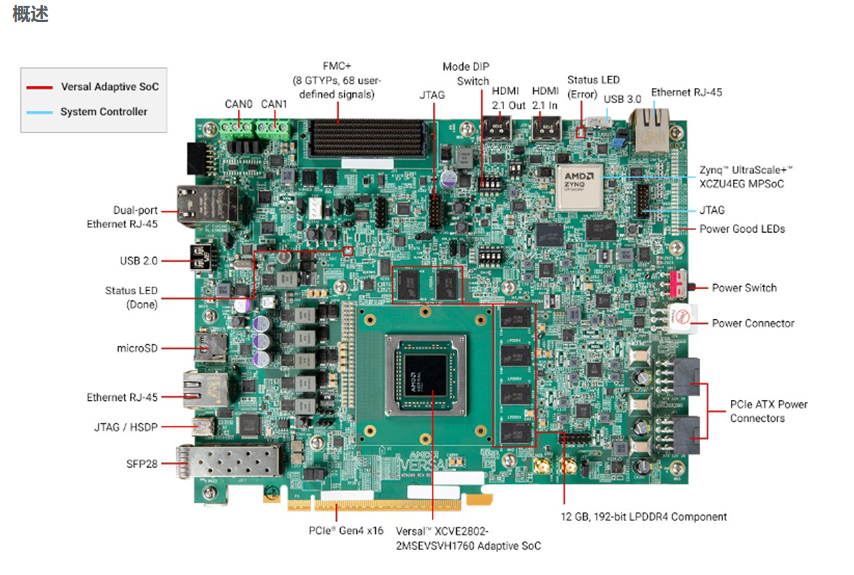

使用 VHK158 評估套件立即啟動開發

開發人員越快完成設計測試,就能越早開始部署產品。VHK158 評估套件可讓硬件開發人員和系統架構師快速評估 Versal HBM 自適應 SoC 的性能、功耗和連接性,賦予開發人員以十足的信心,打造出滿足獨特需求的硬件設計。

通過使用這款功能豐富的評估套件,開發人員不僅能輕松連接到現有系統來驗證其設計,而且還能探索板載功能的系統級優勢。

該評估套件可提供多種連接選項,包括 QSFP-DD、QSFP28、支持 PCIe Gen5x8 和 Gen3/4x16 的 PCIe 邊緣連接器,以及 FMC+ 連接器。此外,它還包括一組強大的配件,如 micro-SD 卡、回送模塊和以太網線纜。該套件的相關資料生態系統有助于優化設計周期;大量的文檔、演示視頻、設計示例和參考設計使開發人員能夠快速啟動運行。一旦啟動設計,開發人員就可以使用 AMD Vivado 設計套件(面向 AMD 自適應 SoC、由機器學習提供支持的電子設計自動化工具)快速且信心滿滿地實現他們的定制設計。

所有這些都便于系統架構師和硬件開發人員立即啟動設計測試,并加速產品上市進程。

即刻訂購 Versal HBM 自適應 SoC

Versal HBM 自適應 SoC 現已投入量產,準備好為新一代計算密集型應用提供支持。與分立式存儲器解決方案相比,這些自適應 SoC 可提供高達 6 倍的內存帶寬1,以及在更小型的封裝內2將功耗降低多達 65%3。我已經迫不及待地想看到它們將如何幫助實現新興網絡通信協議、尖端 AI 等眾多應用。

立即開始評估,并加速產品上市進程。聯系銷售人員或了解有關 Versal HBM 自適應 SoC 的更多信息。

上下滑動查看

1

根據 AMD 在 2023 年 5 月開展的內部分析,將內置 HBM2E 的 Versal HBM VH1542 器件與帶有 4 個 LPDDR4-4266 組件的 Versal Premium VP1502 實現方案進行了比較。配置可能會有所不同,因此產生不同的結果。VER-12。

2

根據 AMD 在 2023 年 5 月開展的內部分析,將假設帶有 24 個 LPDDR4-4266 組件的 Versal Premium VP1502 器件實現方案與單個 Versal HBM VH1542 器件進行了比較。配置可能會有所不同,因此產生不同的結果。VER-14。

3

根據 AMD 在 2023 年 5 月開展的內部分析,將單個內置 HBM2E 的 Versal HBM VH1542 器件與帶有 4 個 LPDDR4-4266 組件的 Versal Premium VP1502 器件實現方案進行了比較。假設使用 40% 的讀/寫事務進行順序內存訪問。功耗計算結果使用 AMD Power Design Manager 和第三方系統功耗計算器生成。配置可能會有所不同,因此產生不同的結果。VER-13。

4

參見 UltraScale+ FPGA 產品選擇指南 (XMP103) 和 Versal HBM 系列產品選擇指南 (XMP465)。

5

根據 AMD 在 2023 年 6 月開展的內部分析,將帶有 GTYP 和 GTM 收發器的 Versal HBM VH1782 器件與帶有 GTY 收發器的 Virtex UltraScale+ HBM VU47P 器件進行了比較。配置可能會有所不同,因此產生不同的結果。VER-17。

2023 年超威半導體公司版權所有。保留所有權利。AMD、AMD Arrow 標識、UltraScale+、Versal、Virtex、Vivado 及其組合是超威半導體公司的商標。PCIe 是 PCI-SIG 公司的商標。本文中使用的其它產品名稱僅用于識別目的,可能是其各自所有者的商標。

原文標題:AMD Versal HBM 自適應 SoC 已投入量產

文章出處:【微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

-

賽靈思

+關注

關注

33文章

1798瀏覽量

133435 -

Xilinx

+關注

關注

73文章

2200瀏覽量

131139

原文標題:AMD Versal HBM 自適應 SoC 已投入量產

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

使用Aurora 6466b協議實現AMD UltraScale+ FPGA與AMD Versal自適應SoC的對接

AMD Vivado Design Suite 2025.2版本現已發布

AMD Versal自適應SoC內置自校準的工作原理

AMD Vivado IP integrator的基本功能特性

如何在AMD Vitis Unified 2024.2中連接到QEMU

在AMD Versal自適應SoC上使用QEMU+協同仿真示例

AMD Power Design Manager 2025.1現已推出

基于AMD Versal器件實現PCIe5 DMA功能

AMD Spartan UltraScale+ FPGA 開始量產出貨

AMD第二代Versal AI Edge和Versal Prime系列加速量產 為嵌入式系統實現單芯片智能

利用AMD VERSAL自適應SoC的設計基線策略

Versal 600G DCMAC Subsystem LogiCORE IP產品指南

適用于Versal的AMD Vivado 加快FPGA開發完成Versal自適應SoC設計

第二代AMD Versal Premium系列SoC滿足各種CXL應用需求

面向AI與機器學習應用的開發平臺 AMD/Xilinx Versal? AI Edge VEK280

AMD Versal HBM 自適應 SoC 已投入量產

AMD Versal HBM 自適應 SoC 已投入量產

評論