電感下方到底要不要鋪銅?

電感是一種常見的電子元器件,它主要由一個線圈構成,用來儲存電能,調節電路的頻率等等。在使用電感的時候,我們可能會遇到這樣一個問題,就是電感下方是否要鋪銅,這個問題其實是具有爭議的,下面我們來詳細介紹一下這個問題。

一、電感下方是否要鋪銅的爭議

在使用電感時,很多人都會將電感下方鋪上銅,以提高電路的效率。但同時也有不少人認為,鋪銅會讓電路中的噪音信號變得更強,從而影響電路的信噪比,因此不應該鋪銅。這兩種認識都有一定的道理,下面我們來詳細講解一下。

二、鋪銅的優點

1. 提高電路的導電性能

在電路設計中,為了提高導電性能,很多人會考慮將電感下方鋪上一層銅。因為銅本身具有優良的導電性能,它可以加速電路中信號的傳遞速度,從而提高電路的響應速度。此外,銅還可以降低電路的電阻,減小電路的功耗,從而提高電路的效率。

2. 防止電磁干擾

在使用電路時,可能會受到一些電磁干擾,這些干擾會降低電路的信噪比,影響電路的性能。由于電感下方鋪上銅可以形成一種屏蔽效應,阻擋這些干擾信號的入侵,從而確保電路的穩定性和可靠性。

3. 增加散熱面積

由于電感工作時會產生一定的熱量,如果沒有及時散熱,就會導致電感溫度過高,從而影響電路的性能。因此,在一些設計中,會選擇在電感下方鋪上一層銅,以增加散熱面積,提高電感的散熱效果,保證電路的安全性和穩定性。

三、不鋪銅的優點

1. 降低信噪比

雖然鋪銅可以提高電路的導電性能,但同時也會增加電路中的噪音,影響電路的信噪比。因此,在一些對信號干擾要求較高的電路中,不建議在電感下方鋪銅。

2. 影響電感的品質因數

電感的品質因數是衡量電感性能的重要指標之一,它可以反映電感的能量儲存能力。如果在電感下方鋪上銅,會影響電感周圍磁場的分布,從而降低電感的品質因數,影響電路的性能。

3. 增加磁耦合

電感下方的銅鋪面會增加電路的磁耦合,從而使電路發生不可預測的變化,影響電路的穩定性。特別是在一些高精度的電路中,這種問題可能會非常嚴重,甚至影響電路的正常運行。

四、結論

通過上文的分析,我們可以得出一個初步的結論:在使用電感時,是否要在電感下方鋪銅,要根據具體情況而定。如果僅僅是為了提高導電性能和散熱效果,可以適當鋪銅,但要注意對信噪比的影響。如果對信號干擾要求較高,或者需要保持電感的高品質因數,則應該不鋪銅。總之,要在不同需求之間權衡,選擇最適合的方案。

-

電感器

+關注

關注

20文章

2650瀏覽量

73844 -

信噪比

+關注

關注

3文章

272瀏覽量

29684 -

電磁干擾

+關注

關注

36文章

2494瀏覽量

108017

發布評論請先 登錄

車規級射頻連接器采購:IATF16949 認證到底要不要卡?

銘普銅鐵共燒電感如何破局高端供電

射頻PCB的“隱形殺手”:90%的工程師都忽視的鋪銅細節!

高速PCB工程師必看:用仿真三步法,讓鋪銅從“隱患”變“保障”

關于DC電路板的GND要不要接金屬外殼的問題,以下那個是對的?

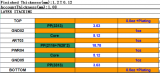

銅厚、絕緣層、結構……哪些因素影響銅基板價格?

高速PCB鋪銅到底怎么鋪

電感下方到底要不要鋪銅?

電感下方到底要不要鋪銅?

評論