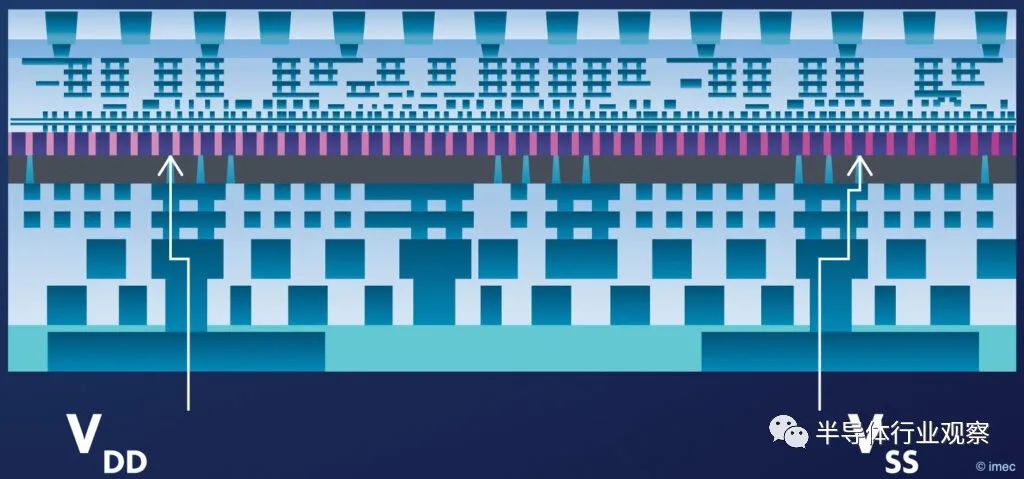

背面電力傳輸打破了在硅晶圓正面處理信號和電力傳輸網絡的長期傳統。通過背面供電,整個配電網絡被移至晶圓的背面。硅通孔 (TSV) 將電源直接從背面傳送到正面,而無需電子穿過芯片正面日益復雜的后道工序 (BEOL) 堆棧。

圖 1:背面電力傳輸網絡的示意圖,允許將電力傳輸與信號網絡解耦。

下一代邏輯的游戲規則改變者

背面供電網絡 (BSPDN) 的目標是緩解邏輯芯片正面后端生產線 (BEOL) 的擁塞。此外,在標準單元層面,它承諾通過設計技術協同優化(DTCO)更有效地安排互連。這將有助于進一步縮小邏輯標準單元的尺寸。系統級也有望受益,系統級日益受到功率密度上升和電源電壓(或 IR)急劇下降的影響。由于背面供電互連可以做得更大、電阻更小,因此 BSPDN 被認為可以顯著降低片上 IR 壓降。這將有助于設計人員保持穩壓器和晶體管之間允許的 10% 功率損耗裕度。此外,

2019年,imec率先提出了背面供電的概念,并與Arm合作量化了系統層面的優勢。與此同時,BSPDN 已作為 2nm 及以上技術節點的上下文感知互連解決方案進入imec 的路線圖。最近,一些主要芯片制造商宣布在其下一代邏輯技術的商業制造工藝中引入背面配電。

具體 BSPDN 案例:nTSV 落在埋地電源軌上

BSPDN 給芯片處理帶來了新的工藝步驟和集成挑戰,包括例如基板極度減薄、微米或納米 TSV 處理、背面到正面對準以及背面處理對有源前端生產線器件的影響。E. Beyne 等人在 2023 年 VLSI 邀請論文中回顧了這些集成流程及其挑戰。

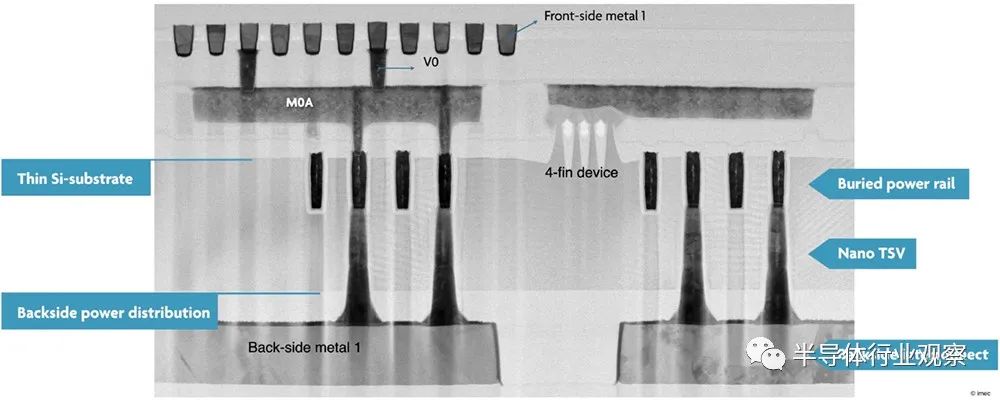

通過實施這些工藝步驟,imec 實驗性地演示了 BSPDN 的一種具體實施方式:背面供電與埋入式電源軌 (BPR) 相結合,如 VLSI 2022 所示。BPR 是嵌入芯片前端深處的垂直金屬化層。離線,與標準電池并行運行。imec 使用這些 BPR 將按比例縮放的 FinFET 器件連接到背面和正面。功率從背面通過 320nm 深的 nTSV 以 200nm 的緊密間距落在 BPR 上,而不占用標準單元的任何面積。背面處理不會對 FinFET 器件的前端性能產生負面影響。

圖 2:TEM 圖像顯示連接到晶圓背面和正面的按比例縮小的 FinFET (VLSI 2022)。

塊級評估:高密度與高性能案例

雖然上述工作著眼于標準單元級別的 BSPDN 和晶體管的連接性,但imec 和 Arm 已采取下一步:縮小到塊級別(代表集成電路的較大部分),其中的好處BSPDN 可以得到充分收獲。他們調查了與前端 PDN 實施相比,BSPDN + BPR 實施是否可以在塊級別提高電源完整性。

通過設計技術協同優化 (DTCO) 進行的塊級評估可以評估片上 IR 壓降,這是量化功率傳輸性能的主要指標。它還通過量化 PDN 對功耗、性能和面積 (PPA) 的影響,提供有關 PDN 對集成電路的侵入程度的信息。該研究還揭示了如何調整某些旋鈕以針對特定操作條件優化 PDN。

事實證明,在高密度邏輯操作條件下,基于 BSPDN 的設計的性能優于前端 PDN 設計。在高密度邏輯中,設計經過優化,可最大限度地節省功耗并減少面積。對于基于納米片的器件架構,這可以通過保持納米片的寬度盡可能小來實現。但迄今為止,高性能邏輯的收益從未被量化。高性能邏輯的目標是快速開關和高驅動電流,實現通常具有更大片寬度和閾值電壓的納米片器件。功率密度要求甚至比高密度邏輯更為嚴格,因此,BSPDN 的優勢預計將更具影響力。

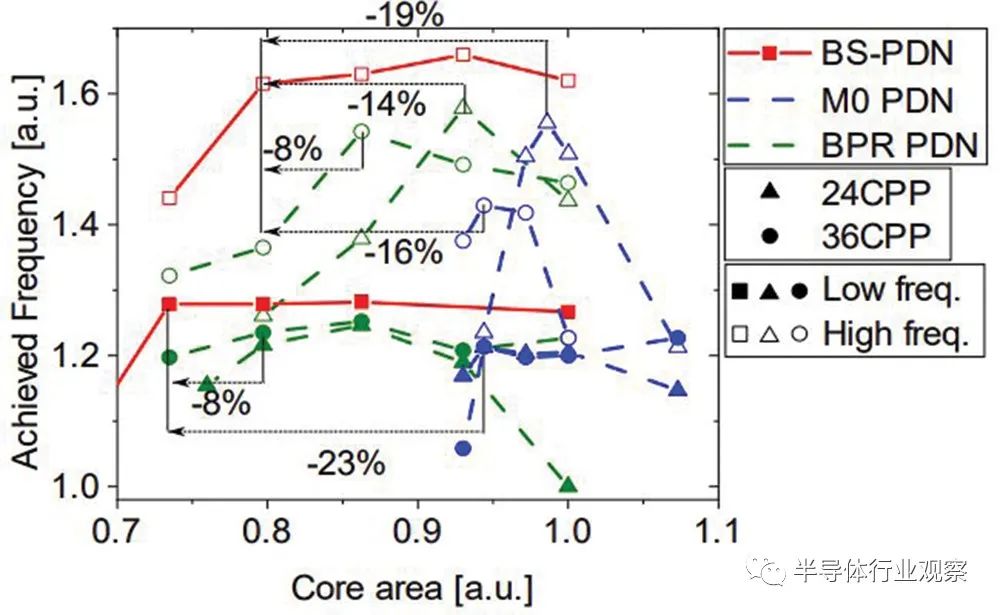

BSPDN + BPR:塊級 PPA 助推器

在 VLSI 2023 上發表的一篇論文中,imec 和Arm評估了 (BS)PDN 對 Arm 商用高性能 64 位處理器模塊的影響。我們評估了三種不同的 PDN 實現:傳統的前端實現、具有前端連接的埋地電源軌,以及帶有 nTSV 落在埋地電源軌上的背面電力傳輸網絡。開發了高性能的imec A14納米片工藝設計套件(PDK),以保證高性能計算模塊的實際實現。內部開發的分析模型與物理設計框架結合使用,以實現塊級 PPA 評估和 IR 壓降驗證。

與前端 PDN 相比,BSPDN 同時實現了 6% 的頻率和 16% 的面積改進,并且在能耗方面沒有任何缺點。與實施具有前端連接的 BPR 相比,BSPDN 的頻率提高了 2%,面積縮小了 8%,能耗降低了 2%。

圖 3:BSPDN (BS-PDN) 與兩種前端實現(M0 PDN;BPR PDN)之間的核心面積比較,適用于寬松節距 (36CPP) 和緊節距 (24CPP) 以及低和高目標頻率。BSPDN 在表現出性能下降之前到達較小的核心區域(如 VLSI 2023 中所示)。

研究人員為 IR 壓降評估確定了 35mV 的最大允許功率損耗,相當于標稱電源電壓 (V DD + V SS ) 的 10%。對于 BSPDN 實施,該目標是通過寬松的 nTSV 節距(4-6μm)實現的,代表“分接”功率的節距。然而,對于這兩種前端選項,這一目標只能通過非常緊密的 PDN 間距(或小 CPP)來實現,從而對處理器的性能產生負面影響。

imec 團隊還研究了如何進一步提高 BSPDN 外殼的電源完整性,例如通過更改 nTSV 所用的材料。當使用 Ru 代替 W 時,由于 nTSV 電阻得到改善,IR 壓降可進一步降低 23%。

簡而言之,BSPDN 作為塊級 PPA 增強器和 IR 壓降減小器的潛力可以在高性能計算環境中得到充分發揮。

標準單元級背面連接選項

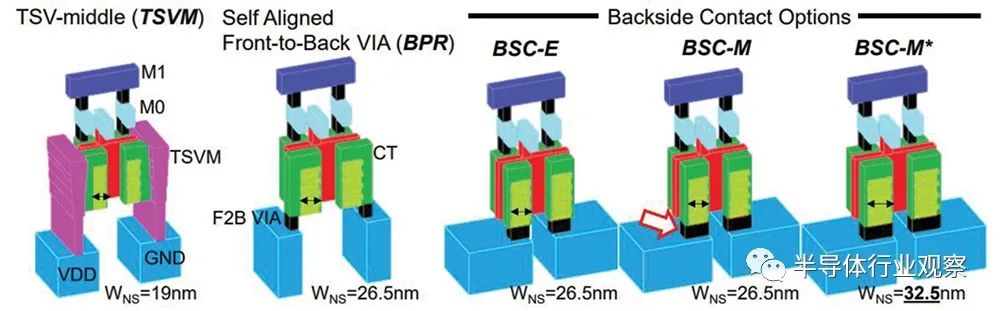

到目前為止,研究人員只討論了 BSPDN 的一種實現方式,其中通過位于 BPR 上的 nTSV 將電力從背面傳送到正面。從 BPR 開始,一個小過孔連接到中線 (M0A) 金屬化的底部,以訪問標準單元級的晶體管。

除了這種“BPR”方法之外,研究人員還在探索在標準單元級別實現背面電源連接的其他選項。在 VLSI 2023 上,imec 討論了另外兩種用于訪問納米片晶體管的連接方案。在 TSV 中間方法 (TSVM) 中,中間的高過孔將背面 metal-1 連接到 M0A 金屬的側面,而無需埋入電源軌。在第三個也是更高級的選項中,通孔將納米片的源極-漏極外延的底部直接連接到背面metal 1。這種直接背面連接選項 (BSC) 存在三種類型,主要區別在于接觸區域的大小。在 BSC-E (epi BSC) 中,過孔僅連接到源漏外延的底部,而在 BSC-M 中,過孔還連接到金屬接觸。

圖 4 – 各種連接選項的模擬結構:TSVM、BPR 和三種風格的 BSC(如 VLSI 2023 上介紹的)。【藍色=電源和參考電壓(VDD+VSS);淺藍色=中間層M0;深藍色=BEOL金屬-1;黑色=通孔;紅色=門;淺綠色=活性納米片和電介質隔離;深綠色=金屬接觸(CT)]。

各種連接方案具有不同的屬性(例如 WNS),對標準單元的電氣性能和擴展潛力具有不同的影響。一般來說,當從 TSVM 轉向 BPR 和 BSC 時,方案變得越來越緊湊,集成起來也更具挑戰性。然而,研究人員預計,隨著邏輯路線圖的進一步擴展,更大的集成復雜性將被更大的 PPA 增益所抵消。

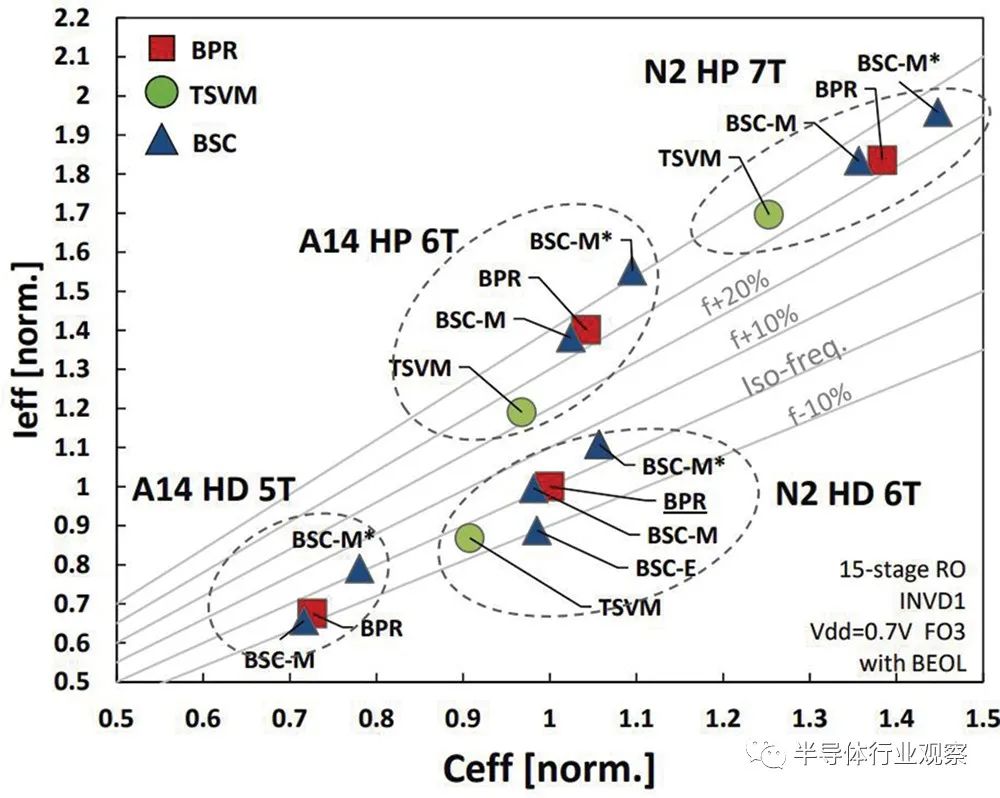

邁向直接背面連接

在 VLSI 2023 上,imec 量化了高密度(2nm、6T;A14、5T)和高性能(2nm 7T;A14 6T)邏輯的 2nm 和 A14 納米片技術中不同背面電源選項的 PPA 和擴展潛力條件。性能評估的主要指標是環形振蕩器的模擬頻率,表示為有效驅動電流與有效電容之比 (I eff /C eff )。

對于 2nm 節點的高性能邏輯,對于最大的 7T 標準單元,不同連接選項之間的頻率幾乎沒有任何差異。然而,當擴展到 A14 時,TSVM 方法仍然適用于 6T 設計,但運行速度比 BPR 等慢 8.5%。總體而言,BSC-M* 明顯優于其他選項(例如,比 BPR 快 5%)。

對于 2nm 節點的高密度邏輯,其軌道高度 (6T) 比高性能邏輯更小,不同選項的頻率之間的差異變得更加明顯。當擴展到A14和5T時,TSVM不再是可行的選擇,只考慮BPR和BSC。BPR 和 BSC-M* 之間片材寬度的相對差異現在比 2nm 更大,這使得 BSC-M* 成為明顯的贏家(比 BPR 快 8.9%)。

圖 5:高性能邏輯(N2、7T;A14、6T)和高密度邏輯(N2、6T;A14、5T)系列的各種連接選項的模擬環形振蕩器頻率(如 VLSI 2023 上所示)。

綜上所述,雖然 TSVM 占用更多空間,但對于較大單元(例如 2nm 7T 邏輯)來說,它仍然是一個不錯的選擇。然而,BPR 和 BSC 在尺寸和電氣方面具有更好的擴展潛力。由于納米片寬度和接觸面積比其他選項更大,直接背面接觸 BSC-M* 型顯然是小軌道高度的贏家。然而,對于 BSC-M*,應權衡性能提升與更大的集成挑戰。

imec 團隊目前正在致力于不同背面連接選項的技術演示,并與 Arm 合作進行塊級 PPA 評估。

超越背面供電

雖然硅晶圓的背面長期未使用,但利用背面的第一個實例將是用于電力傳輸。與此同時,imec 及其行業合作伙伴也在探索哪些其他功能也可以遷移到背面。例如,考慮全局互連和時鐘信號分配。雖然電力傳輸是一種非常特殊的互連類型,針對最小電阻進行了優化,但分配時鐘或其他類型的信號可能具有不同的屬性,從而改變了背面的尋址方式。Imec 目前正在研究這種功能性背面(或背面 2.0)可能帶來哪些挑戰和機遇。

審核編輯:劉清

-

處理器

+關注

關注

68文章

20255瀏覽量

252311 -

晶體管

+關注

關注

78文章

10396瀏覽量

147768 -

電源完整性

+關注

關注

9文章

226瀏覽量

21966 -

FinFET

+關注

關注

12文章

260瀏覽量

92259 -

TSV技術

+關注

關注

0文章

17瀏覽量

5794

原文標題:背面供電,imec的玩法

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

在Termux環境下實現康威生命游戲

英飛凌下一代電磁閥驅動器評估套件使用指南

Amphenol Aerospace高壓38999連接器:滿足下一代飛機電力需求

Amphenol Multi-Trak?:下一代高速互連解決方案

Microchip推出下一代Switchtec Gen 6 PCIe交換芯片

Telechips與Arm合作開發下一代IVI芯片Dolphin7

用于下一代 GGE 和 HSPA 手機的多模式/多頻段功率放大器模塊 skyworksinc

適用于下一代 GGE 和 HSPA 手機的多模/多頻段 PAM skyworksinc

下一代高速芯片晶體管解制造問題解決了!

下一代PX5 RTOS具有哪些優勢

NVIDIA 采用納微半導體開發新一代數據中心電源架構 800V HVDC 方案,賦能下一代AI兆瓦級算力需求

InspireSemi借助Cadence解決方案為下一代AI鋪路

下一代高速銅纜鐵氟龍發泡技術

背面電力傳輸 下一代邏輯的游戲規則改變者

背面電力傳輸 下一代邏輯的游戲規則改變者

評論