1、異步復(fù)位同步釋放

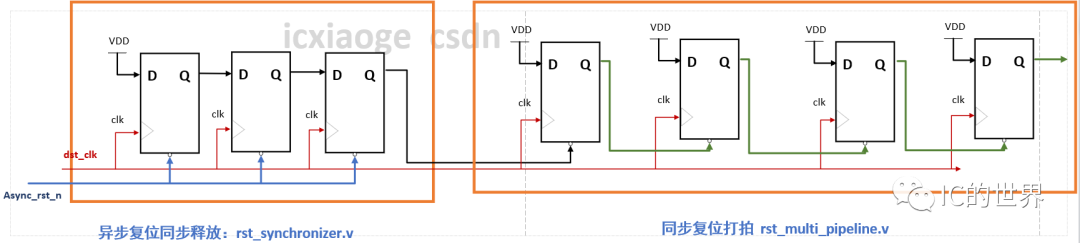

異步復(fù)位同步釋放:rst_synchronizer.v

采用3級同步打拍模塊

異步復(fù)位async_rst_n連接到3級同步寄存器復(fù)位端

時(shí)鐘采用目的時(shí)鐘dst_clk

第一個(gè)寄存器輸入D端接高電平,Q端驅(qū)動下一級寄存器的D端,

最后一級reg的Q端就是作為模塊輸出的已同步到dst_clk時(shí)鐘域的復(fù)位信號

模塊特點(diǎn):

采用3級同步器減少亞穩(wěn)定發(fā)生概率(7nm,5nm時(shí)鐘頻率一般在1GHz左右會采用3級同步器)

一般設(shè)計(jì)會采用定制模塊實(shí)現(xiàn),保證3級寄存器的上一級Q端和下一級D端延時(shí)很小

2、同步復(fù)位打拍模塊 同步復(fù)位同步打拍:rst_multi_pipeline.v

采用多個(gè)寄存器實(shí)現(xiàn)

所有寄存器輸入D端接高電平

輸出q端作為復(fù)位連接到下一級寄存器的復(fù)位端rst_n

首個(gè)寄存器復(fù)位端來自rst_synchronizer.v的輸出復(fù)位信號

模塊特點(diǎn):

采用多級寄存器同步打拍,便于時(shí)序收斂,布局布線以及增加驅(qū)動能力

采用多級寄存器打拍,還能便于芯片整理復(fù)位平衡的。

審核編輯:劉清

-

寄存器

+關(guān)注

關(guān)注

31文章

5611瀏覽量

130155 -

延時(shí)器

+關(guān)注

關(guān)注

1文章

36瀏覽量

16232 -

同步器

+關(guān)注

關(guān)注

1文章

117瀏覽量

15670 -

異步復(fù)位

+關(guān)注

關(guān)注

0文章

47瀏覽量

13692 -

CLK

+關(guān)注

關(guān)注

0文章

132瀏覽量

18066

原文標(biāo)題:異步復(fù)位同步釋放與同步復(fù)位打拍

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Xilinx FPGA異步復(fù)位同步釋放—同步后的復(fù)位該當(dāng)作同步復(fù)位還是異步復(fù)位?

異步復(fù)位同步釋放有多個(gè)時(shí)鐘域時(shí)如何處理 異步復(fù)位同步釋放的策略

異步復(fù)位異步釋放會有什么問題?FPGA異步復(fù)位為什么要同步釋放呢?

同步復(fù)位與異步復(fù)位,同步釋放的對比疑問

同步復(fù)位和異步復(fù)位有什么聯(lián)系與區(qū)別,優(yōu)缺點(diǎn)!

關(guān)于異步復(fù)位同步釋放理解與分析

如何區(qū)分同步復(fù)位和異步復(fù)位?

Xilinx FPGA的同步復(fù)位和異步復(fù)位

同步復(fù)位和異步復(fù)位電路簡介

同步復(fù)位與異步復(fù)位的區(qū)別

FPGA學(xué)習(xí)-異步復(fù)位,同步釋放

淺析異步復(fù)位同步釋放與同步復(fù)位打拍模塊

淺析異步復(fù)位同步釋放與同步復(fù)位打拍模塊

評論