電子發(fā)燒友網(wǎng)報(bào)道(文/周凱揚(yáng))隨著摩爾定律的失效或者說減弱已成定數(shù),除了穩(wěn)步發(fā)展半導(dǎo)體制造工藝外,半導(dǎo)體產(chǎn)業(yè)還涌現(xiàn)了不少繼續(xù)提高性能的方法,比如Chiplet技術(shù)。該技術(shù)將復(fù)雜的SoC芯片設(shè)計(jì)分解成模塊化的小芯片單元,再通過die-to-die(D2D)技術(shù)將其封裝在一起。

如此一來設(shè)計(jì)更高效的重復(fù)利用成為現(xiàn)實(shí),借助Chiplet設(shè)計(jì)芯片的廠商們不僅降低了成本,也極大加快了產(chǎn)品上市周期,更可以改善大型單片SoC的良率。當(dāng)下Chiplet無論是從設(shè)計(jì)還是制造,以及標(biāo)準(zhǔn)化上都擁有了較為成熟的生態(tài),從這些生態(tài)中我們也可以看出為何越來越多的SoC選擇Chiplet設(shè)計(jì)。

EDA與IP

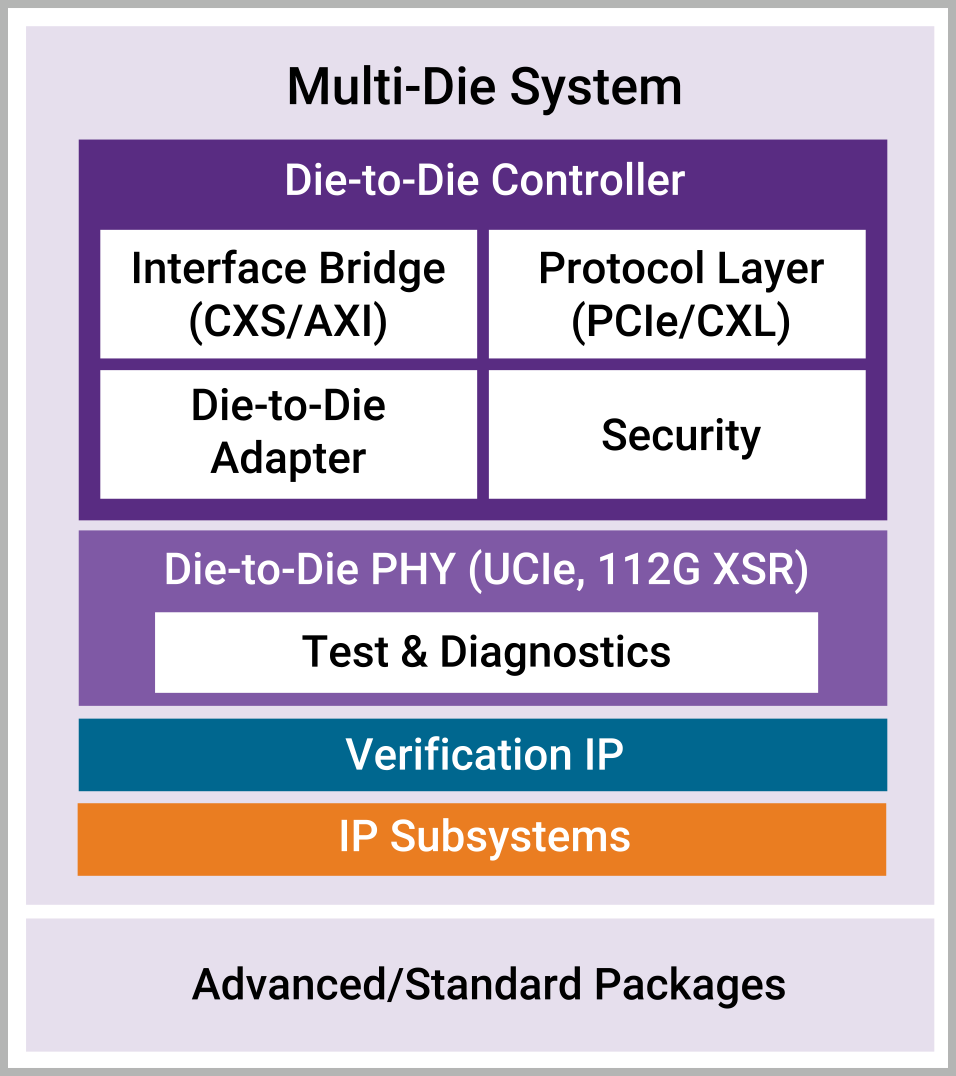

要說Chiplet生態(tài)除了造福下游一眾初創(chuàng)半導(dǎo)體企業(yè)外,也帶動(dòng)了EDA與IP廠商的創(chuàng)新和發(fā)展,甚至說他們是直接受益人也不為過。從IP廠商來說的話,目前被Chiplet生態(tài)中利用最多的莫過于接口IP的Chiplet,比如新思等IP廠商的產(chǎn)品。同時(shí),類似以太網(wǎng)等接口IP往往無需用到最先進(jìn)的工藝,很適合用于節(jié)省芯片整體成本。

Designware多Die系統(tǒng)解決方案 / 新思

像Blue Cheetah這樣的IP廠商,也推出了為Chiplet定制的D2D互聯(lián)IP方案BlueLynx,支持到5nm、7nm、12nm和16nm的工藝節(jié)點(diǎn),且不少Tier1和初創(chuàng)企業(yè)都將該方案用于其數(shù)據(jù)中心、網(wǎng)絡(luò)和AI芯片中。

至于相關(guān)通用計(jì)算類IP在公開Chiplet化的進(jìn)度上仍較為落后,畢竟這類IP往往是各大廠商最強(qiáng)競(jìng)爭(zhēng)力的體現(xiàn)。擁有足夠優(yōu)秀IP的廠商往往會(huì)選擇自研產(chǎn)品,而不是拿出來供市場(chǎng)公開重復(fù)利用。但RISC-V架構(gòu)下的IP廠商倒是對(duì)此更加開放,而Arm也有心將其用于特定的應(yīng)用中去,比如服務(wù)器CPU。

而EDA廠商目前對(duì)Chiplet生態(tài)的參與度也相當(dāng)高,包括新思、Cadence這些本身就有IP業(yè)務(wù)的廠商在內(nèi),本身就有著全流程的EDA工具,自然也都早早參與到Chiplet生態(tài)的建設(shè)中來。與此同時(shí),多個(gè)Chiplet設(shè)計(jì)的分層測(cè)試、診斷維護(hù)以及全面檢測(cè)功能也屬于EDA廠商的重心,畢竟這對(duì)于制造難易程度和長(zhǎng)期系統(tǒng)可靠性來說至關(guān)重要。

而國(guó)產(chǎn)EDA廠商在Chiplet設(shè)計(jì)上的進(jìn)度就有些慢了,目前絕大多數(shù)國(guó)產(chǎn)EDA廠商并沒有提供Chiplet對(duì)應(yīng)的方案,已知開始Chiplet相關(guān)技術(shù)研發(fā)的公司包括華大九天、合見工軟等廠商,考慮到國(guó)內(nèi)EDA廠商對(duì)這類先進(jìn)封裝方案的研究尚處于開始階段,也需要更多的時(shí)間積累才有概率趕上國(guó)際大廠。

制造與封裝

同樣在半導(dǎo)體制造端,絕大多數(shù)廠商都已經(jīng)開啟了Chiplet的進(jìn)程,出貨量也在逐漸上升,對(duì)于他們來說對(duì)Chiplet的支持反而會(huì)給他們帶來更多的訂單。以臺(tái)積電為例,Chiplet對(duì)于他們來說就是一個(gè)與3D堆疊技術(shù)完美結(jié)合的方案。

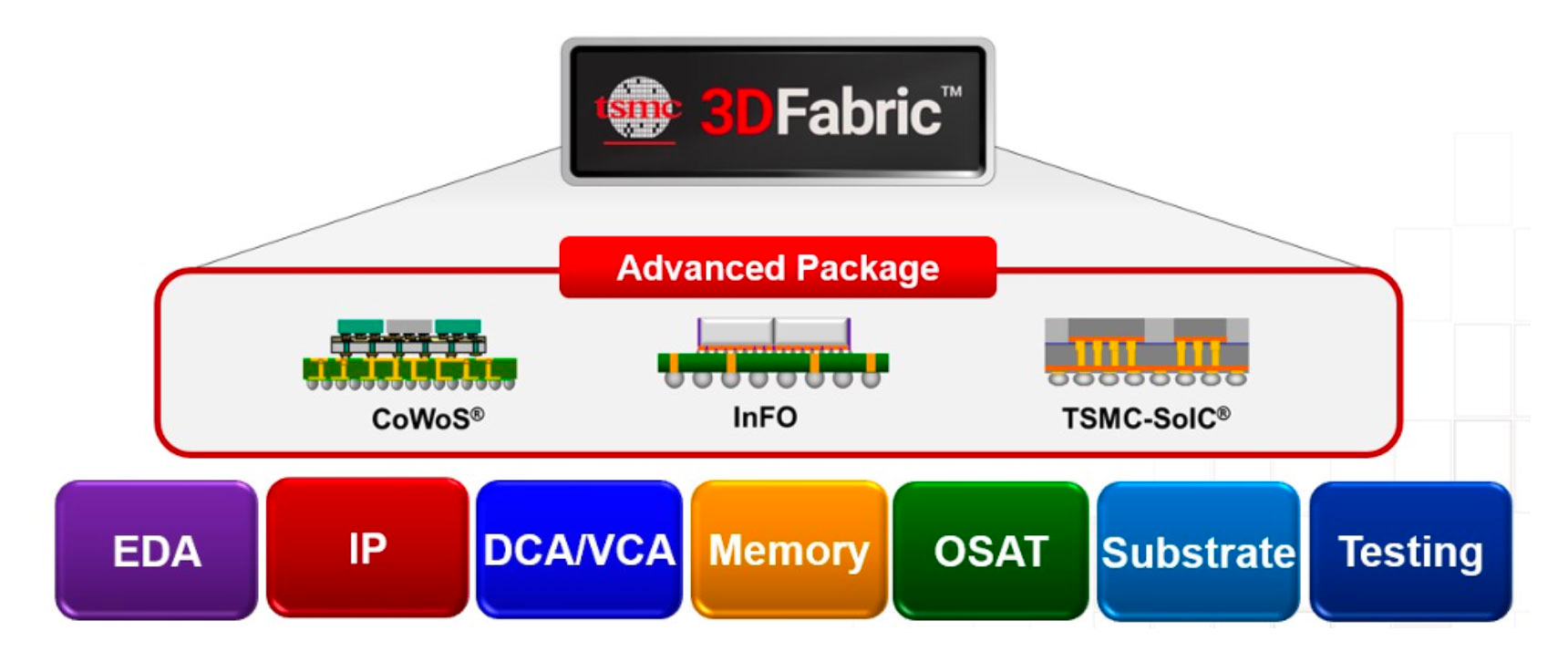

為此,臺(tái)積電于去年在其OIP合作伙伴生態(tài)下,成立了新的3DFabric聯(lián)盟,拉攏EDA/IP、DCA/VCA、內(nèi)存、OAST、基板與測(cè)試廠商,一同推進(jìn)Chiplet生態(tài)的發(fā)展。像AMD這樣的廠商,早就和臺(tái)積電合作打造了基于3D Chiplet技術(shù)的CPU和APU產(chǎn)品。

3DFabric聯(lián)盟 / 臺(tái)積電

除了3DFabric的3D堆疊和先進(jìn)封裝技術(shù)外,臺(tái)積電還和EDA廠商合作打造了3Dblox這一標(biāo)準(zhǔn),用于統(tǒng)一設(shè)計(jì)工具的工作流,讓客戶在臺(tái)積電的平臺(tái)上進(jìn)行3D Chiplet IC設(shè)計(jì)時(shí),擁有更高的靈活度和易用性。

與此同時(shí),Chiplet為封裝廠商創(chuàng)造了更多的機(jī)會(huì),即便是初創(chuàng)企業(yè)也都有機(jī)會(huì)參與到最先進(jìn)的半導(dǎo)體制造流程中來。今年年初,長(zhǎng)電科技宣布其XDFOI Chiplet高密度多維異構(gòu)集成系列工藝已經(jīng)進(jìn)入穩(wěn)定量產(chǎn)階段,且同步實(shí)現(xiàn)國(guó)際客戶4nm節(jié)點(diǎn)的多芯片系統(tǒng)集成封裝產(chǎn)品出貨,最大可實(shí)現(xiàn)1500mm2的系統(tǒng)級(jí)封裝面積。

據(jù)長(zhǎng)電科技公布的數(shù)據(jù),其XDFOI Chiplet技術(shù)可以實(shí)現(xiàn)50μm以內(nèi)的中介層厚度,40μm的微凸點(diǎn)中心距,可以供客戶在更小的單位面積內(nèi)實(shí)現(xiàn)各種高密度工藝的集成,從而做到更小的封裝尺寸。至于國(guó)際客戶的4nm封裝訂單,則很有可能是來自某個(gè)高性能AI芯片。

再以周秀文、戴偉立夫婦二人和前長(zhǎng)電科技執(zhí)行副總裁韓丙濬2021年成立的Silicon Box為例。這家新加坡初創(chuàng)公司在近期宣布,他們耗資20億美元在本地建立的先進(jìn)半導(dǎo)體封裝廠正式開放,主打解決Chiplet互聯(lián)技術(shù)面臨的挑戰(zhàn)。

三大創(chuàng)始人的背景則足以證明了Chiplet的潛力,更何況周秀文早前就提出過Mochi這種模塊化芯片架構(gòu)的方案。且據(jù)CEO韓丙濬稱,早在工廠尚未完工之前,客戶就已經(jīng)開始排隊(duì)了。Silicon Box表示新封裝廠的成立加上其專有的次5μm級(jí)互聯(lián)技術(shù),將幫助AI、數(shù)據(jù)中心和電動(dòng)汽車等領(lǐng)域的客戶實(shí)現(xiàn)更快的芯片上市周期,同時(shí)保證他們的IP安全性。

目前已知公開有合作意向的客戶就包括了RISC-V AI芯片初創(chuàng)企業(yè)Tenstorrent,其兩大高層Jim Keller和Raja Koduri都在近期參觀了Silicon Box的新封裝廠。從Tenstorrent的產(chǎn)品路線圖來看,后續(xù)AI芯片中的Chiplet封裝很可能會(huì)交由Silicon Box完成。

聯(lián)盟與規(guī)范

當(dāng)然了,作為力求席卷行業(yè)的一個(gè)技術(shù),即便是不開源,也需要有一定的標(biāo)準(zhǔn)規(guī)范,比如上文中臺(tái)積電聯(lián)合EDA廠商推出的3Dblox。同時(shí)也需要行業(yè)個(gè)體和組織共同推動(dòng),比如UCIe聯(lián)盟。UCIe聯(lián)盟作為成立尚不足兩年的Chiplet標(biāo)準(zhǔn)聯(lián)盟,已經(jīng)吸引了一大批巨頭和初創(chuàng)企業(yè)的加入。

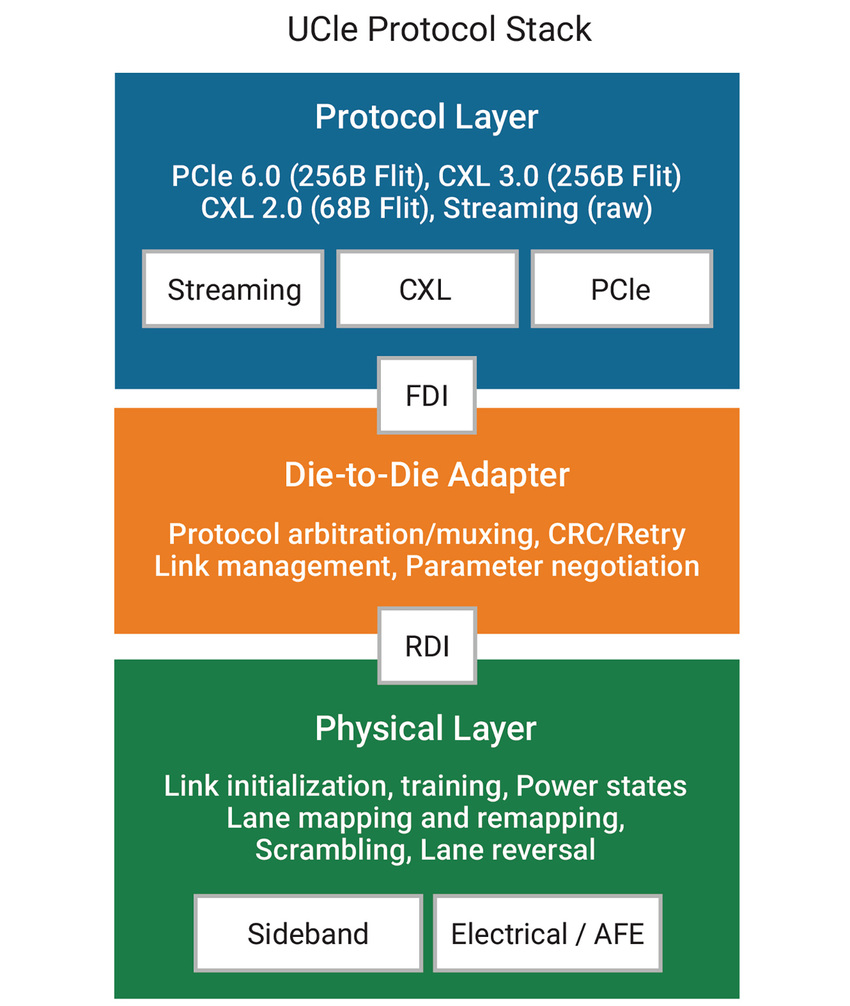

UCIe協(xié)議棧 / UCIe聯(lián)盟

在第一版UCIe 1.0規(guī)范中,聯(lián)盟定義了die-to-die I/O的物理層和協(xié)議,同時(shí)還有利用另外兩大行業(yè)標(biāo)準(zhǔn)PCIe和CXL的軟件棧模型。不過第一版僅僅只針對(duì)的是2D和2.5D的芯片封裝,并沒有對(duì)一些3D die-to-die 技術(shù)提供定義,畢竟這類3D封裝技術(shù)還是僅限于部分先進(jìn)制造廠商,且技術(shù)路線各有不同,但UCIe聯(lián)盟仍在進(jìn)行相關(guān)的努力。

不過即便是只有2D和2.5D封裝,UCIe也展現(xiàn)出了可觀的帶寬性能,根據(jù)今年ISC2023上公布的數(shù)據(jù),2D封裝下的Chiplet可以實(shí)現(xiàn)4通道73GB/s的帶寬,而2.5D封裝下的Chiplet可以實(shí)現(xiàn)32通道630GB/s的帶寬。這樣的密度意味著其能效要遠(yuǎn)遠(yuǎn)大于標(biāo)準(zhǔn)的PCIe 5.0板載連接。

近日,UCIe聯(lián)盟也終于發(fā)布了1.1版本的新規(guī)范,為Chiplet生態(tài)系統(tǒng)又帶來了一些改進(jìn),尤其是針對(duì)汽車行業(yè)。比如預(yù)測(cè)性失效分析和健康度檢測(cè)等,都是汽車這類高可靠性應(yīng)用中的關(guān)鍵特性。同時(shí),1.1版本還引入了新的凸點(diǎn)圖降低了封裝成本。相信隨著UCIe規(guī)范的發(fā)展,以及越來越多的公司加入這一聯(lián)盟,過去的共享IP池也能逐漸變?yōu)槲磥淼墓蚕鞢hiplet池。

寫在最后

即便Chiplet技術(shù)對(duì)于整個(gè)行業(yè)來說,是又一次設(shè)計(jì)效率的蛻變,但我們也需要提防設(shè)計(jì)創(chuàng)新思維的僵化。未來基于第三方Chiplet打造的芯片會(huì)越來越多,卻很有可能依然打著“完全自研”的旗號(hào)。Chiplet的存在無疑讓設(shè)計(jì)公司對(duì)可靠IP的選擇變得更加靈活,避免了重復(fù)造輪子的問題,即便如此,我們還是應(yīng)該避免設(shè)計(jì)同質(zhì)化的問題,這樣對(duì)于市場(chǎng)多樣性和創(chuàng)新發(fā)展來說,也能起到更大的推進(jìn)作用。

-

chiplet

+關(guān)注

關(guān)注

6文章

495瀏覽量

13604

發(fā)布評(píng)論請(qǐng)先 登錄

TPS61042:高性能LED驅(qū)動(dòng)芯片的深度解析

擁抱Chiplet,大芯片的必經(jīng)之路

國(guó)產(chǎn)高性能ONFI IP解決方案全解析

AFM Microelectronics射頻微波MLCC領(lǐng)軍制造商

AD8353 RF增益模塊:高性能寬帶放大器的理想選擇

得一微電子受邀出席第四屆HiPi Chiplet論壇

芯片的制造過程---從硅錠到芯片

推薦高性能存儲(chǔ)psram芯片

從技術(shù)封鎖到自主創(chuàng)新:Chiplet封裝的破局之路

淺談Chiplet與先進(jìn)封裝

從焊錫膏到3D堆疊:材料創(chuàng)新如何重塑芯片性能規(guī)則?

ESP32-C3FH4:高性能物聯(lián)網(wǎng)芯片的卓越之選,智能門鎖安防等應(yīng)用

深入解析硅基光子芯片制造流程,揭秘科技奇跡!

Chiplet:芯片良率與可靠性的新保障!

從設(shè)計(jì)到制造,Chiplet何以成為高性能芯片設(shè)計(jì)的首選

從設(shè)計(jì)到制造,Chiplet何以成為高性能芯片設(shè)計(jì)的首選

評(píng)論