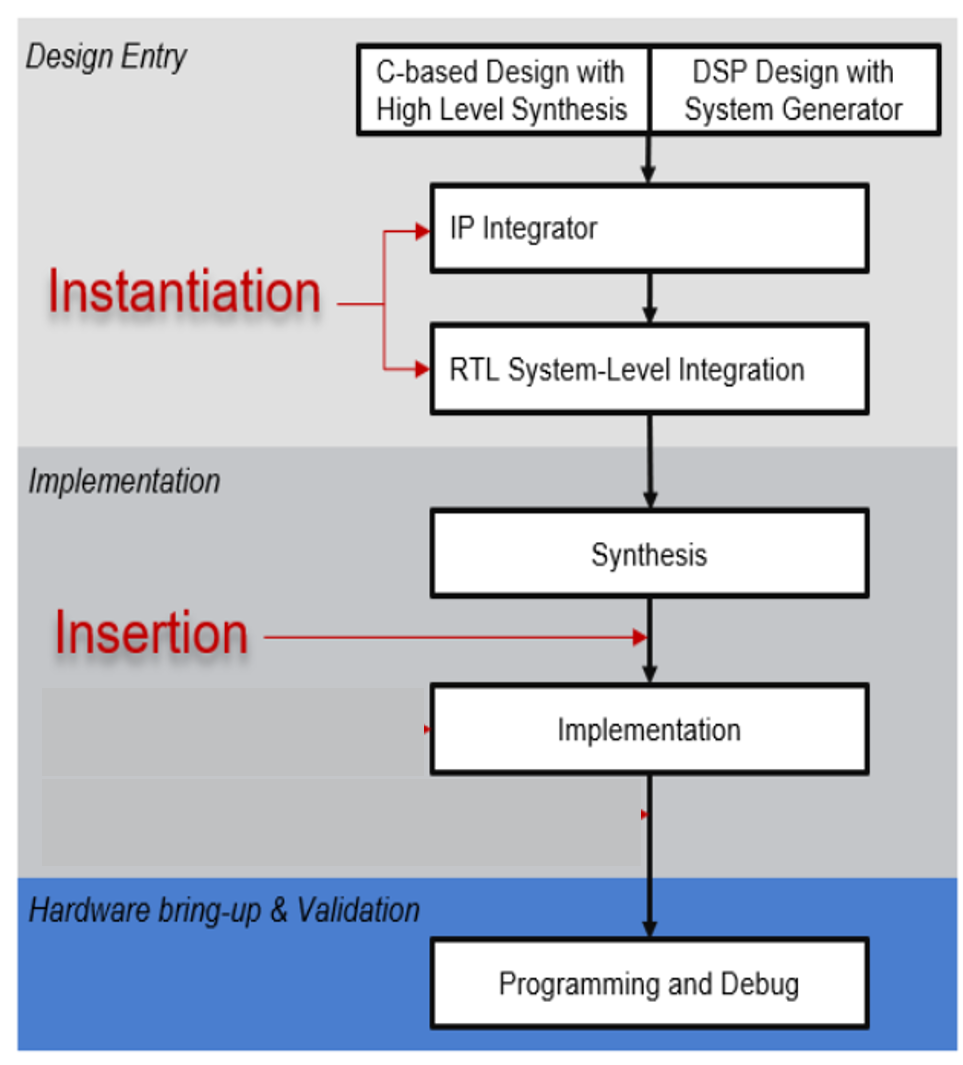

對(duì)傳統(tǒng)的非DFX設(shè)計(jì)進(jìn)行調(diào)試時(shí),一個(gè)重要環(huán)節(jié)是插入ILA(Integrated Logic Analyzer,集成邏輯分析儀)。可以采用如下圖所示的兩種方式。方式1是實(shí)例化方式,即在RTL代碼或者BD中實(shí)例化ILA。如果圖中紅色字體“Instantiation”所示。方式2是網(wǎng)表插入方式,即在綜合后的網(wǎng)表中插入ILA。

不難看出方式1是在綜合之前完成,而方式2則是在綜合之后完成。方式1需要手工例化ILA,同時(shí)將待測(cè)網(wǎng)線(xiàn)連接到ILA的測(cè)試端口,這個(gè)過(guò)程稍顯繁瑣,尤其是待測(cè)信號(hào)需要穿越多個(gè)層次到達(dá)ILA所在層次時(shí),但也確保了待測(cè)信號(hào)能夠百分之百被觀測(cè)到(不會(huì)被工具優(yōu)化掉)。方式2更為自動(dòng)化,在綜合后的網(wǎng)表中找到待測(cè)信號(hào)將其標(biāo)記為debug(本質(zhì)上是將其屬性mark_debug設(shè)置為true)。但有可能出現(xiàn)待測(cè)信號(hào)名字發(fā)生改變或者徹底被優(yōu)化掉而無(wú)法找到的情形。

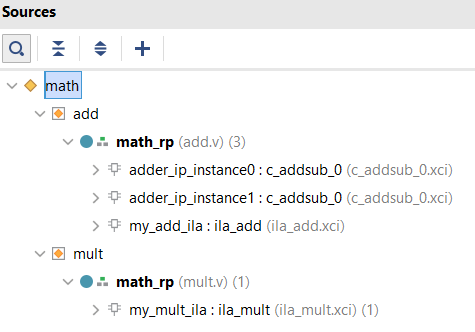

對(duì)于DFX設(shè)計(jì),那么就只能使用實(shí)例化方式插入ILA。但即便如此,仍有一些特殊之處。為便于說(shuō)明,我們看一個(gè)實(shí)際案例。這個(gè)DFX設(shè)計(jì)中的RP(Reconfigurable Partition)為math,該RP下有兩個(gè)RM(ReconfigurableModule),分別為add和mult,如下圖所示。

每個(gè)RM中均包含一個(gè)ILA。這個(gè)ILA無(wú)論參數(shù)配置是否一致,都要分別調(diào)用ILA IP Core,單獨(dú)例化。這是DFX設(shè)計(jì)所要求的,即每個(gè)IP都要以唯一的方式存在于RM中。

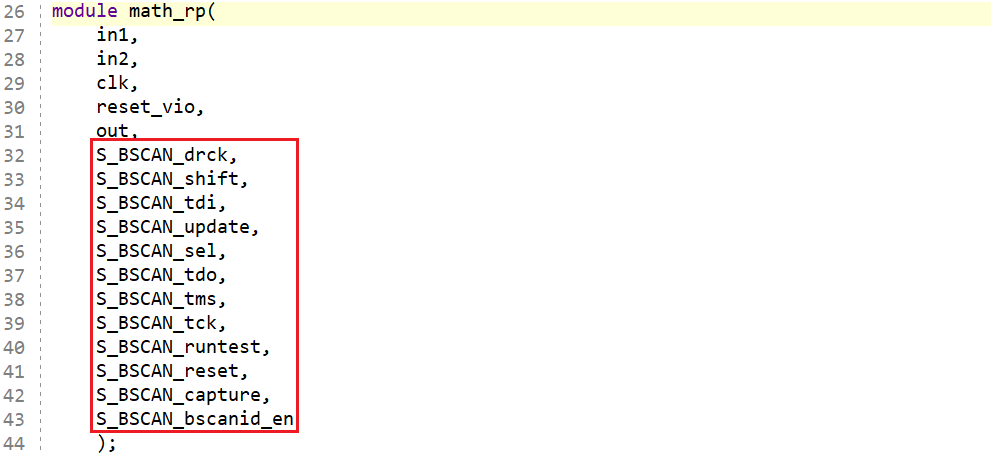

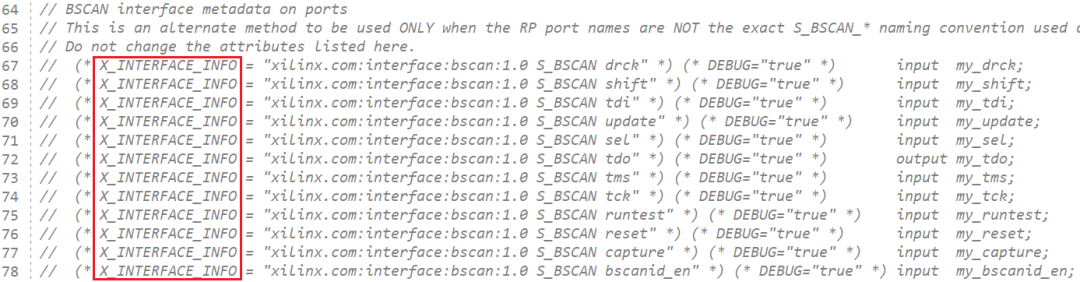

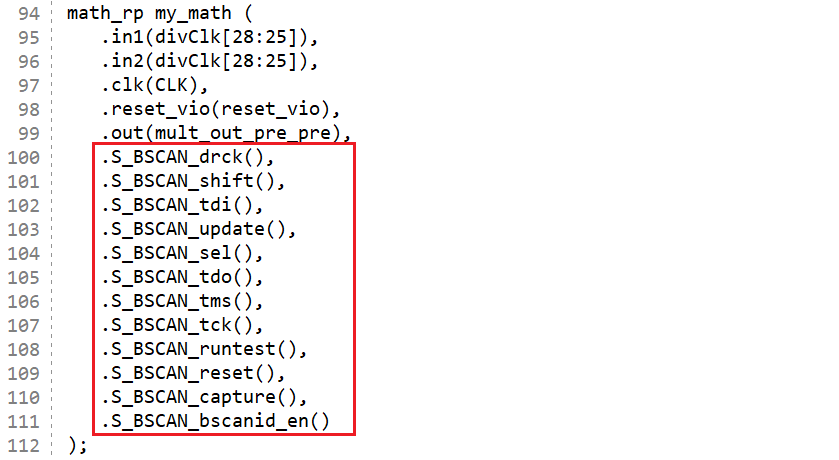

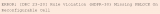

到這里我們看到的例化ILA的方式與傳統(tǒng)的非DFX設(shè)計(jì)并沒(méi)有什么不同。但是在每個(gè)RM的頂層,需要添加12個(gè)BSCAN端口,如下圖所示。這12個(gè)端口最終會(huì)與dbg_hub相連。這里要求端口名字必須與圖中紅色方框內(nèi)的名字完全一致,如果不一致,則要通過(guò)屬性X_INTERFACE_INFO設(shè)定。

在整個(gè)設(shè)計(jì)的頂層,對(duì)RM進(jìn)行實(shí)例化時(shí),這12個(gè)端口的端口映射為空,如下圖所示,如果使用的是VHDL,端口映射內(nèi)填寫(xiě)open。

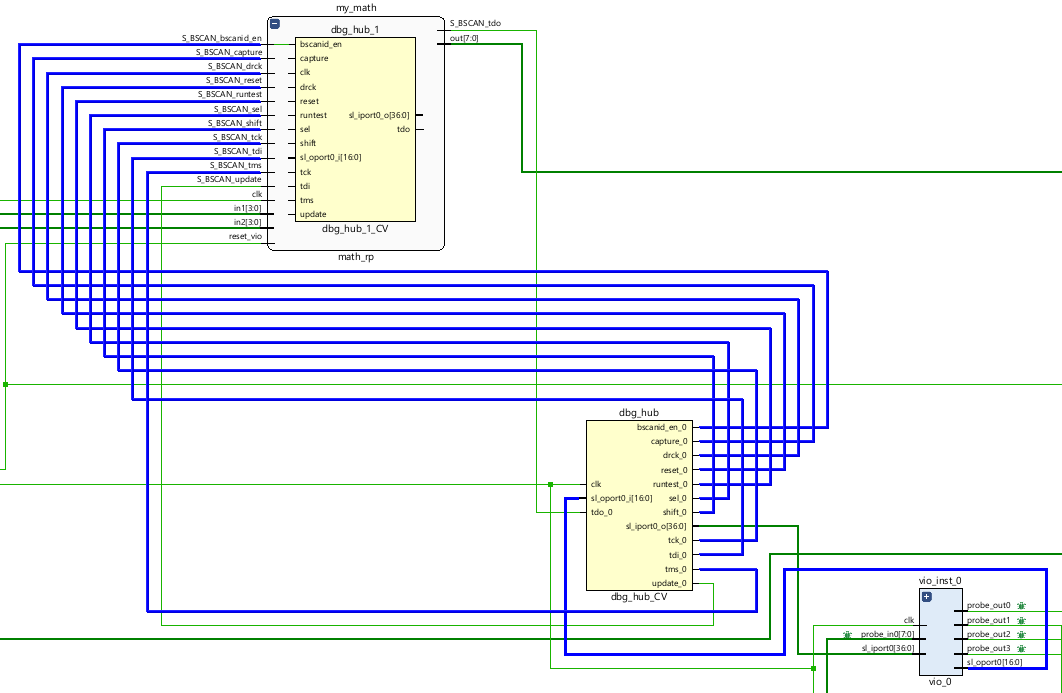

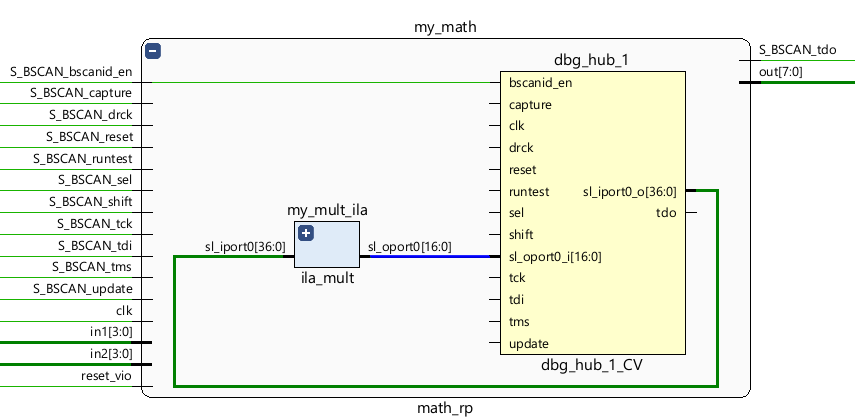

在綜合階段生成的網(wǎng)表中,dbg_hub是以黑盒子的形式存在,在設(shè)計(jì)頂層和RM內(nèi)分別有一個(gè)dbg_hub,如下圖所示。dbg_hub與ILA的連接關(guān)系由工具自動(dòng)處理,無(wú)需人工干預(yù)。

在綜合階段生成的網(wǎng)表中,dbg_hub是以黑盒子的形式存在,在設(shè)計(jì)頂層和RM內(nèi)分別有一個(gè)dbg_hub,如下圖所示。dbg_hub與ILA的連接關(guān)系由工具自動(dòng)處理,無(wú)需人工干預(yù)。

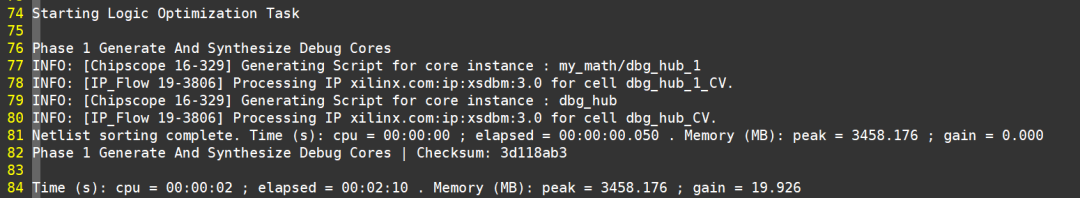

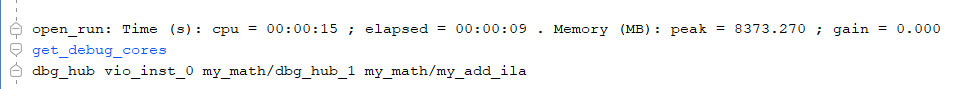

實(shí)際上,在opt_design階段,Vivado會(huì)自動(dòng)生成dbg_hub,這可在runme.log文件中查看到,如下圖所示。

打開(kāi)布線(xiàn)后的網(wǎng)表文件,執(zhí)行命令get_debug_cores,可以看到當(dāng)前網(wǎng)表中的ILA、VIO和dbg_hub。如下圖所示,設(shè)計(jì)頂層和RM中各有一個(gè)dbg_hub。

如果某個(gè)RM中并沒(méi)有使用ILA或VIO,而其他RM中至少有一個(gè)使用了ILA或VIO,那么所有的RM都要列出上文提到的12個(gè)BSCAN端口,以確保所有RM接口的一致性。

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

20316瀏覽量

254344 -

VHDL語(yǔ)言

+關(guān)注

關(guān)注

1文章

113瀏覽量

19455 -

RTL

+關(guān)注

關(guān)注

1文章

395瀏覽量

62832 -

VIO

+關(guān)注

關(guān)注

0文章

11瀏覽量

10668 -

DFx

+關(guān)注

關(guān)注

0文章

36瀏覽量

11153

原文標(biāo)題:如何對(duì)DFX設(shè)計(jì)進(jìn)行調(diào)試?

文章出處:【微信號(hào):Lauren_FPGA,微信公眾號(hào):FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

什么是DFX技術(shù)?DFX設(shè)計(jì)一定要執(zhí)行設(shè)計(jì)規(guī)則檢查嗎?

DFX設(shè)計(jì)如何分析

采用UltraScale/UltraScale+芯片的DFX設(shè)計(jì)注意事項(xiàng)

如何對(duì)傳統(tǒng)的非DFX設(shè)計(jì)進(jìn)行調(diào)試呢?

如何對(duì)傳統(tǒng)的非DFX設(shè)計(jì)進(jìn)行調(diào)試呢?

評(píng)論