探討了RS485接口電路設計,包括其半雙工通信原理、關鍵要素、電路類型、自動收發功能及防雷保護等,強調了信號傳輸、電氣隔離、噪聲抑制和接地設計的重要性,以確保通信穩定和安全。突出特點包括支持多節點數據傳輸、長距離傳輸能力以及強大的抗干擾性。通過AB兩線間的電壓差異,RS485能夠判斷邏輯電平1或邏輯電平0,即當AB間電壓差超過200mV時,判定為高電平1,反之則為邏輯電平0。在電路的首尾兩端,通常會接入120Ω的電阻,以實現阻抗匹配并減少信號反射。

RS485硬件電路設計解析

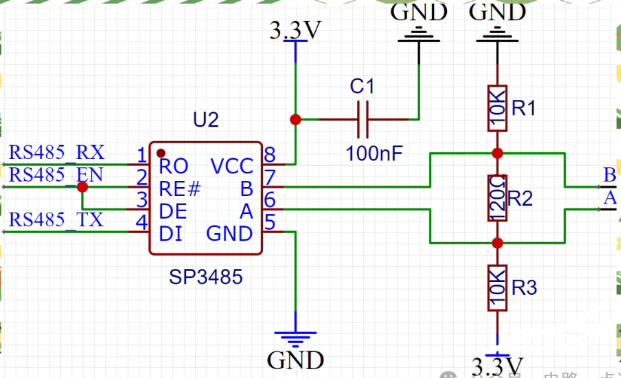

RS485電路設計主要分為隔離型和非隔離型兩種類型。以非隔離型電路為例,B端通過接地實現下拉,而A端則通過上拉電阻維持高電平,這樣確保了A和B之間的電壓差超過200mV,從而滿足RS485的邏輯判斷需求。此外,電路中的DE和RE引腳分別用于控制發送和接收功能。當RE引腳置為低電平時,芯片處于接收使能狀態;而DE引腳置為高電平時,芯片則進入發送狀態。在實際應用中,這兩個引腳通常通過一個IO口(如RS485_EN)進行統一控制。這樣,芯片在任意時刻都只能處于接收或發送的一種狀態。因此,在發送數據前,需要給RS485_EN信號置為高電平以啟動發送功能,而在接收數據時則置為低電平以切換到接收模式。

RS485自動收發電路硬件設計詳解

自動收發電路相較于普通的485電路,其關鍵差異在于增加了一個晶體管來控制485的使能引腳。設計中,R9限流電阻通常取值為4.7K,而R8上拉電阻也設定為4.7K,以確保在晶體管未導通時,使能引腳能夠被有效上拉。這樣的設計使得電路能夠根據需要自動切換收發模式,提高了數據的傳輸效率與靈活性。

接收數據時,RS485_RX引腳作為接收數據引腳,負責接收外界數據。在接收過程中,RS485_TX引腳保持高電平,同時VGS也處于高電平,這使得NPN三極管Q1得以導通。通過晶體管的導通,RE和DE相連的引腳被下拉至GND,從而啟動了接收使能,使電路進入接收狀態。

發送數據時,RS485_TX引腳作為發送數據引腳,負責向外界發送數據。當RS485_TX發送高電平(即1)時,晶體管導通,使得RE和DE的電平降低,從而關閉了RS485收發芯片。由于常態下485為高電平,因此此時發送的數據即為高電平。相反,當RS485_TX發送低電平(即0)時,晶體管不導通,這會使485收發芯片的發送使能變為高電平,同時DI引腳被持續下拉至GND,因此發送出去的數據為低電平。通過這種方式,電路實現了485的自動收發功能。

此外,為了進一步增強電路的穩定性和耐久性,我們還設計了RS485接口的防雷電路。這一設計能夠有效地保護電路免受雷電等外部干擾的影響,確保數據的傳輸安全與穩定。

接口防護電路

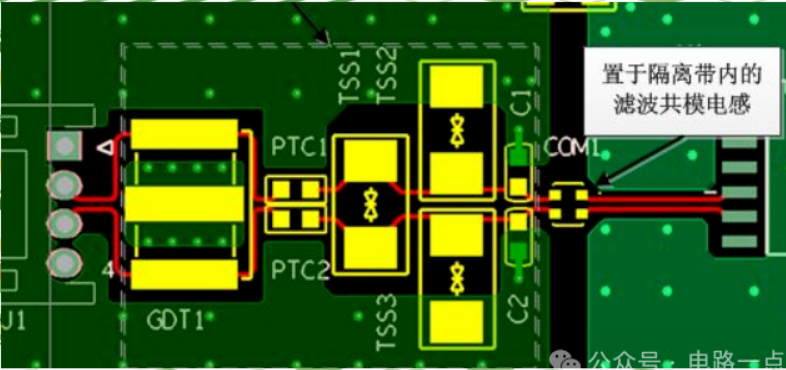

L1作為共模電感,其核心作用是衰減共模噪聲并增強電路的抗干擾能力。在選擇時,通常考慮120Ω/100MHz的規格。而C3電容則主要用于隔離接口地與數字地,以防止潛在的干擾,其值一般選為1000pF。為了確保電磁兼容性(EMC)達到高標準,即差模信號能夠承受2kV的沖擊,共模信號能抵御6kV的干擾,我們在接口處精心設計了由氣體放電管、熱敏電阻和TVS管共同組成的防護電路。

在布局RS485接口電路的PCB時,需注意GND的設計。為確保防護效果最佳,虛線所示的防護器件應盡可能地靠近接口位置,且擺放要緊湊有序。通常,我們首先放置這些防護器件,然后再進行濾波器件的布局。

RS485接口電路設計涵蓋了諸多關鍵要素,包括信號傳輸、電氣隔離、噪聲抑制、保護措施,以及電源和控制邏輯的設計等。在信號傳輸方面,通常選用一對雙絞線作為差分信號線(A和B),并優先考慮使用屏蔽雙絞線電纜,以最大程度地減少電磁干擾。同時,應確保A和B線的長度盡可能相等,從而減少信號延遲差異,進而保障信號的完整性。

為了抑制共模干擾,需要在信號線入口處加入共模電感L1。推薦選用阻抗范圍在120Ω/100MHz至2200Ω/100MHz之間的共模電感,以充分發揮其抑制作用。此外,還可能需要在電路中并聯去耦電容和TVS管等元件,以進一步提升電路的抗干擾能力。

在選擇收發器芯片時,常見的選項包括SP3485、MAX485等,它們能夠將TTL/CMOS邏輯電平有效地轉換為RS485差分信號。同時,需要仔細關注RE、DE以及RO等控制引腳的連接邏輯,通常RE和DE可以通過單個控制信號進行連接,從而實現對發送/接收模式的統一控制。

在偏置和終端電阻方面,A信號線可能需要上拉電阻(如10kΩ至4.7kΩ),以確保在空閑時的電壓狀態;而B信號線則可能需要下拉到GND。此外,在總線的兩端或適當位置應放置120Ω終端電阻,以減少信號反射并改善信號質量。

為了增強電路的魯棒性,可以在信號線上添加TVS管和/或自恢復保險絲,以實現過壓和浪涌保護。在高風險環境中,甚至需要加入6kV以上的防雷擊保護電路設計。

此外,良好的接地設計對于RS485接口電路的性能至關重要。特別是接口地的處理,有時可能涉及單板地與外殼的直接連接,并通過1000pF電容進行耦合。在電路板布局時,應確保電源和信號線的分離,以減少交叉干擾,并增加濾波和退耦電容的使用。

最后,根據應用需求,可能需要設計相應的控制邏輯電路或使用MCU來控制發送使能信號,從而實現自動或手動的發送/接收切換。對于需要自動收發管理的電路設計,可能需要更復雜的邏輯來自動調節發送和接收狀態,以適應不同的通信場景。

RS485接口電路設計并不僅僅是技術層面的考量,它還需要綜合考慮電磁兼容性(EMC)、系統的可靠性以及安全性等多個方面,以確保在復雜的工業應用環境中能夠保持穩定的通信性能。

-

收發器

+關注

關注

10文章

3834瀏覽量

111376 -

電路設計

+關注

關注

6745文章

2731瀏覽量

219967 -

引腳

+關注

關注

16文章

2115瀏覽量

55947 -

RS485接口

+關注

關注

2文章

64瀏覽量

14927

原文標題:全面解析RS485接口電路設計要點

文章出處:【微信號:zfdzszy,微信公眾號:張飛電子實戰營】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

rs485接口EMC電路設計方案(防雷/濾波及防護電路原理圖)

RS485接口電路設計要點

RS485接口電路設計要點

評論