寄生電容有一個(gè)通用的定義:寄生電容是存在于由絕緣體隔開的兩個(gè)導(dǎo)電結(jié)構(gòu)之間的虛擬電容(通常不需要的),是PCB 布局中的一種效應(yīng),其中傳播的信號表現(xiàn)得好像就是電容,但其實(shí)并不是真正的電容。

寄生電容通常出現(xiàn)在被電介質(zhì)隔開的任何一對導(dǎo)體之間。

PCB寄生電容

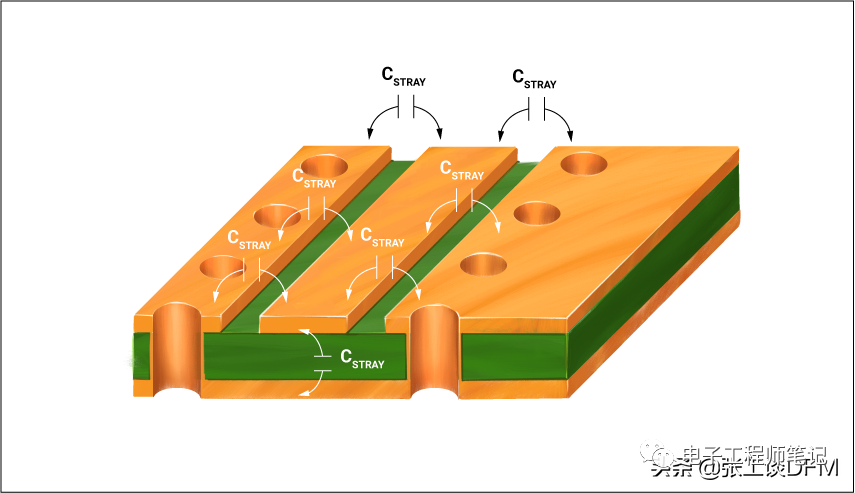

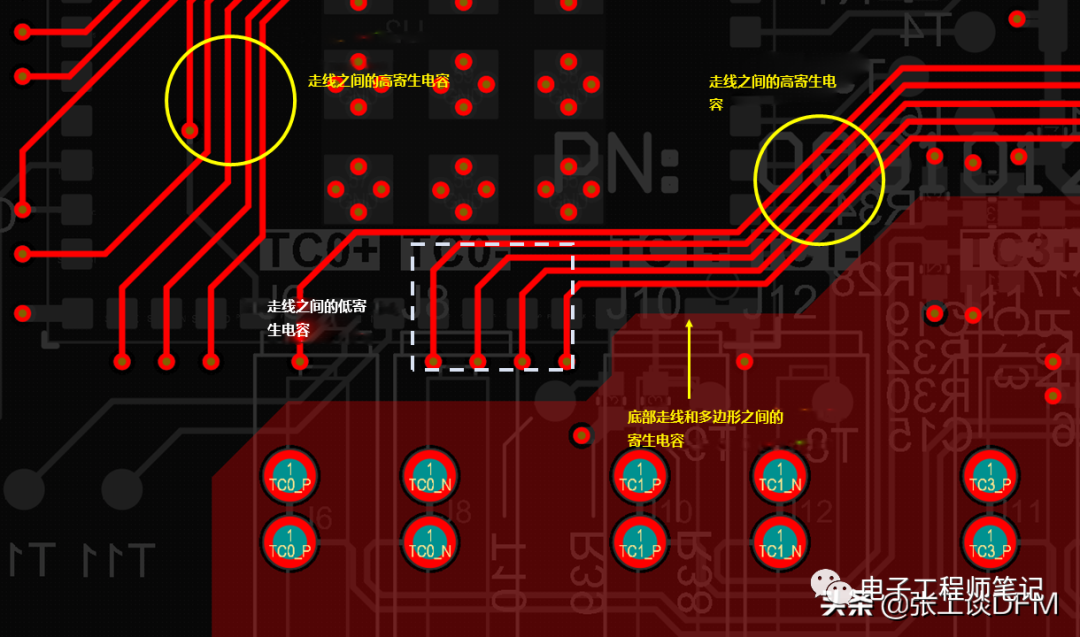

在 PCB 中,寄生電容基本上可以出現(xiàn)在任何地方,可以參考下方的布局,有標(biāo)記出電容突出的區(qū)域,這里只是頂層產(chǎn)生的電容,但其他層都有可能存在電容。

PCB 寄生電容

二、 PCB 寄生電容的影響

傳輸線中的頻帶限制行為,在非常高的頻率下產(chǎn)生低通濾波器行為

不同電位地之間的噪聲耦合,導(dǎo)致共模噪聲

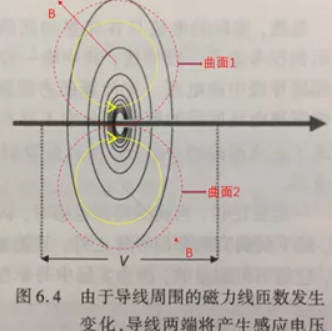

噪聲或信號耦合到組件中,尤其是繞線電感

高頻電容串?dāng)_(表現(xiàn)為 FEXT 和 NEXT)

由于電源層和接地層之間的間距而導(dǎo)致的PDN 阻抗修改

EMI 耦合到散熱器中,產(chǎn)生共模電流

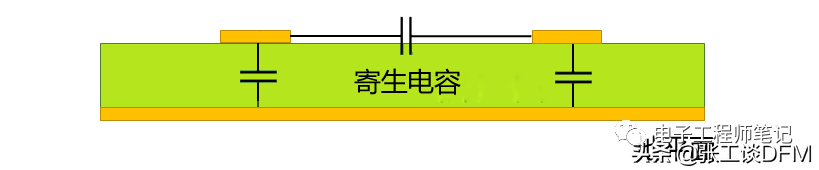

下圖顯示了 PCB 布局中寄生電容如何產(chǎn)生的簡單示例。在 PCB 布局中,我們有一個(gè)由絕緣體隔開的導(dǎo)體排列,形成一個(gè)具有等效電容的復(fù)雜結(jié)構(gòu)。

下圖結(jié)構(gòu)可以建模為電容器的排列,但請注意該結(jié)構(gòu)中的一些寄生電感和電阻。正是這種等效電容和電感決定了 PCB 布局中的阻抗。

兩條微帶走線之間以及兩條走線與附近接地層之間的寄生電容示例

三、 PCB 寄生電容怎么計(jì)算?

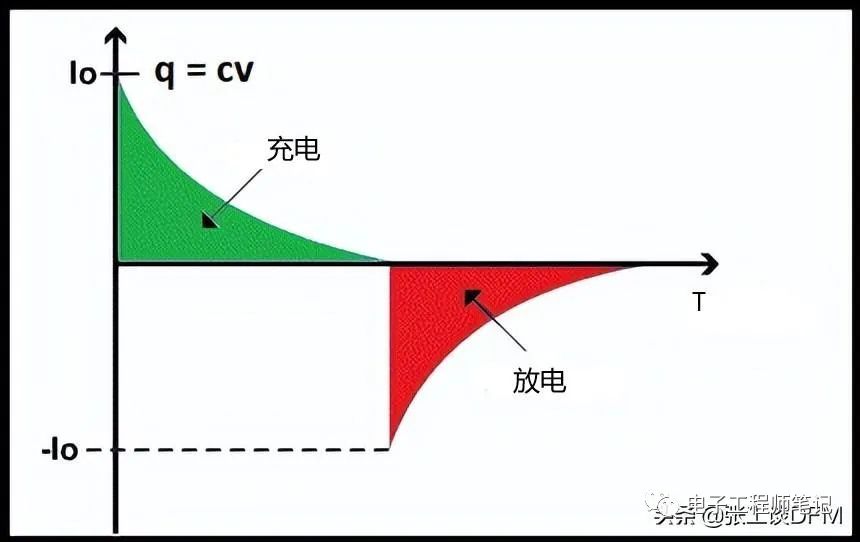

下圖為電容的充電放電循壞圖。

電容的充電放電循壞

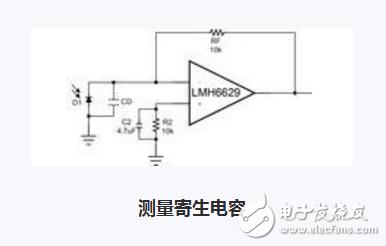

寄生電容是導(dǎo)體的固有特性,是每單位電勢變化的存儲量,寄生電容計(jì)算公式為:

C=q/v

C:電容,單位:法拉(F)

V:電壓,單位:伏特 (V)

Q:電荷,單位:庫倫(C)

1)對于不隨時(shí)間變化的恒定電信號,dv/dt = 0,也就是電位沒有變化:

i = 0

2)如果電路回路中有電容,dv/dt會收斂到一個(gè)固定值,電位會發(fā)生變化,產(chǎn)生電流:

i ≠ 0

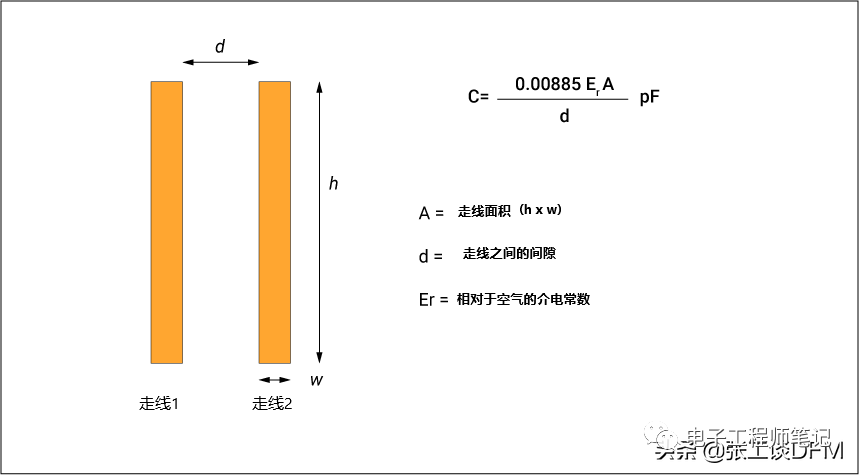

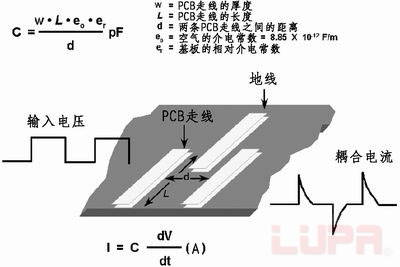

四、走線電容的計(jì)算

平行板電容的電容為:C= (kA/11.3d)pF

C:電容

A:極板面積

k:板材料的相對介電常數(shù)

d:極板之間的距離

走線電容的計(jì)算圖如下所示:

走線電容的計(jì)算圖

五、PCB 寄生電容怎么消除?

PCB 布局永遠(yuǎn)不會完全消除寄生電容,但你可以減少PCB 布局中的寄生電容或者采取一些措施來限制寄生電容對信號和電源完整性的影響。

這里列舉10 條可以減少 PCB 布局中的寄生電容的措施:

1、避免平行布線

采用平行布線時(shí),金屬之間的面積最大,寄生電容也會最大。

2、移除電源層

電源層通常被認(rèn)為是交流接地,與接地層完全相同,所以移除電源層與移除導(dǎo)體附近的接地層一樣重要。

3、使用法拉第屏蔽或保護(hù)環(huán)

將法拉第屏蔽放置在兩條跡線之間以最大程度地減少寄生電容效應(yīng)。

4、關(guān)鍵走線盡可能窄和短

為了最大限度地減少寄生電容,使關(guān)鍵走線盡可能窄,以使 PCB 工藝可以處理,與附近的走線保持良好的距離。

5、避免過度使用過孔

過孔的過度使用會增加寄生電容,最好盡可能用貼片來代替過孔。

6、避免元件分離

元件之間、電源層和接地層,輸出和輸入等的正確接線,對減少不需要的寄生電容非常重要。

7、信號層應(yīng)夾在兩個(gè)接地層之間或一個(gè)接地層或電源層之間

例如:在4層板中,可以將電源層放在底層,并在電源層和接地層之間布線一些敏感走線,這可以防止來自一層中的信號的 EMI 在另一層中的信號中引起噪聲。

8、確定合適的層厚

較薄的層會減小環(huán)路面積和寄生電感,但會增加寄生電容。

9、信號完整性

阻抗降低,通常是由于布局中靠近接地銅線

由于互連和驅(qū)動器/接收器組件之間的阻抗不匹配導(dǎo)致更高的回波損耗

高通濾波行為導(dǎo)致更高的插入損耗

簡單的解決方案是增加互連與不是所需參考平面的任何導(dǎo)體之間的距離。

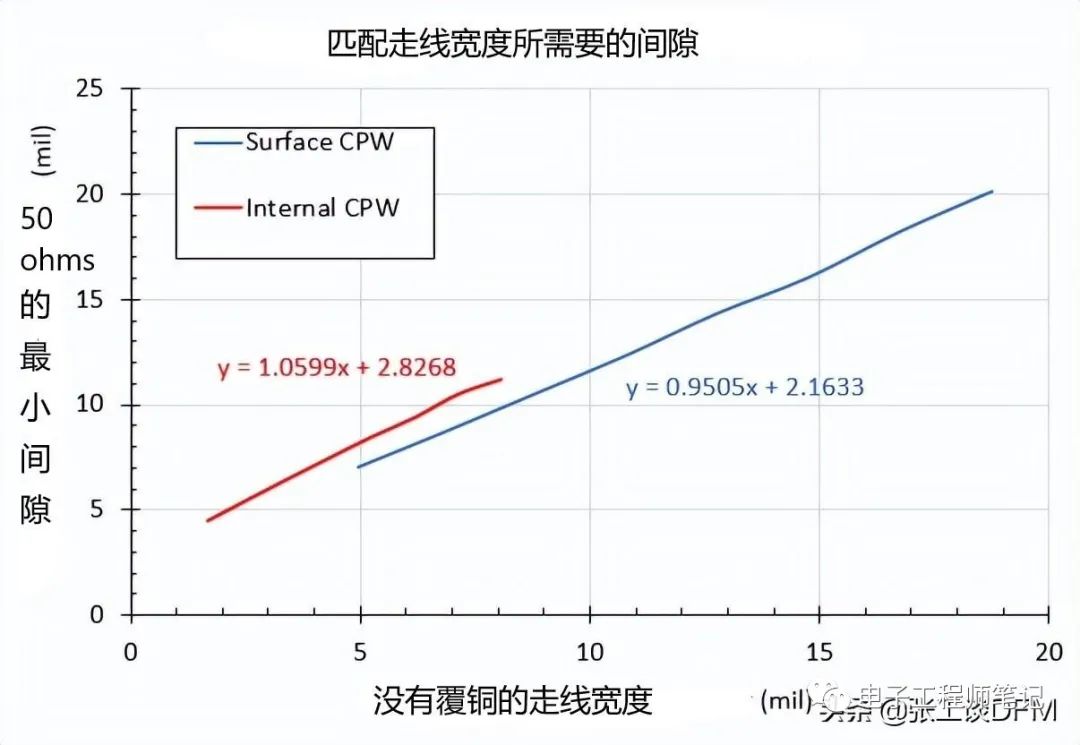

在設(shè)計(jì)期間,應(yīng)仔細(xì)設(shè)計(jì)PCB 上的走線寬度,考慮附近的導(dǎo)體,尤其是附近的覆銅,創(chuàng)建共面走線布置。

覆銅問題是上述信號完整性問題的常見問題。

PCB Layout 應(yīng)該花時(shí)間計(jì)算覆銅與其走線之間的所需的最小間隙,以確保阻抗控制。

下圖顯示了具有 50 歐姆 CPW 微帶線和帶狀線的 Isola 370HR 層壓板的示例計(jì)算。

兩條微帶走線之間以及兩條走線與附近接地層之間的寄生電容

10、電源完整性

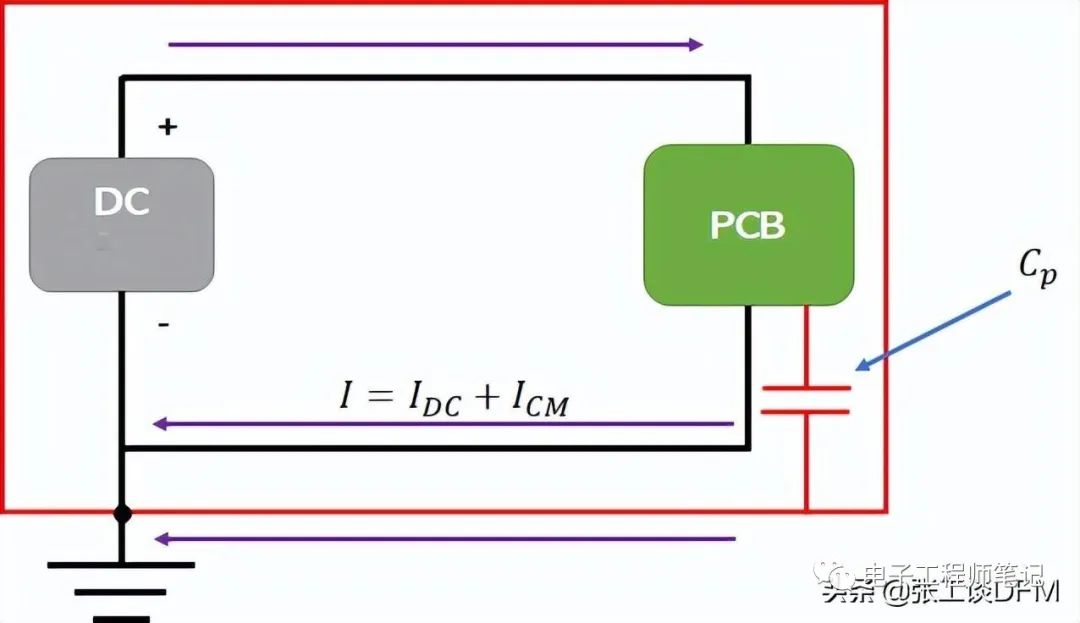

寄生電容在電源完整性方面既可取又不可取,可以通過將電路板中的 PDN 結(jié)構(gòu)與涉及多個(gè)接地系統(tǒng)進(jìn)行比較。

在具有多個(gè)接地點(diǎn)(例如 PCB 電源接地層、系統(tǒng)接地區(qū)域和機(jī)箱接地)的系統(tǒng)中,寄生電容不受歡迎的一種常見情況。

在這些系統(tǒng)中,尤其是在大電流電源中,寄生電容可能存在于 PCB 接地層和機(jī)箱接地之間,從而允許共模電流通過系統(tǒng)并產(chǎn)生強(qiáng)烈輻射。

當(dāng) PCB 接地層和機(jī)箱接地的電位略有不同時(shí),設(shè)備機(jī)箱的寄生電容如何為共模電流創(chuàng)建路徑。

六、減少PCB 寄生電容的示例

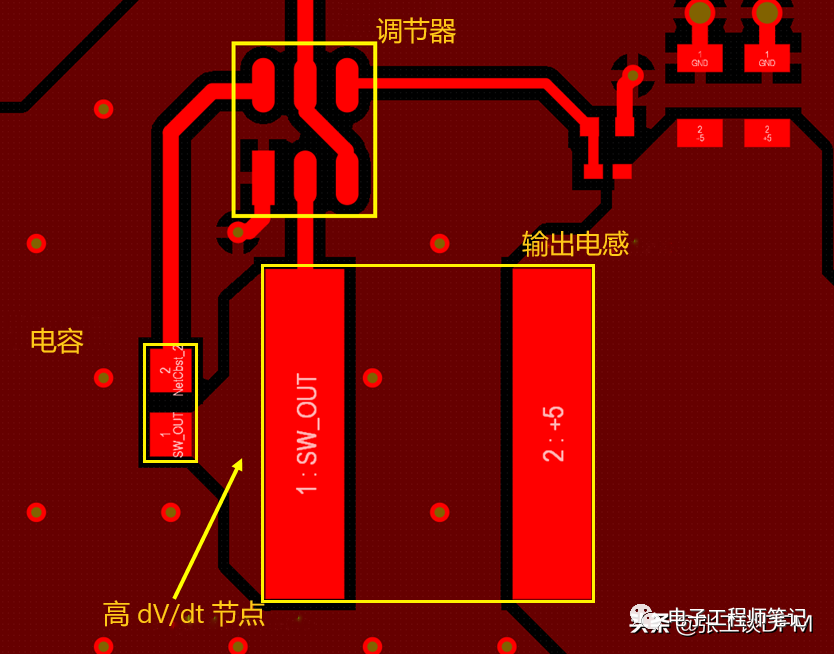

1、開關(guān)穩(wěn)壓器中的高 dV/dt 節(jié)點(diǎn)

下面的穩(wěn)壓器示例部分說明了強(qiáng) dV/dt 節(jié)點(diǎn)的位置,以及為什么這種布局將有更大的耦合到其反饋回路而不是系統(tǒng)的任何附近部分。

這個(gè)節(jié)點(diǎn)對附近的接地區(qū)域有一些寄生電容,如果附近還有其他一些元件或電路,這些電路的寄生電容會導(dǎo)致這些電路中出現(xiàn)開關(guān)噪聲。附近的接地有一些幫助,

但真正防止噪聲耦合的是從 SW_OUT 連接回穩(wěn)壓器芯片的電容,這個(gè)大電容為高 dV/dt 開關(guān)噪聲返回開關(guān)級高端提供了一條低阻抗路徑,從而有效地將開關(guān)級輸出與 GND 去耦。

dV/dt 節(jié)點(diǎn)可能負(fù)責(zé) PCB 布局周圍的噪聲耦合

dV/dt 節(jié)點(diǎn)可能負(fù)責(zé) PCB 布局周圍的噪聲耦合,有意放置的電容器可以防止這種情況發(fā)生。

另一個(gè)有助于減少 SW_OUT 和附近走線或電路之間寄生電容的策略是利用下一層的 GND 平面。

與 PCB 布局中與其他節(jié)點(diǎn)的耦合相比,使 GND 平面更靠近高 dV/dt 節(jié)點(diǎn)將通過創(chuàng)建更強(qiáng)的電場與 GND 耦合來降低互電容。

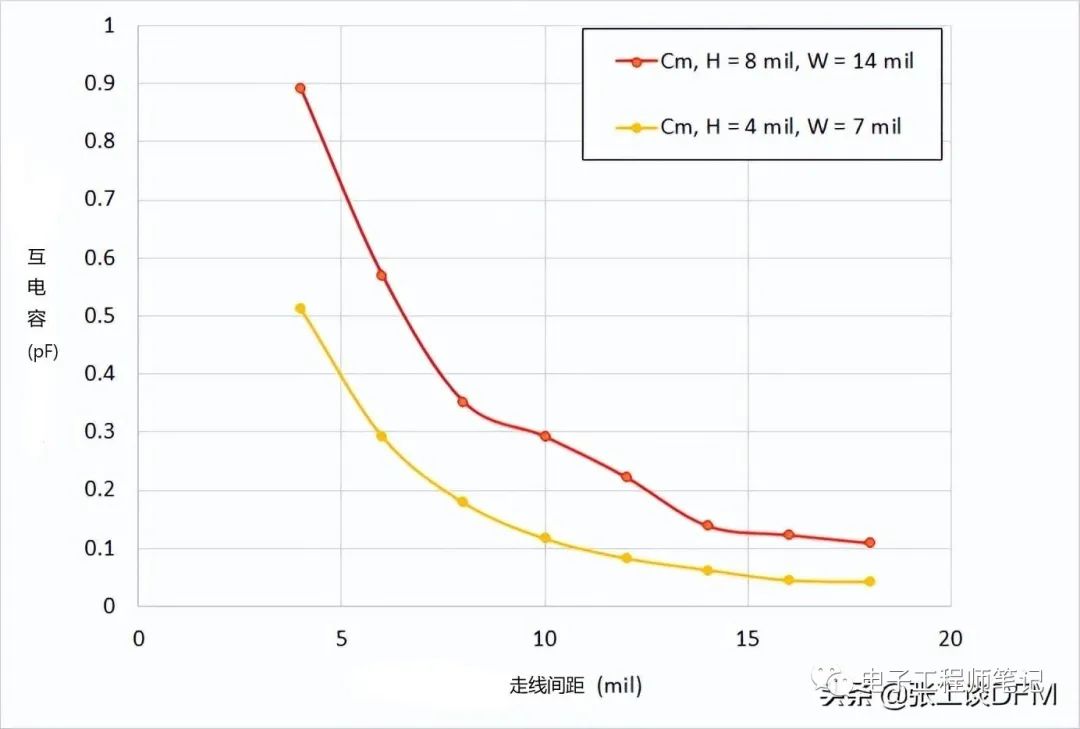

2、兩條走線之間的互電容

電容串?dāng)_是走線之間的兩種耦合(另一種是電感)之一,其中一條走線上的信號會在另一條走線上產(chǎn)生噪聲。在逐漸更高的頻率下,這主要由互電容決定,這里提供兩種選擇來減少寄生電容:

使地線更靠近走線,同時(shí)使走線更窄(固定阻抗目標(biāo))

增加走線之間的間距

仿真結(jié)果顯示了兩條 50 歐姆走線之間的寄生電容如何受與 GND 平面的距離(表示為 H)的影響

-

pcb

+關(guān)注

關(guān)注

4404文章

23877瀏覽量

424231 -

濾波器

+關(guān)注

關(guān)注

162文章

8411瀏覽量

185690 -

噪聲

+關(guān)注

關(guān)注

13文章

1156瀏覽量

49227 -

寄生電容

+關(guān)注

關(guān)注

1文章

302瀏覽量

20299

原文標(biāo)題:總結(jié)10 種方法幫搞定 PCB的寄生電容

文章出處:【微信號:電子工程師筆記,微信公眾號:電子工程師筆記】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

PCB布線設(shè)計(jì)時(shí)寄生電容的計(jì)算方法

PCB寄生電容的影響 PCB寄生電容計(jì)算 PCB寄生電容怎么消除

寄生電容,寄生電容是什么意思

如何消除寄生電容的影響

寄生電容產(chǎn)生的原因_寄生電容產(chǎn)生的危害

什么是寄生電感_PCB寄生電容和電感計(jì)算

什么是寄生電容_寄生電容的危害

電容器基本計(jì)算公式的詳細(xì)說明(二)

什么是寄生電容,什么是寄生電感

技術(shù)資訊 | 在高速設(shè)計(jì)中如何消除寄生電容?

PCB寄生電容的影響、計(jì)算公式和消除措施

PCB寄生電容的影響、計(jì)算公式和消除措施

評論