點擊上方藍字關注我們

FPGA 器件自問世以來,已經經過了幾個不同的發展階段。驅動每個階段發展的因素都是工藝技術和應用需求。正是這些驅動因素,導致器件的特性和工具發生了明顯的變化。FPGA 經歷了如下幾個時代:

● 發明時代;

● 擴展時代;

● 積累時代;

● 系統時代。

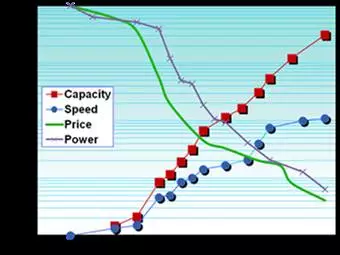

賽靈思于 1984 年發明了世界首款 FPGA,那個時候還不叫 FPGA,直到 1988 年 Actel 才讓這個詞流行起來。接下來的 30 年里,這種名為 FPGA 的器件,在容量上提升了一萬多倍,速度提升了 一百倍,每單位功能的成本和能耗降低了一萬多倍 (見圖 1)。

圖 1:與 1988 年的賽靈思 FPGA 特征對比。價格和功耗降低一萬倍。

這些進步主要由工藝技術所驅動, 而且人們很容易認為 FPGA 的發展只是隨著工藝的發展簡單地增大了容量。其實并沒有這么簡單。真正的故事要精彩得多。

1、發明時代(1984 年 - 1992 年)

首款 FPGA,即賽靈思 XC2064,只包含 64 個邏輯模塊,每個模塊含有兩個 3 輸入查找表 (LUT) 和一個寄存器。按照現在的計算,該器件有 64 個邏輯單元——不足 1000 個邏輯門。盡管容量很小,XC2064 晶片的尺寸卻非常大,比當時的微處理器還要大;而且采用 2.5 微米工藝技術勉強能制造出這種器件。

每功能的晶片尺寸和成本至關重要。XC2064 只有 64 個觸發器,但由于晶片太大,成本高達數百美元。產量對大晶片來說是超線性的,因此晶片尺寸增加 5% 就會讓成本翻一倍,讓良率降至零,同時也導致初期的賽靈思無產品可賣。成本控制不僅僅是成本優化的問題;更是牽扯到公司生存問題。

在成本壓力下,FPGA 架構師尋求通過架構和工藝創新來盡可能提高 FPGA 設計效率。盡管基于 SRAM 的 FPGA 是可重編程的,但是片上 SRAM 占據了 FPGA 大部分的晶片面積。基于反熔絲的 FPGA 以犧牲可重編程能力為代價,避免了 SRAM 存儲系統片上占位面積過大問題。1990 年,最大容量的 FPGA 是基于反熔絲的 Actel 1280。Quicklogic 和 Crosspoint 也跟隨 Actel 的腳步開發出基于反熔絲的 FPGA。為提高效率,架構經歷了從復雜的 LUT 結構到 NAND 門再到單個晶體管的演變。

在發明時代,FPGA 是數量遠遠比用戶的應用產品小得多。因此,多 FPGA 系統變得流行,自動化多芯片分區軟件成為 FPGA 設計套件的重要組成部分。自動布局布線尚未有。完全不同的 FPGA 架構排除了通用設計工具的可能,因此 FPGA 廠商就擔負起了為各自器件開發電子設計自動化 (EDA) 的任務。由于問題比較小,FPGA(邏輯和物理)手動設計是可以接受的。手動設計與優化通常很有必要,因為芯片上布線資源有限會帶來很大設計挑戰。

2、擴展時代(1992 年 - 1999 年)

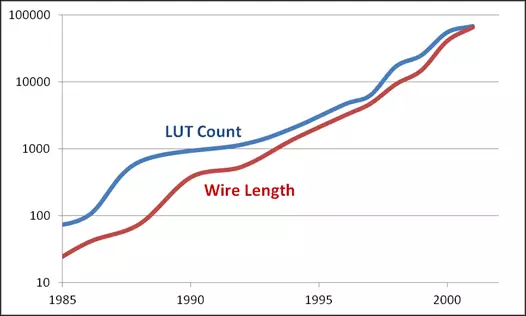

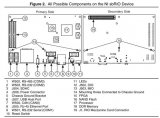

FPGA 初創公司都是無晶圓廠的公司,在當時屬于新鮮事物。由于沒有晶圓廠,他們在上世紀 90 年代初期通常無法獲得領先的芯片技術。因此 FPGA 開啟了擴展時代,此時落后于 IC 工藝的發展。到上世紀 90 年代后期,IC 代工廠意識到 FPGA 是理想的工藝發展推動因素,由此 FPGA 成為掃除工藝發展障礙的利器。代工廠只要能用新工藝產出晶體管和電線,就能制造基于 SRAM 的 FPGA。每一代新工藝的出現都會將晶體管數量增加一倍,使每功能成本減半,并將最大 FPGA 的尺寸增大一倍。化學-機械拋光(CMP)技術允許代工廠在 IC 上堆疊更多金屬層,使 FPGA 廠商能夠大幅增加片上互聯,以適應更大的 LUT 容量 (見圖 2)。

圖 2:FPGA LUT 和互連線路的增加。線路長度以數百萬晶體管間距來測量。

占位面積變得不再像發明時代時那么寶貴。現在,占位面積可讓位于性能、特性和易用性。更大的 FPGA 設計需要具有自動布局布線功能的綜合工具。到上世紀 90 年代末,自動綜合、布局和布線已經成為設計流程的必要步驟。FPGA 公司的命運對 EDA 工具的依賴程度不亞于對 FPGA 功能的依賴程度。

最重要的是,實現容量翻番和片上 FPGA 邏輯成本減半的最簡單方法是采用新一代工藝技術節點,因此,盡早采用新的工藝節點意義非凡。基于 SRAM 的 FPGA 在這個時期實現了明顯的產品優勢,因為它們率先采用了每種新工藝節點:基于 SRAM 的器件可立即使用密度更高的新工藝,而反熔絲在新節點上的驗證工作則額外需要數月甚至數年時間。基于反熔絲的 FPGA 喪失了競爭優勢。為獲得上市速度和成本優勢,架構創新與工藝改進相比就要退居其次。

3、積累時代(2000 年 - 2007 年)

新千年伊始,FPGA 已成為數字系統中的通用組件。容量和設計尺寸快速增加,FPGA 在數據通信領域開辟了巨大市場。2000年代初期互聯網泡沫破滅之后,迫切需要降低成本,這也減少了很多“臨時”ASIC 用戶。定制芯片對小的研發團隊來說風險太大。當他們發現FPGA可以解決他們的問題,自然他們就變成了 FPGA 用戶。

FPGA 問題不局限于典型問題,單純提高容量不足以保證市場增長。FPGA 廠商通過如下兩種方式解決了這一挑戰。針對低端市場,廠商再度關注效率問題,并生產低容量、低性能、“低成本”的 FPGA 系列,例如賽靈思 Spartan FPGA 系列。針對高端市場,FPGA 廠商通過開發針對重要功能的軟邏輯 (IP) 庫,努力讓客戶更方便地填充最大的 FPGA。這些軟邏輯功能中最值得注意的是存儲器控制器、各種通信協議模塊(包括以太網 MAC),甚至軟微處理器(如賽靈思 MicroBlaze 處理器)。

設計特點在 2000 年代發生了改變。大型 FPGA 容納超大型設計(完整子系統)。FPGA 用戶不再只是實現邏輯;他們需要使 FPGA 設計符合系統標準要求。這些標準主要是指信號和協議方面的通信標準,可用來連接外部組件或者實現內部模塊通信。處理標準讓 FPGA 在計算密集型應用中發揮越來越重要的作用。積累時代末期,FPGA 已不僅是門陣列,而且還是集成有可編程邏輯的復雜功能集。FPGA 儼然變成了一個系統。

4、系統時代(2008 年以后)

為解決系統設計問題,FPGA 越來越多地整合系統模塊:高速收發器、存儲器、DSP 處理單元和完整處理器。同時還進一步集成了重要控制功能:比特流加密與驗證、混合信號處理、電源與溫度監控以及電源管理等。這些特性在 Zynq All Programmable 器件中得到了充分體現。同時,器件也推動了工具的發展。系統 FPGA 需要高效的系統編程語言,現可利用 OpenCL 和 C 語言以類似軟件的流程來編程。

FPGA 發展何時才能到頭?可編程性的基本價值已經為業界所共識,小型、高效的邏輯操作可加速很多重要算法并降低功耗,FPGA 技術會持續存在, 并不斷發展演進。

有你想看的精彩 至芯科技-FPGA就業培訓來襲!你的選擇開啟你的高薪之路!7月12號北京中心開課、歡迎咨詢! 基于FPGA的CAN總線通信節點設計 基于FPGA的DVI/HDMI接口實現方案

掃碼加微信邀請您加入FPGA學習交流群

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優秀的FPGA工程師、學生、老師、這里FPGA技術交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點個在看你最好看

原文標題:一文了解FPGA發展之路 —— 將功耗和價格降低一萬倍

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636330

原文標題:一文了解FPGA發展之路 —— 將功耗和價格降低一萬倍

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

一文了解數據存儲演變之路

Altera Agilex 5 D系列FPGA和SoC家族全面升級

利用DMA如何降低MCU功耗?

一文了解Mojo編程語言

如何通過優化電能質量在線監測裝置的散熱系統來降低功耗?

ALM(應用生命周期管理)解析:一文了解其概念、關鍵階段及Perforce ALM工具推薦

AI 芯片浪潮下,職場晉升新契機?

CYBT-213043-MESH如何降低低功耗節點的電流消耗?

一文了解電壓諧波

新一代nRF54L系列:進一步降低功耗

不同于HBM,這種創新的堆疊式DRAM,功耗有望降低50%

功耗對IGBT性能的影響,如何降低IGBT功耗

一文了解FPGA發展之路 —— 將功耗和價格降低一萬倍

一文了解FPGA發展之路 —— 將功耗和價格降低一萬倍

評論