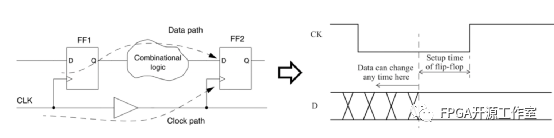

1 setup time

Setup time (建立時間)是數據信號(D)在時鐘事件(這里以時鐘上升沿為例)發生之前保持穩定的最小時間。以便時鐘可靠地對數據進行采樣。適用于同步電路,如觸發器(flip-flop)。

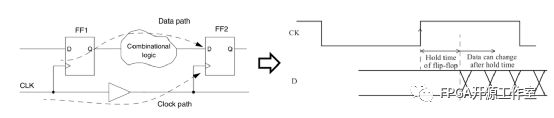

2 hold time

Hold time (保持時間) 是數據信號(D) 在時鐘事件(這里以時鐘上升沿為例)發生之后保持穩定的最小時間。

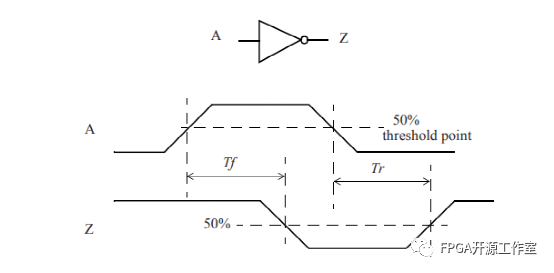

3 Propagation Delay

信號傳播延時(Propagation Delay),以反相器(Inverter)為例,A輸入信號變化(0-1的50%)為開始,到Z輸出信號變化(1-0的50%)所需的時間稱為Tf, A輸入信號變化(1-0的50%)為開始,到Z輸出信號變化(0-1的50%)所需的時間稱為Tr。

Output fall delay (Tf)

Output rise delay (Tr)

# Threshold point of an input falling edge: input_threshold_pct_fall : 50.0; # Threshold point of an input rising edge: input_threshold_pct_rise : 50.0; # Threshold point of an output falling edge: output_threshold_pct_fall : 50.0; # Threshold point of an output rising edge: output_threshold_pct_rise : 50.0;

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

觸發器

+關注

關注

14文章

2056瀏覽量

63406 -

時序分析

+關注

關注

2文章

130瀏覽量

24227 -

同步電路

+關注

關注

1文章

61瀏覽量

13759

原文標題:時序分析的基本概念(1)

文章出處:【微信號:leezym0317,微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

時序分析基本概念

發表于 05-06 14:35

時序分析基本概念介紹

今天我們要介紹的時序分析概念是Combinational logic. 中文名組合邏輯單元。這是邏輯單元的基本組成器件。比如我們常見的and, or, not, nand,nor等門電路。

FPGA設計中時序分析的基本概念

時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

時序分析基本概念介紹—Timing Arc

今天我們要介紹的時序基本概念是Timing arc,中文名時序弧。這是timing計算最基本的組成元素,在昨天的lib庫介紹中,大部分時序信息都以Timing arc呈現。

時序分析基本概念解析

正如“聚合”的意思(字典)“兩個或多個事物聚集在一起的發生”。所以我們可以假設它也與 2 個時鐘路徑聚集在一起有關。 (了解時鐘路徑請參考另一篇博客-靜態時序分析基礎:第1部分“時序路徑”)

時序分析的基本概念

時序分析的基本概念

評論