Cadence Spectre 技術助力 DB GlobalChip 加速模擬和混合信號 IP 開發

中國上海,2023 年 6 月 25 日 —— 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,DB GlobalChip 部署了 Cadence Spectre FX Simulator,該工具與 Spectre AMS Designer 集成,用于驗證其關鍵的模擬和混合信號 IP,與現有流程相比,在達到所需精度的同時,可幫助提升 2 倍性能。Cadence 的這款解決方案助力 DB GlobalChip 加速了 IP 開發和驗證周期,可以更快將產品推向市場。

在客戶規定的時間內滿足模擬和混合信號 IP 的嚴苛設計要求,這是一項日益突出的挑戰。DB GlobalChip 不斷創新自己的設計方法學,力求在保證精度的同時縮短設計和驗證周期。其成功將 Spectre FX Simulator 用于模擬晶體管級設計,同時還運用了全面的混合信號仿真解決方案——Spectre AMS Designer,該工具與 Spectre FX Simulator 集成,用于涵蓋數字控制邏輯,以更快的速度轉換模擬 / 數字交互影響。

Cadence Spectre 為 DB GlobalChip 設計團隊提供了開箱即用的直觀使用模式和全方位的方法學支持,其中包括 Cadence Virtuoso ADE Suite,幫助他們獲得全面的驗證品質和覆蓋率,同時大大加快了向客戶交付 IP 的速度。

DB GlobalChip 利用了 Spectre FX Simulator 的多核心架構來并行運行仿真,并利用易于使用的預設選項,優化混合信號和晶體管級仿真的精度。這就使得設計和驗證團隊能夠在不犧牲精度的前提下,利用現有的硬件資源來加快仿真周轉速度。

“要開發復雜的模擬和混和信號 IP,需要借助高度準確的 FastSPICE 仿真,并與混合信號驗證環境緊密集成,”DB GlobalChip 副總裁 Jeongtae Park 說道,“我們的 IP 設計人員利用 Cadence 全面混合信號仿真解決方案提供的使用模式和超高性能,縮短了運行周期,將生產力提升了 2 倍,同時能滿足嚴苛的精度要求。”

Spectre FX Simulator 和 Spectre AMS Designer 是業界領先的 Spectre Simulation Platform 的一部分,該平臺提供唯一包含多個求解器的完整仿真解決方案,使設計人員可以在電路級、模塊級和系統級仿真和驗證任務之間輕松無縫切換。Spectre Simulation Platform 支持 Cadence 的智能系統設計(Intelligent System Design)戰略,助力客戶實現 SoC 卓越設計。

要獲取更多信息,請訪問:

www.cadence.com/go/SpectreSimulationPlatform

(您可復制至瀏覽器或點擊閱讀原文打開)

關于 Cadence

Cadence 是電子系統設計領域的關鍵領導者,擁有超過 30 年的計算軟件專業積累。基于公司的智能系統設計戰略,Cadence 致力于提供軟件、硬件和 IP 產品,助力電子設計概念成為現實。Cadence 的客戶遍布全球,皆為最具創新能力的企業,他們向超大規模計算、5G 通訊、汽車、移動設備、航空、消費電子、工業和醫療等最具活力的應用市場交付從芯片、電路板到完整系統的卓越電子產品。Cadence 已連續九年名列美國財富雜志評選的 100 家最適合工作的公司。如需了解更多信息,請訪問公司網站www.cadence.com。

2023 Cadence Design Systems, Inc. 版權所有。在全球范圍保留所有權利。Cadence、Cadence 徽標和 www.cadence.com/go/trademarks 中列出的其他 Cadence 標志均為 Cadence Design Systems, Inc. 的商標或注冊商標。所有其他標識均為其各自所有者的資產。

-

Cadence

+關注

關注

68文章

1011瀏覽量

146905

原文標題:DB GlobalChip有效運用Cadence的Spectre FX和AMS Designer,將IP驗證速度加快2倍

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Cadence收購Arm基礎IP業務,誰是贏家?

Cadence 推出 ChipStack? AI Super Agent,開辟芯片設計與驗證新紀元

Cadence推出高可靠性LPDDR5X 9600Mbps內存IP系統解決方案

Cadence Conformal AI Studio三大核心引擎重塑IC驗證

今日看點:Cadence宣布收購ChipStack;德州儀器啟用馬六甲第二組裝測試工廠

如何驗證硬件冗余設計的有效性?

1218 MHz、25 dB 增益 CATV 倍功率放大器 skyworksinc

Cadence推出Cerebrus AI Studio

Cadence Conformal AI Studio助力前端驗證設計

Cadence推出HBM4 12.8Gbps IP內存系統解決方案

Cadence推出DDR5 12.8Gbps MRDIMM Gen2內存IP系統解決方案

使用gpif designer fx2lp在CTL0中生成波形來連接FPGA 以便從FPGA獲取數據,為什么不能正常工作?

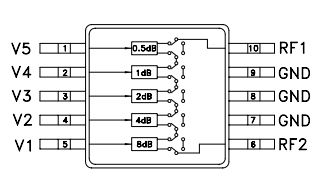

HMC306AMS10/306AMS10E 0.5 dB LSB GaAs MMIC 5位數字衰減器技術手冊

一文讀懂分貝(dB)【強烈建議收藏】

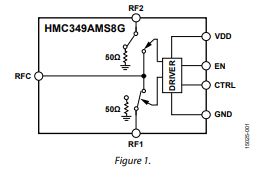

HMC349AMS8G高隔離度、非反射、GaAs、SPDT開關,100MHz至4GHz技術手冊

DB GlobalChip有效運用Cadence的Spectre FX和AMS Designer,將IP驗證速度加快2倍

DB GlobalChip有效運用Cadence的Spectre FX和AMS Designer,將IP驗證速度加快2倍

評論