沉積晶圓通量是晶圓廠 FAB 效率的關鍵指標之一, 也是晶圓廠 FAB 不斷改進以降低每次移動成本和減少資本支出的關鍵指標. 上海伯東日本 Atonarp Aston? 質譜儀提供腔室清潔終點檢測方案已成功應用于 low-k 電介質沉積應用 ( 特別是氮化硅 Si3N4 ), 在減少顆粒污染的同時, 縮短了生產時間.

low-k 電介質沉積需要經常清潔工藝室以除去沉積冷凝物的堆積. 如果不除去冷凝物可能會導致顆粒薄片從腔室壁上分層, 從而導致產量損失.通常每 5 片晶圓進行一次清潔(在 25 片晶圓批次中進行 5 次).

上海伯東日本 AtonarpAston? 質譜儀提供腔室清潔終點檢測解決方案

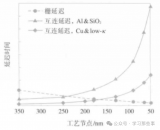

為了提高整個工藝吞吐量, 需要使用端點檢測來縮短腔室清潔周期時間. 使用殘余氣體分析儀 RGA 或光學發射光譜 OES 的傳統計量解決方案是無效的. 用于腔室清潔的三氟化氮 NF3 氣體對 RGA 電子碰撞電離源具有高度腐蝕性(使其無法用于生產), 并且 OES 需要在清潔周期中不存在等離子體. 從歷史上看, 腔室清潔周期是一個固定時間的工藝步驟, 有足夠的余量, 以確保考慮到腔室之間的統計變化. 借助上海伯東日本 Atonarp Aston? 質譜儀基于終點檢測的腔室清潔既可以縮短處理時間, 又不會影響工藝裕度, 還可以避免過度清潔, 因為過度清潔會造成氟化鋁污染, 造成大量腔室的陳化處理.

使用Aston? 質譜儀檢測結果

讓處理時間減少 >40%:在一次晶圓廠 FAB 連續生產研究中, Aston 質譜儀將整個腔室清潔周期縮短了高達 80%. 在總共5片晶圓加工周期內, 晶圓沉積和晶圓室清潔的周期時間, 總共減少了 40% 以上.

更高的吞吐量和產量:除了縮短工藝時間之外, 研究還發現, 基于 Aston 端點的清潔周期在基于時間的解決方案中, 由于過度清潔而導致的腔室側壁超過蝕刻產生的顆粒很少. 基于較低的后處理顆粒污染, 預測總體產品產量提高.

設備和工藝協同優化 EPCO: 380億美元的長期制造優化機會

許多先進的制造工藝都需要設備和工藝協同優化 EPCO. 麥肯錫公司 McKinsey & Co. 在2021年發表的一篇論文表明, 利用人工智能 AI 和機器學習 ML 進行半導體制造優化, 通過提高產量和提高吞吐量, 有望節省380億美元的成本. 麥肯錫強調, 幫助企業實現這些好處的干預點之一是調整工具參數, 使用當前和以前步驟的實時工具傳感器數據, 使 AI/ML 算法優化工藝操作之間的非線性關系. 成功部署 AI/ML 的關鍵是可操作的實時數據.

上海伯東日本 Atonarp Aston? 質譜儀原位實時分子診斷和云連接數據是實現這一能力的關鍵技術, 從而解鎖半導體 EPCO 的潛力.

AtonarpAston? 質譜儀優點

1. 耐腐蝕性氣體

2. 抗冷凝

3. 實時, 可操作的數據

4. 云連接就緒

5. 無需等離子體

6. 功能: 穩定性, 可重復性, 傳感器壽命, 質量范圍, 分辨率, 最小可檢測分壓, 最小檢測極限 PP,靈敏度 ppb, 檢測速率.

AtonarpAston? 質譜儀半導體行業應用

1. 介電蝕刻: Dielectric Etch

2. 金屬蝕刻: Metal Etch EPD

3. CVD 監測和 EPD: CVD Monitoring and EPD

4. 腔室清潔 EPD: Chamber Clean EPD

5. 腔室指紋: Chamber Fingerprinting

6. 腔室匹配: Chamber Matching

7. 高縱橫比蝕刻: High Aspect Ratio Etch

8. 小開口面積 <0.3% 蝕刻: Small Open Area <0.3% Etch

9. ALD

10. ALE

若您需要進一步的了解Atonarp Aston?在線質譜分析儀詳細信息或討論, 請聯絡

上海伯東版權所有, 翻拷必究

審核編輯黃宇

-

分析儀

+關注

關注

0文章

1763瀏覽量

54684 -

質譜

+關注

關注

0文章

21瀏覽量

9739

發布評論請先 登錄

大模型 ai coding 比較

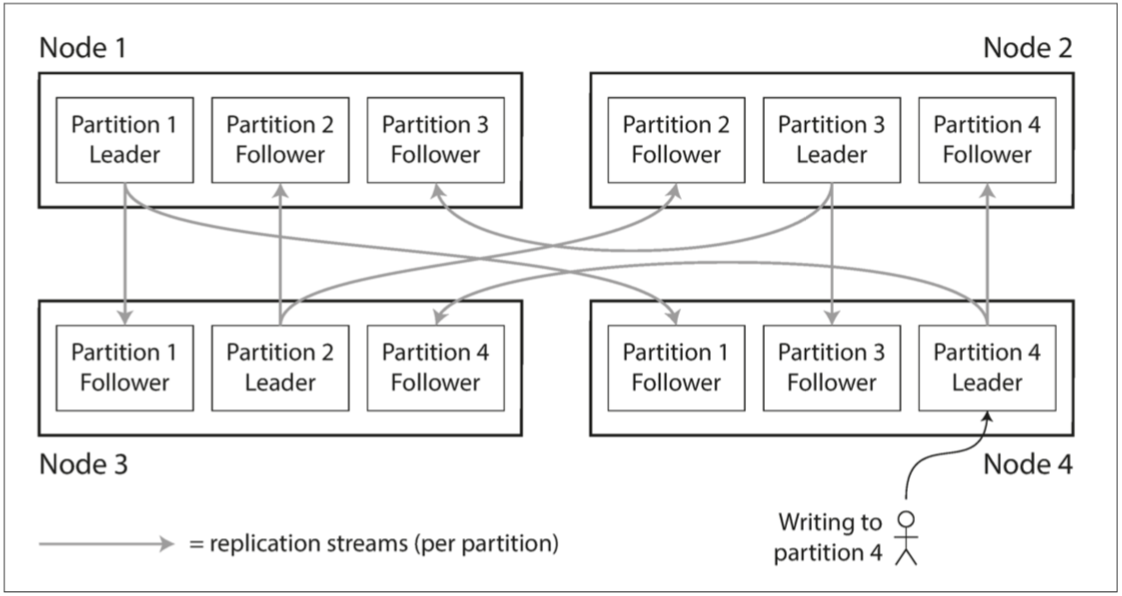

用“分區”來面對超大數據集和超大吞吐量

使用羅德與施瓦茨CMX500的吞吐量應用層測試方案

SDRO1250-8介質振蕩器Synergy

VirtualLab Fusion:分層介質元件

電子束對Low-K材料有什么影響

CY7C65211 作為 SPI 從機模式工作時每秒的最大吞吐量是多少?

如何在Visual Studio 2022中運行FX3吞吐量基準測試工具?

FX3進行讀或寫操作時CS信號拉低,在讀或寫完成后CS置高,對吞吐量有沒有影響?

Aigtek高光回顧!第二十屆全國電介質物理、材料與應用學術會議!

PCB的介質損耗角是什么“∠”?

VirtualLab Fusion應用:分層介質元件

Low-K材料在芯片中的作用

Aston? 過程質譜提高 low-k 電介質沉積的吞吐量

Aston? 過程質譜提高 low-k 電介質沉積的吞吐量

評論