我們總能從各種渠道看到硅片的模樣,那散發著五彩光芒的硅晶圓仿佛在向世界訴說著埋在晶圓表面下面那幾十億個晶體管的故事。然而我們日常看到的芯片并不是這樣子的。它們有的連接著密集的銀白色針腳,有的就是一塊純黑色的方塊一樣趴在PCB板上。其實芯片原本的樣子沒有變,它們只是被“放”在了保護殼里。放在保護殼里的這個過程,就是芯片封裝。

別小看封裝這個過程,它與芯片在最終使用階段時的體積大小和穩定性息息相關。尤其是目前芯片制程逐漸達到技術瓶頸,摩爾定律已經不能完全描述集成電路技術進步,要想讓芯片在工藝層面用更小的體積獲得更好的性能,成本逐漸增高。在智能手表、高性能移動設備普及的今天,曾經的“大老粗”芯片早已無法適應今天的使用環境,先進封裝或成為繞開摩爾定律的關鍵。

本文將帶你認識封裝技術的發展,以及了解封裝技術的未來展望。

為什么要封裝?

其實,要弄懂芯片封裝技術的變遷,只要了解為什么需要封裝。

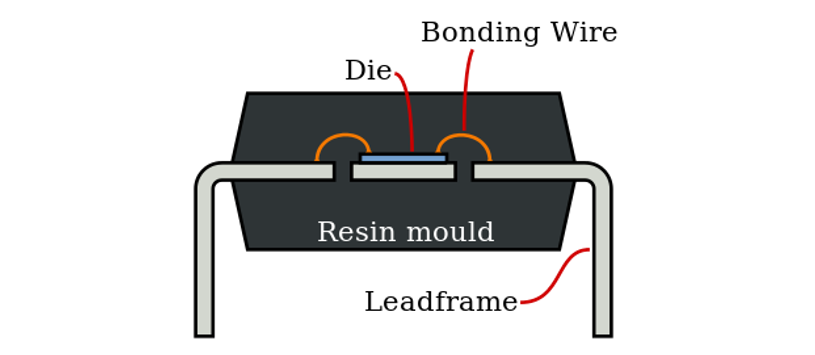

所謂封裝就是把集成電路裝配為芯片最終產品的過程,對于芯片來說,封裝是必須的,也是至關重要的。

1

晶片需要保護。

芯片電路非常微小也十分脆弱,封裝可以有效保護芯片表面以及內部電路免受外界損害以及干擾。此外,封裝還可以緩解內部芯片與外部基板之間的熱膨脹系數不同導致的應力,用來防止芯片損壞。

2

芯片與基板之間需要建立電氣連接。

芯片對外接腳往往是亞微米級別的,而外部引腳可達上百微米,封裝在這里起著由小到大、由難到易、由復雜到簡單的變換作用,從而可使操作費用及材料費用降低,而且能提高工作效率和可靠性。

3

芯片需要標準化、規格化。

標準化的芯片,有著固定的尺寸、形狀、引腳數量等參數,便于配合印刷電路板,且生產設備通用,可進行流水線制造。

總的來說,芯片封裝有著保護芯片,連接基板,標準化生產等優點。封裝技術的迭代也基于這幾點進行技術革新。

芯片封裝,從“毛毛蟲”到“小而美”

從應用的角度看,好的封裝技術可以實現更小的體積,更快的速度,以及更多的觸點。早期封裝的變化過程,就是體積的變小史。

集成電路剛剛誕生的六七十年代,人們對于芯片的印象往往是寬大的引腳,細長的形狀,其實這就是芯片最早的封裝方式,即DIP(Dual In-line Package)雙列直插式封裝,絕大多數中小規模集成電路都采用這種封裝形式。它通常采用長方形外形,兩側有并排的金屬針腳。最早的DIP包裝元件是由飛兆半導體(Fairchild)公司的Bryant Buck Rogers在1964年時發明,首個元件有14個引腳,采用此類封裝的半導體元件可以接在印刷電路板電鍍的貫穿孔中,或是插入在DIP插座(socket)上。早期芯片,例如8086、8088等CPU都采用了DIP封裝。不過這種技術密度、頻率難以提高,無法滿足高效自動化生產的要求,且芯片面積與封裝面積的比值較大,體積也很大。

圖源 | 維基百科

更多的觸點永遠是芯片封裝技術追求的目標。

80年代開始,DIP封裝的兩排針腳已經不能滿足芯片與外界交流的需求,SMT表面貼裝時代到來讓芯片封裝有了更多發揮空間。SMT技術是一種將無引腳或短引線表面組裝元器件安裝在印制電路板的表面或其它基板的表面上,通過再流焊或浸焊等方法加以焊接組裝的電路裝連技術。SMT工藝包括絲印、點膠、貼裝、固化、回流焊接、清洗、檢測等步驟。相比前代封裝技術,SMT組裝密度更高,體積更小,重量更輕。

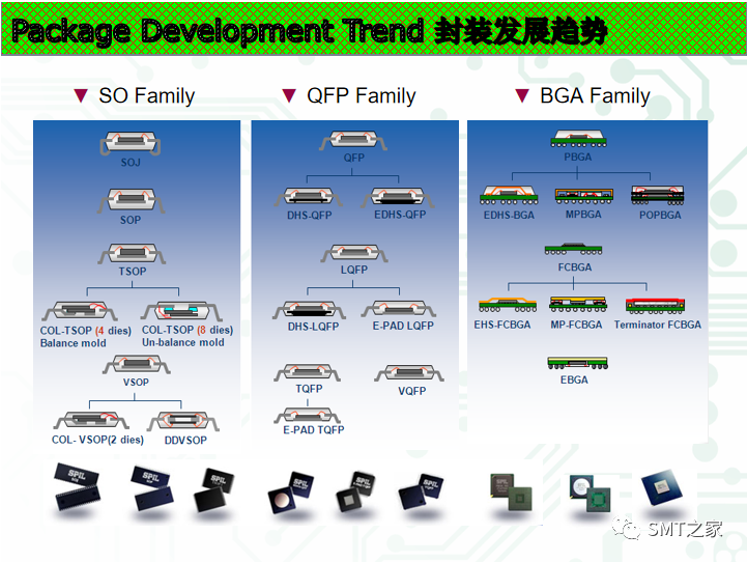

SOP(Small Out-Line Package小外形封裝)封裝是一種常見的表面貼裝形式,引腳從封裝兩側引出呈海鷗翼狀或L狀。SOP與DIP封裝的外表很像,從功能上也是沒有區別的,只是在芯片焊接階段,由于SOP引腳小,焊接難度會比DIP大一點,不過SOP的價格相比DIP也便宜一點。SOP封裝還逐漸派生出了許多其他的封裝類型,例如SOJ(J型引腳小外形封裝)、TSOP(薄小外形封裝)、TSSOP(薄的縮小型SOP)等。

QFP封裝,中文含義叫方型扁平式封裝技術(Quad Flat Package),該技術實現的CPU芯片引腳之間距離很小,引腳很細,一般大規模或超大規模集成電路采用這種封裝形式,引腳中心距離有1.0mm、0.8mm、0.65mm、0.5mm、0.4mm、0.3mm 等多種規格,總數一般都在100以上。QFP及其他派生封裝技術的可以更有效的利用空間,高度與體積都縮小了很多。

90年代面積陣列封裝出現。PGA、BGA等封裝技術逐一應用,在縮減體積的同時提高了系統性能。

PGA(Pin Grid Array)插針網格陣列是一般用戶很熟悉的封裝形式,很多老款的CPU都采用PGA封裝,其最大的特點就是背面布滿針腳。這種類型的封裝底部布滿針腳,使用時需要將整塊芯片放置于對應的卡座內,不過缺點很明顯,就是容易“斷腳”,后來逐漸被針腳在PCB板上的平面網格陣列封裝LGA(Land grid array)替代。

BGA改良自PGA。BGA(Ball Grid Array)球柵陣列封裝是一種表面黏著封裝技術,相比DIP以及QFP封裝技術,BGA可以容納更多的接腳,整個裝置的底部表面可全作為接腳使用,而不是只有周圍可用,比起QFP等周圍限定的封裝類型還具有更短的平均導線長度與更好的高速效能,與TSOP相比,BGA具有更小的體積、更好的散熱和電學性能,并極大地提高了每平方英寸的存儲容量。因此由該技術實現封裝的CPU信號傳輸延遲小,適應頻率可以提高很大。和PGA相比,BGA一般直接焊接在PCB板上,拆卸焊接需要專用的BGA修復臺,但價格也比PGA更便宜。

圖源 |SMT之家

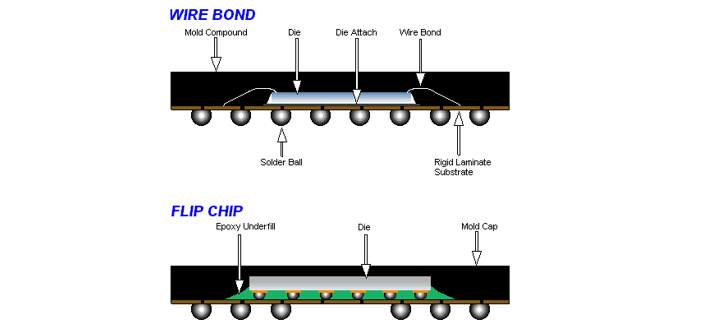

從最開始的DIP封裝到CPU使用的BGA、LGA型封裝,我們可以明顯的看到芯片的體積在逐步縮小,與外界交換信息的針腳也在增多。然而這些封裝技術都不能擺脫wire bond的限制,也就讓芯片的功率上限較低,也難以承受超高頻率的運算性能。21世紀的新封裝技術將解決這個問題。

封裝,不止關注體積

進入21世紀后,移動設備對于芯片的需求逐漸提升。芯片制程沿著摩爾定律快速發展,這同時也對封裝技術提出新的考驗。為了進一步提升芯片的整體性能,倒晶封裝技術Flip Chip出現(或稱覆晶封裝、倒裝芯片、controlled collapse chip connection、c4等)。以往封裝是將晶片置放于基板(chip pad)上,再用引線焊接(wire bond)將晶片與基板上的焊盤連接。Flip chip是先將晶片連接到凸塊(bump),然后將晶片翻轉過來使凸塊與基板(substrate)直接連結而得其名。Flip Chip與傳統wire bond封裝技術相比,晶片與基板的互連形式要方便的多,芯片焊盤位于芯片正下方,因此與基板之間連接路徑較短,能顯著提高電氣性能,更提高了I/O數量;芯片底部區域陣列焊接點的密度也更高,因此整顆芯片的尺寸能顯著縮小。此外,晶片倒裝后沒有引線的限制,芯片整體高度更低,外部散熱也可以直接作用于晶片之上。

Flip chip技術與其他封裝,例如BGA封裝技術并不是相互獨立的,應用Flip chip技術的BGA同樣能有效降低芯片體積。

圖源 | integra報告

Flip chip有著尺寸、I/O密度、傳輸性能、散熱能力以及生產效率等諸多優點,不過先進封裝也有更“先進”的問題需要解決。

Flip chip技術面對的最大難題就是解決芯片翹曲,這在芯片超薄化后成為影響封裝良率的關鍵問題。Flip chip的組裝過程需要將芯片上的焊點與基板上的焊盤進行對位,然后使用回流焊工藝在芯片和基板焊盤間形成焊球,再在芯片與基板間的空隙中填充底部填充膠(點膠),最終實現芯片與基板間的電氣連接。因此這個流程的第一步,焊點與焊盤的對應十分重要。若芯片產生過大的翹曲會在組裝過程中導致錫球無法對接,出現開路。目前,采用新材料做基板可以有效降低熱膨脹系數,減小翹曲度。此外采用銅柱技術(CopperPillar)也可以進一步縮小焊點間距。

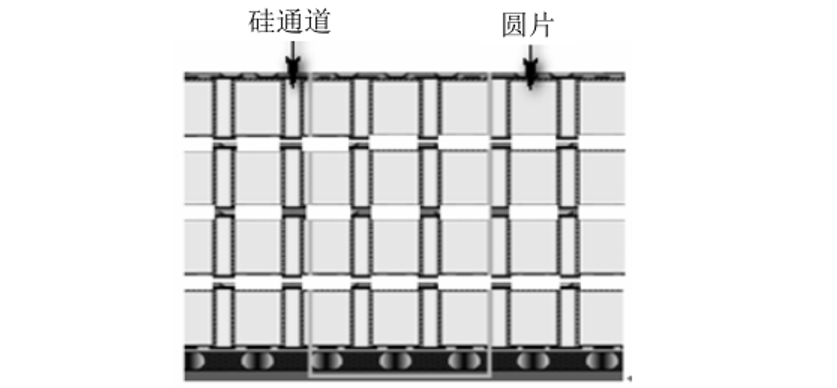

隨著各種智能設備小型化的發展,要求作為終端的傳感器更便攜化、多功能化。因此,將更多功能集成于單個芯片內成為降低體積、提升性能的高效方式。因此,疊層3D封裝出現了。

目前,芯片疊層共有三種形式:芯片與芯片的堆疊(Die to Die,D2D),芯片與晶片的堆疊(Die to Wafer,D2W),晶片與晶片的堆疊(Wafer to Wafer,W2W)。

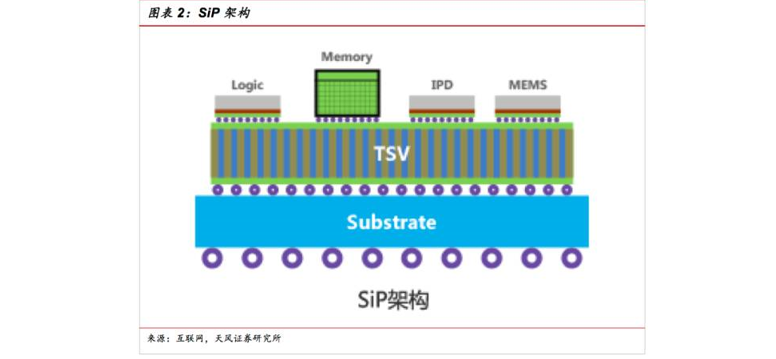

D2D利用傳統的引線連接技術,將芯片在垂直方向上堆疊起來進行封裝,應用傳統的封裝技術即可解決。D2W則需要Flip chip技術來連接上下兩層。W2W的上下兩層之間通過直徑在10微米以下的硅通道相連接,這種技術也稱為TSV(Through silicon via)。與其他技術不同,TSV能夠使芯片在三維方向堆疊的密度更大、外形尺寸更小,并且大大改善芯片速度和降低功耗,是目前3D芯片的主流發展方向。

圖源 | 中國集成電路報告

除了垂直封裝技術外,在同一個封裝腔體內堆疊多個3D封裝也是一種技術方案。PIP(Package in Package)封裝內封裝逐漸流行。目前該項技術主要用于SD卡、XD卡等儲存芯片的封裝上。

先進封裝,超越摩爾定律的關鍵賽道

目前,半導體業界逐漸意識到了制程不會無限縮小下去,晶體管也不可能無限增加下去。摩爾定律首先是一條經濟上的定律,然后才是工程科學方面的定律。人們專注于提高芯片制造技術達到瓶頸之后,與之對應的封裝技術發展也同樣慢了下來。封裝還是要回到原點,也就是文章開頭所提到的:為什么要封裝?什么才是好的封裝?

好的封裝,不僅能保護芯片,還具有更小的體積,以及更好的電氣性能。因此,封裝的發展面臨了三條路可以選擇:More Moore,More than Moore,Beyond Moore。

More Moore是沿著摩爾定律這條路一直走下去,鉆研更精細、更先進的封裝方案,這也往往面臨著高昂的制造成本,也就是SoC的發展路徑。More than Moore則是繞過摩爾定律,采用其他技術達到同樣的更小、更先進的目標。Beyond Moore則需要超越現有芯片體系,或許只能在非硅基半導體上實現。

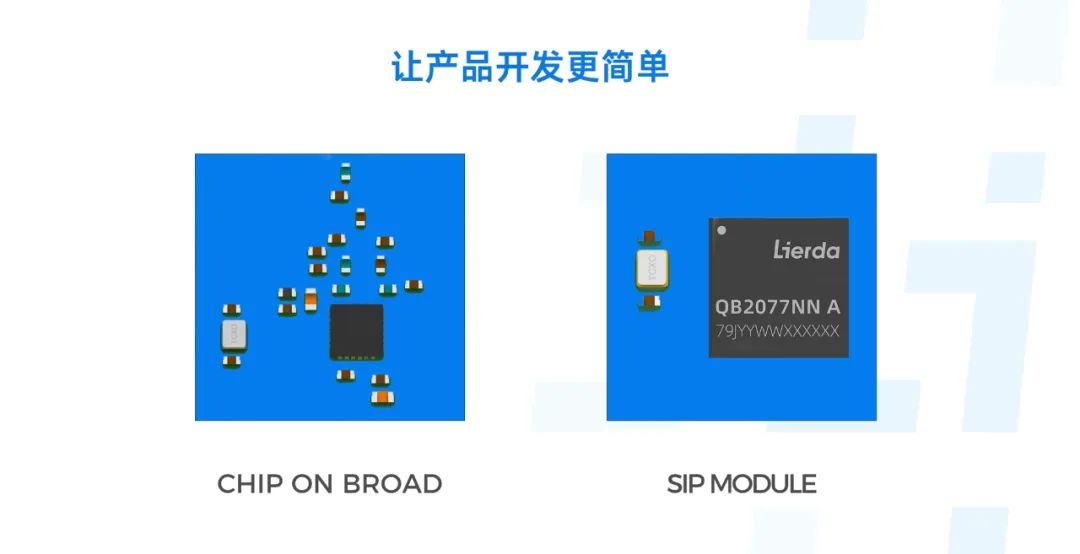

就目前來說,More than Moore是一項最經濟也最便捷的選擇。SIP(System In a Package)系統級封裝是目前芯片封測廠商的主流之選。它是一種是將多種功能晶圓,包括處理器、存儲器等功能晶圓根據應用場景、封裝基板層數等因素,集成在一個封裝內,從而實現一個基本完整功能的封裝方案。

圖源 | 知乎

SIP與SoC對比,兩者均將一個包含邏輯組件、內存組件,甚至包含被動組件的系統,整合在一個單位中。而SIP則是從封裝角度出發,利用并排或疊加的方式,將不同制程的芯片集成在一起。我們知道,越高的制程也擁有越高的制造成本,SIP可以僅在關鍵模塊上使用高端制程,例如CPU、GPU等,在其他模塊上,例如WIFI、觸控模塊上使用成熟制程,這將極大的降低制造成本。

此外,SIP還將繞過PCB板載體,解決因為PCB自身的先天不足帶來系統性能遇到瓶頸的問題。存儲芯片和處理器之間也能做到更快速的數據交換,真正做到存算一體化。

利爾達物聯網發力SiP封裝技術

利爾達物聯網響應市場需求,推出基于LoRa的 SiP芯片模組。該模組基于SX1262 DIE平臺研發,包含QB20-C7和QB20-C8兩款,僅工作頻段與發射電流存在區別,滿足歐標和美標用戶需求。

模組內部集成LoRa射頻收發器SX1262和射頻前端匹配電路,支持LoRa和FSK調制,可選擇外接32MHz TCXO或無源晶振使用,擁有低成本、多頻段、低功耗、遠距離 、高靈敏度 、SPI接口、易使用、數據兼容 、高速率等特性。

利爾達物聯網還為QB20配備了EVK,包含開發板、轉接板、天線、拉距例程等部件,主要用于前期的性能評估和拉距。

相較而言,QB20具備以下優勢:

1、采用全新一代LoRa芯片設計,功耗相較上一代芯片降低50%;

2、采用PCB基材設計,成本低,交期短,免去缺貨煩惱;

3、小體積,高等級ESD防護設計,尺寸縮小但可靠性“不縮水”;

4、模組晶振外置,用戶可以根據應用場景需求選擇有源晶振或者無源晶振,性能、交期、成本盡在掌握;

5、免去不同頻段不同PCB設計的煩惱,一個封裝,走遍全球。

利爾達SiP芯片能提高產品集成度和功能多樣化,能充分滿足終端應用對芯片輕薄、低功耗、高性能的需求,同時大幅降低芯片成本,在智能三表 、智慧停車、環境監測 、熱控閥、低壓電器 、智慧農業等領域均得到了廣泛應用。

當前我國的倉儲行業體量還在不斷增大,再加上智能倉芯片封裝,已經從剛起步時僅作為保護作用的外殼,成為今天提升芯片電氣性能,繞過摩爾定律發展的關鍵。后摩爾時代,芯片封裝技術將成為解鎖未來半導體技術的關鍵。

-

芯片

+關注

關注

463文章

54012瀏覽量

466193 -

封裝

+關注

關注

128文章

9249瀏覽量

148646

發布評論請先 登錄

Chiplet,改變了芯片

當摩爾定律 “踩剎車” ,三星 、AP、普迪飛共話半導體制造新變革新機遇

先進封裝轉接板的典型結構和分類

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

晶心科技:摩爾定律放緩,RISC-V在高性能計算的重要性突顯

電力電子中的“摩爾定律”(2)

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

電力電子中的“摩爾定律”(1)

玻璃基板在芯片封裝中的應用

先進封裝工藝面臨的挑戰

瑞沃微先進封裝:突破摩爾定律枷鎖,助力半導體新飛躍

摩爾定律走到盡頭后,廠商們開始卷封裝了

摩爾定律走到盡頭后,廠商們開始卷封裝了

評論