1GPMC并口簡介

GPMC(General Purpose Memory Controller)是TI處理器特有的通用存儲器控制器接口,是AM335x、AM437x、AM5708、AM5728等處理器專用于與外部存儲器設備的接口,如:

●異步,同步,和頁面模式(僅適用于非復用模式)突發NOR閃存設備。

●NAND閃存。

●ADC器件。

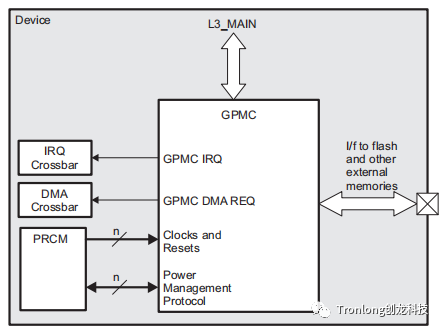

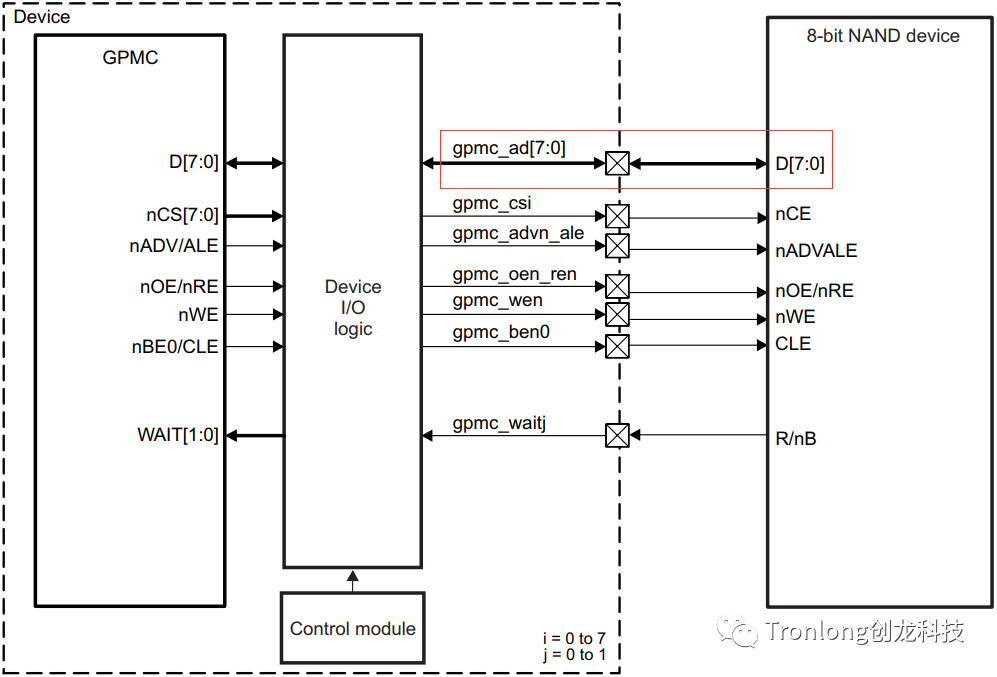

圖 1GPMC概述

2GPMC并口特點

為什么工業領域在與FPGA/ADC通信的時候,更喜歡使用GPMC接口呢?本文給出3個理由,那就是:高帶寬、連接模式豐富、配置靈活。具體如下:

PS:下文將介紹基于AM570x GPMC的ARM + FPGA通信案例、多通道AD(AD7606/ADS8568)采集綜合案例。

(1)高帶寬,速率可達100MB/s以上

以AM57x為例,通過GPMC接口與FPGA連接,采用DMA的方式讀取FPGA端的數據,速度可達69MB/s,實際上通過配置GPMC接口的時序參數和不同工作模式,速率可超過100MB/s。

(2)連接模式豐富,靈活的8位和16位異步存儲器接口

由于有gpmc_ad[15:0] 16個信號引腳可支持地址線與數據線復用和非復用模式,這讓GPMC與外設的連接模式變得很豐富,可以和寬范圍的外部設備通信,如:

●外部異步或同步8-bit位寬內存或設備(非突發設備)

●外部異步或同步16-bit位寬內存或設備

●外部16-bit非復用NOR Flash設備

●外部16-bit地址和數據復用NOR Flash設備

●外部8-bit和16-bitNAND Flash設備

●外部16-bit偽SRAM(pSRAM)設備

下面介紹幾種連接模式。

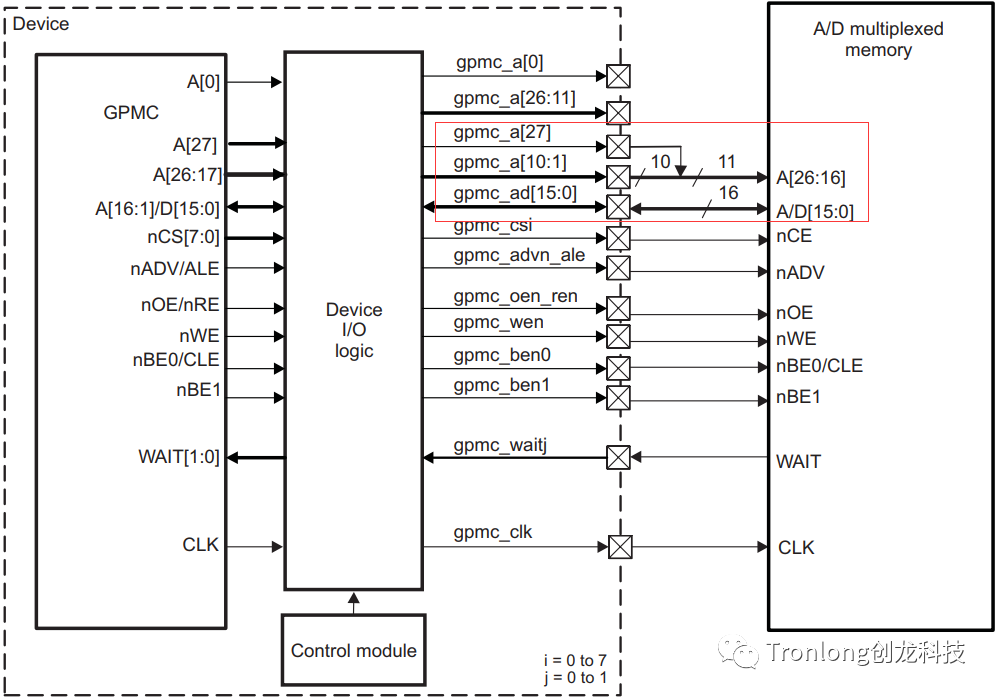

1)16-bit Address/Data Multiplexed(地址線與數據線復用模式)

圖 2

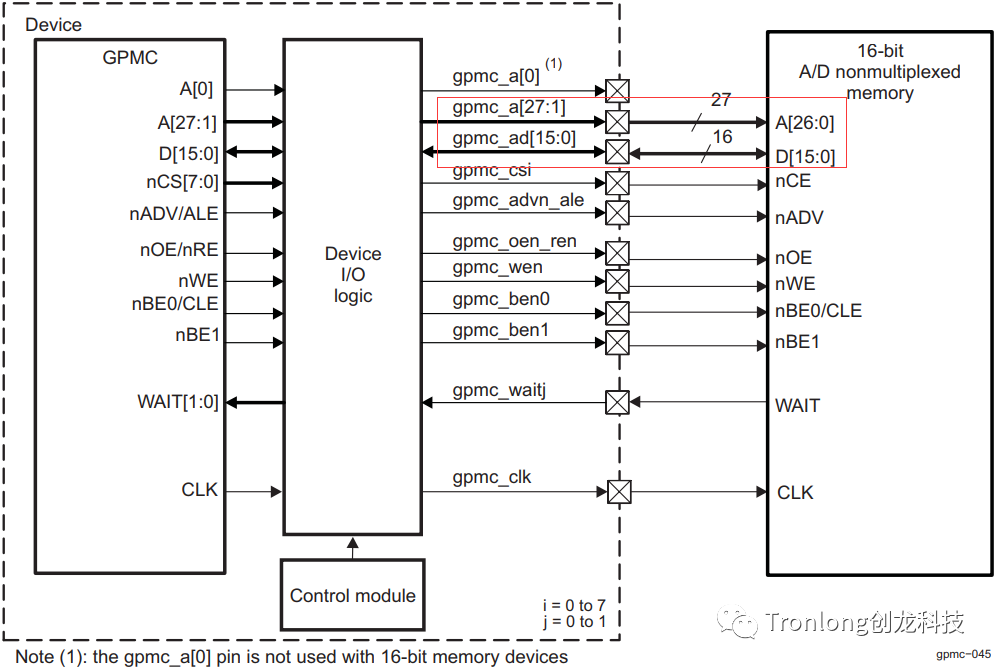

2)16-bit Nonmultiplexed(地址線與數據線非復用模式)

圖 3

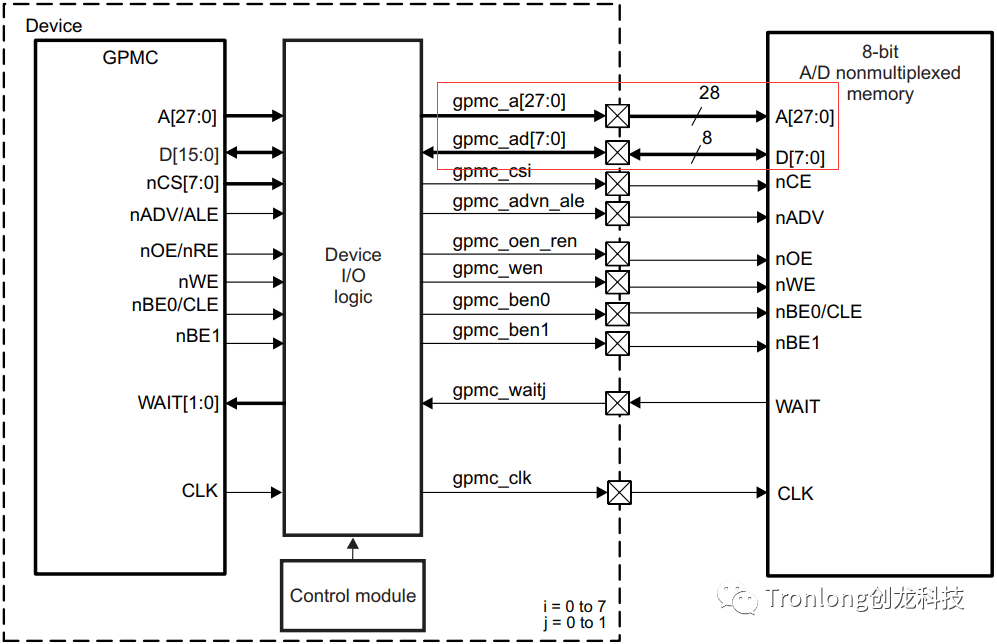

3)8-bit Nonmultiplexed(地址線與數據線非復用模式)

圖 4

4)8-bitNAND(僅使用數據線模式)

此模式適用于無需地址線的場合,例如GPMC與NAND FLASH連接。NAND FLASH無需地址線,通過數據線D[x:0]發送讀寫命令,進行數據讀取/寫入。

圖 5

(3)配置靈活,具有多達8個片選

GPMC基本編程模型提供了最大的靈活性,以支持八個可配置片選中不同的時序參數和位寬配置。可根據外部設備的特點,使用最佳的片選設置。

●可選擇不同的協議,以支持通用異步或同步隨機訪問設備(NOR閃存,SRAM)或支持特定的NAND器件。

●地址和數據總線可在同一個外部總線上復用。

●讀和寫訪問可獨立定義為異步或同步。

●系統請求(字節,16位字,突發)是通過單次或多次訪問進行。外部設備訪問配置文件(單或多個優化的突發長度,本地包或仿真包)是基于外部設備特性(支持協議,總線寬度,數據緩沖區大小,本地包支持)。

●系統突發讀或寫請求是同步突發(多個讀,或多個寫)。在沒有突發或頁面模式時是由外部存儲器或ASIC設備支持,系統突發讀或寫請求轉換為連續單一的同步或異步訪問(單一讀,或單一寫)。僅在單一同步或 單一異步讀或寫模式下支持8位寬的設備。

為了模擬一個可編程的內部等待狀態,一個外部等待引腳可被監控,以在開始(初始訪問時間)和突發訪問期間動態的控制外部訪問。

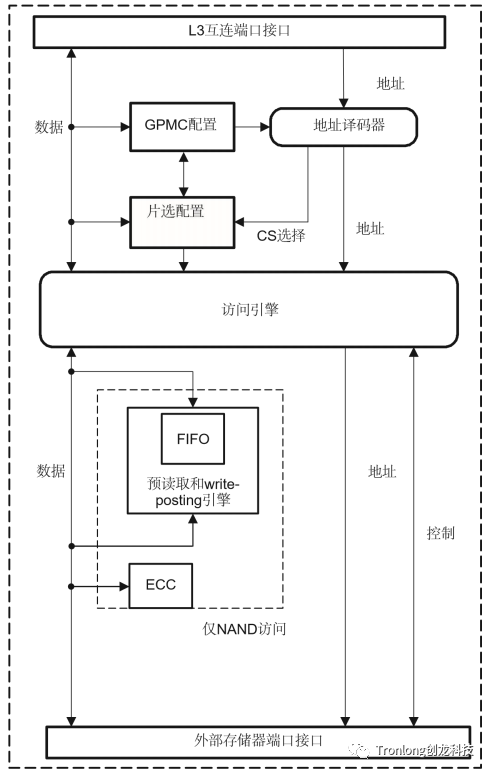

圖 6GPMC框圖

3GPMC并口應用案例

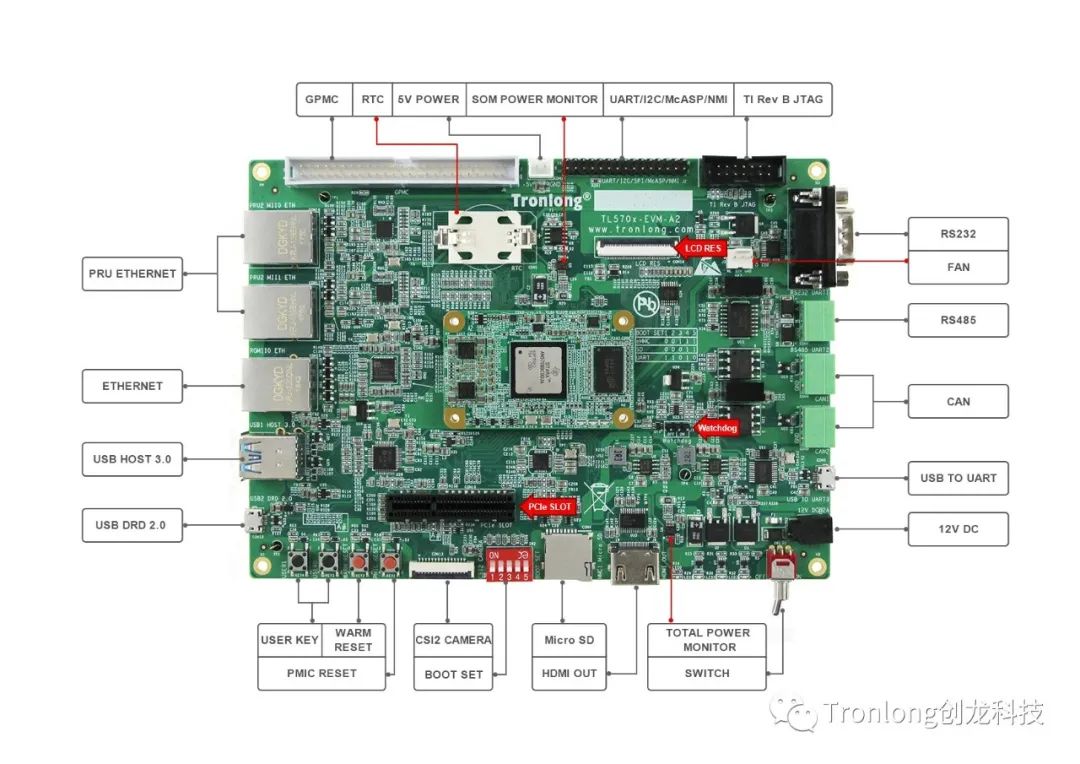

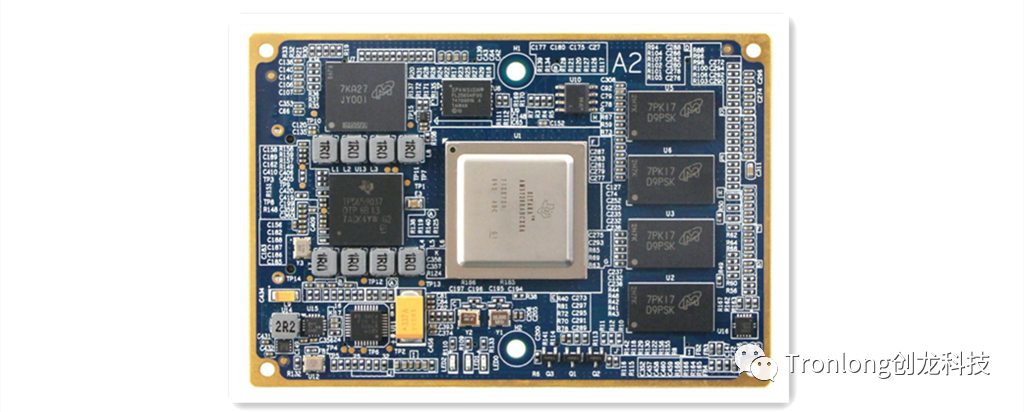

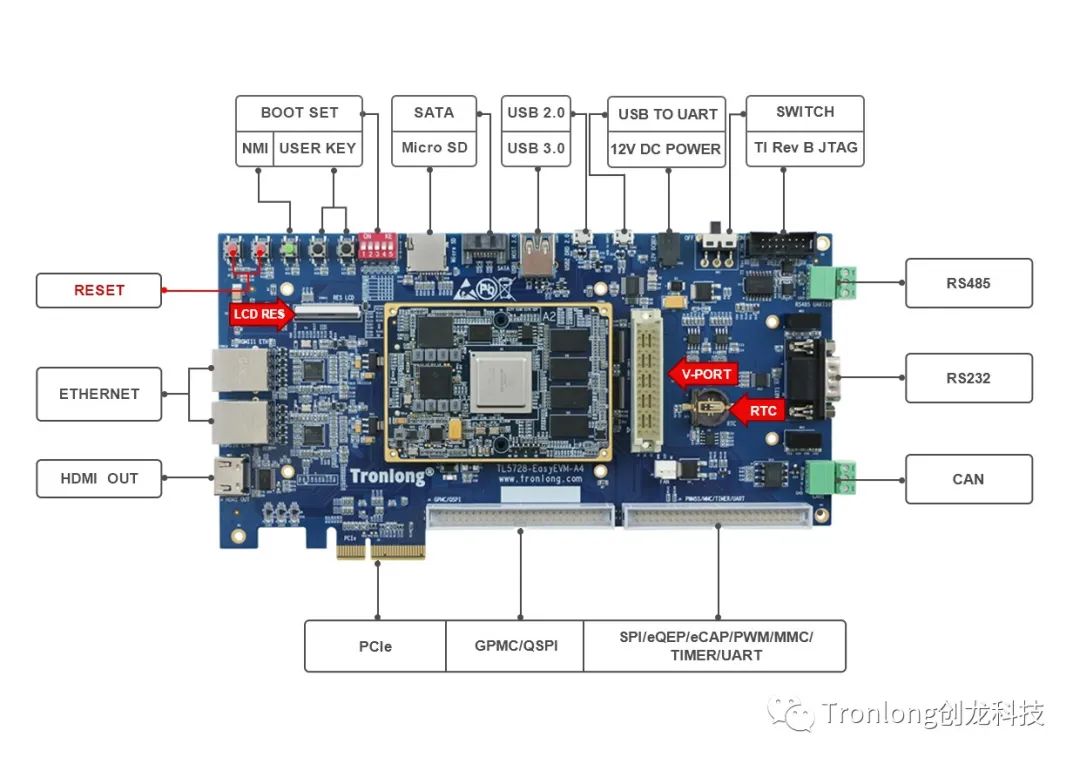

創龍科技基于AM5708、AM5728設計的工業評估板——TL570x-EVM、TL5728-EasyEVM,由核心板和評估底板組成。核心板經過專業的PCB Layout和高低溫測試驗證,穩定可靠,可滿足運動控制、工業PC、機器視覺、智能電力、視頻監測等工業應用環境。

* AM5708

圖7SOM-TL570x核心板

圖8TL570x-EVM開發板

* AM5728

圖9SOM-TL5728核心板

圖10TL5728-EasyEVM開發板

圖 11

本文講解基于AM570x GPMC的ARM + FPGA通信案例、多通道AD采集綜合案例。

3.1基于GPMC的ARM + FPGA通信案例

3.1.1案例功能

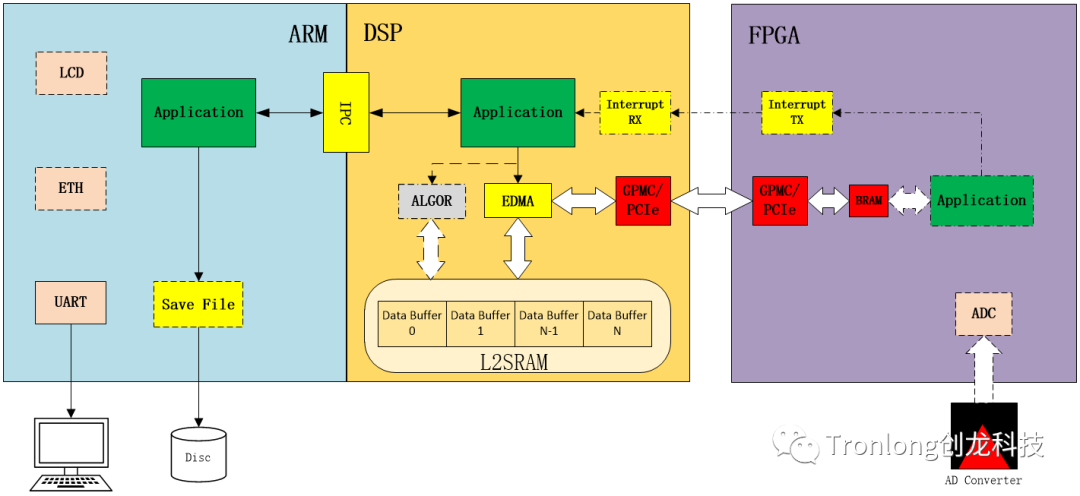

DSP端使用EDMA將數據搬運到指定的內存空間物理地址(GPMC片選基地址),再將數據讀取回來并保存到DSP端L2SRAM,并校驗數據讀寫的正確性、計算數據讀寫速率。ARM端通過MessageQ發送讀寫地址與讀寫大小到DSP端,DSP端讀寫對應內存空間,并返回傳輸時間及傳輸速率到ARM端。GPMC的初始化由ARM端驅動程序實現。

程序工作流程框圖如下所示。

圖 12

3.1.2案例測試

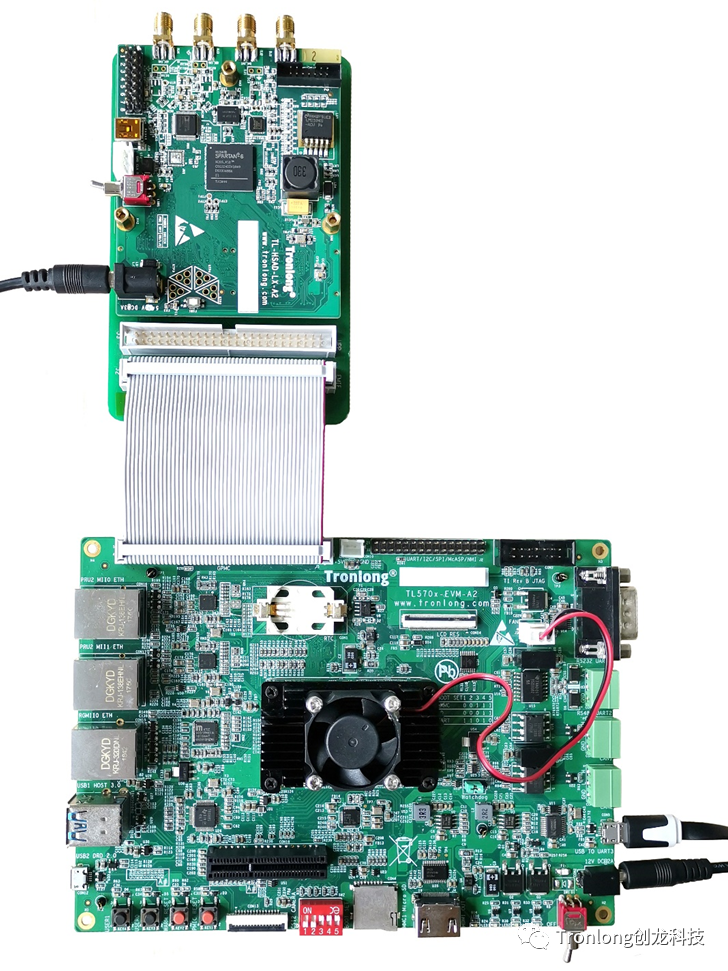

將TL-HSAD-LX采集卡通過TL-HSAD-LX-PinBoard轉接板和軟排線,插到TL570x-EVM評估板的GPMC拓展接口J5上,并使用5V2A電源給TL-HSAD-LX采集卡供電,硬件連接圖如下。

圖 13

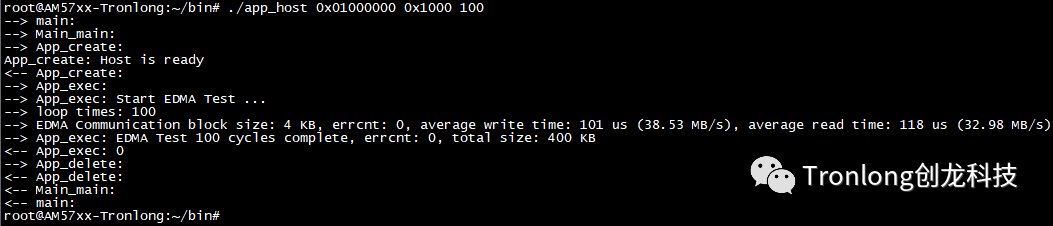

圖 14測試結果

EDMA單次傳輸數據大小為2KByte(0x800),總共循環100次。如需再次測試讀寫速度,請重新運行DSP端程序。

從上圖可看到本次測試的誤碼率為0%(errcnt: 0);平均寫入時間約為101us,寫入速率約為38.53MB/s;平均讀取時間約為118us,讀取速率約為32.98MB/s。

備注:本次測試板卡通過軟排線的形式連接,軟排線的長度會影響誤碼率和讀寫帶寬,目前測得最高速率為38.53MB/s(寫入速率)。如將FPGA設計于底板,最高速率可到69MB/s(寫入時間為28us)

3.2基于GPMC的多通道AD采集綜合案例

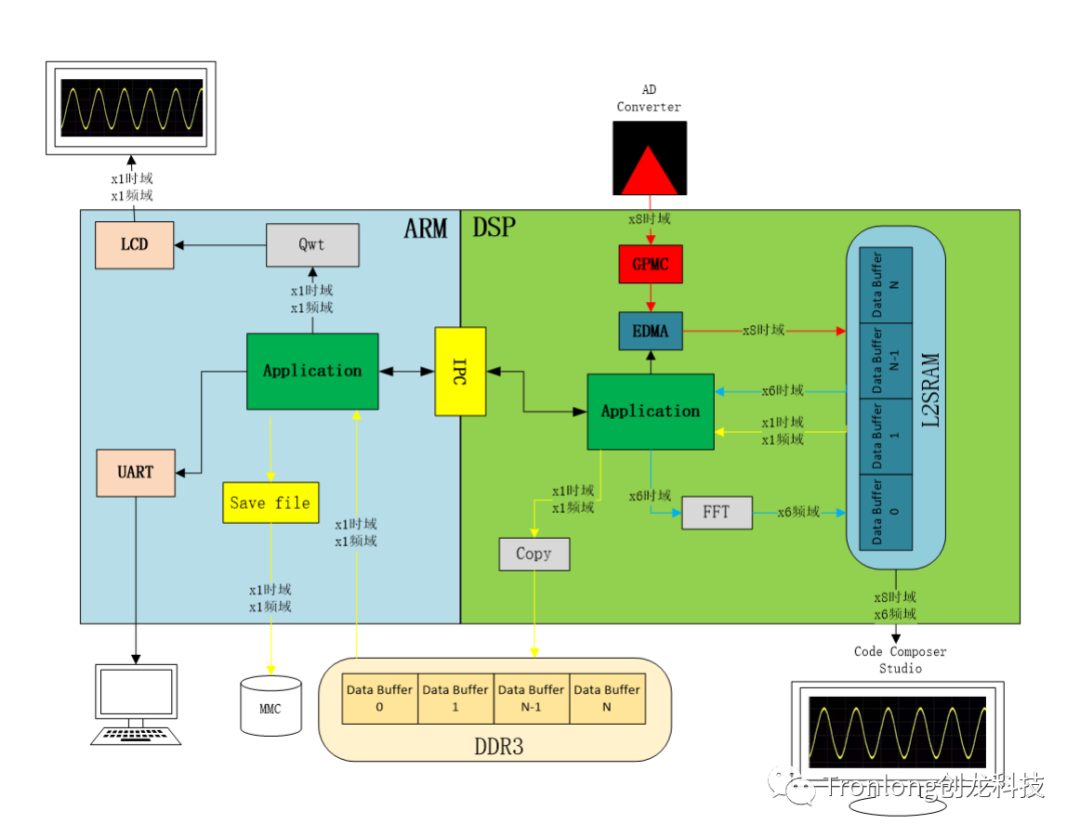

3.2.1案例功能

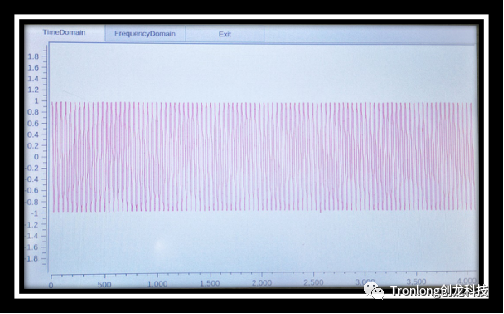

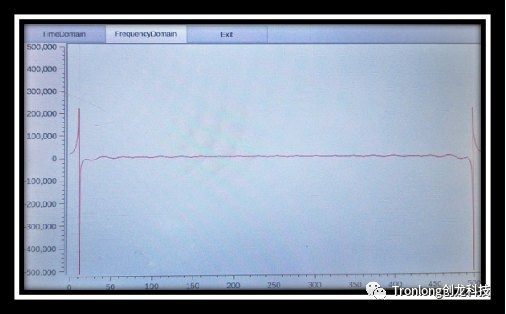

AM570x DSP端使用EDMA通過GPMC接口采集AD7606或ADS8568模塊8通道的AD信號,同時由DSP端對其中6通道的AD信號進行FFT處理,最后將8通道時域數據和經FFT處理的6通道頻域數據保存到DSP端L2SRAM中,可通過仿真器與CCS軟件查看對應通道的時域波形和頻域波形。

程序保存通道0的時域數據和經FFT處理的頻域數據至CMEM(共享內存)空間,通過IPC組件通知ARM端讀取該通道的時域數據和頻域數據,使用Qt在LCD顯示屏上進行波形繪制,最后將數據保存到文件中。

本案例默認配置AD7606模塊采樣周期為6us,即采樣率約為167KHz;配置ADS8568模塊采樣周期分別為5us,即采樣率為200KHz。程序工作流程框圖如下所示:

圖 15

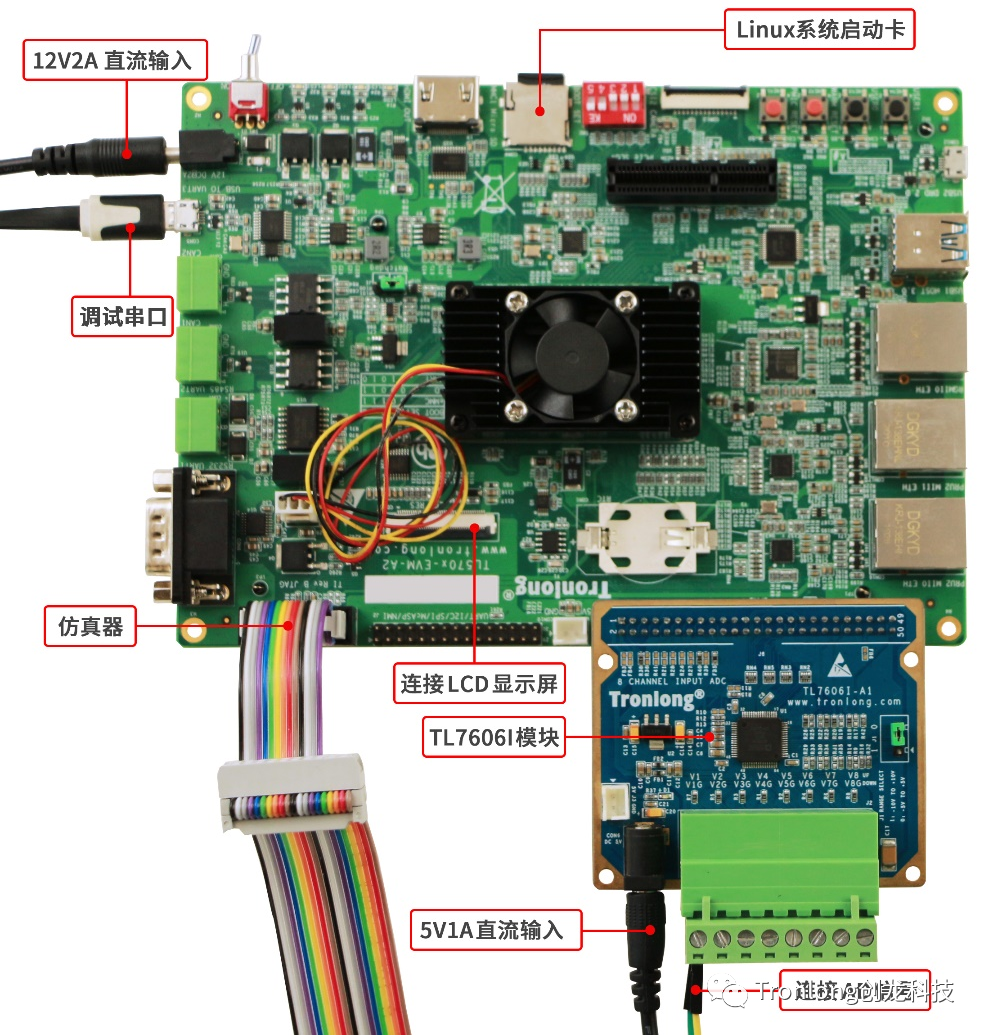

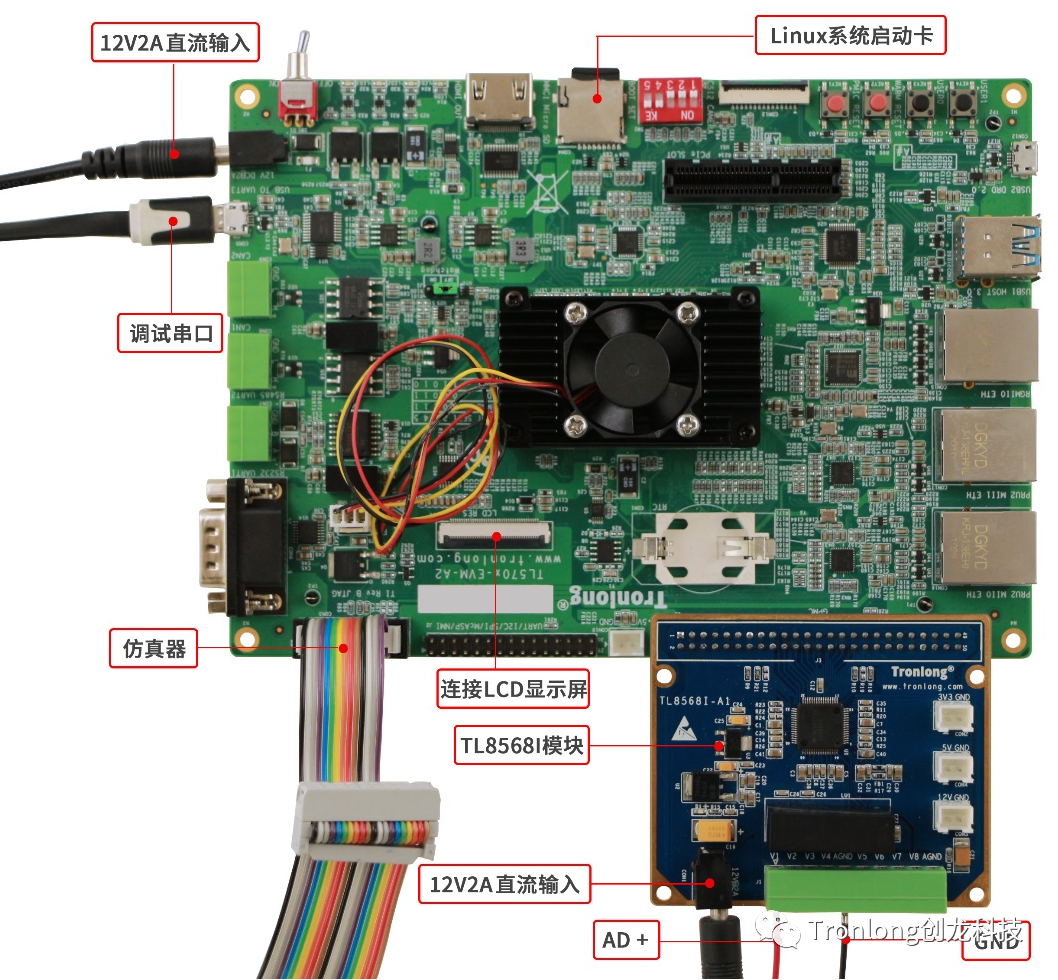

3.2.2案例測試

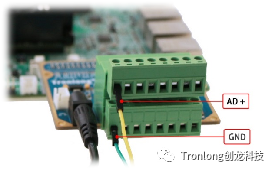

將Tronlong的TL7606I(AD7606)模塊或TL8568I(ADS8568)模塊插入評估板GPMC擴展接口,并對模塊進行獨立供電。TL7606I模塊使用5V電源供電,J1跳線帽連接到0,使用±5V量程。TL8568I模塊使用12V電源供電,軟件已配置為±12V量程。

將模塊的待測輸通道正確連接信號發生器,信號發生器輸出頻率為4KHz、峰峰值為2Vpp(即幅值為1V)的正弦波信號。待測信號電壓請勿超過模塊量程,否則可能會導致模塊損壞。評估板接入LCD顯示屏,并通過仿真器連接到PC機。硬件連接示意圖如下:

圖 16TL7606I模塊硬件連接示意圖

圖 17TL7606I模塊硬件連接示意圖

圖 18TL8568I模塊硬件連接示意圖

程序運行后,即可在LCD顯示屏上看到通道0的時域波形和頻域波形。

圖 19時域波形

圖 20頻域波形

-

ARM

+關注

關注

135文章

9573瀏覽量

392866 -

FPGA設計

+關注

關注

9文章

431瀏覽量

28190 -

嵌入式主板

+關注

關注

7文章

6107瀏覽量

37135

發布評論請先 登錄

LAT1602_STM32H7 的 3 個 ADC 時鐘同步方法

TI AM62L經典再進化!高能效,低功耗全新發布

使用變頻調速方案的10個理由

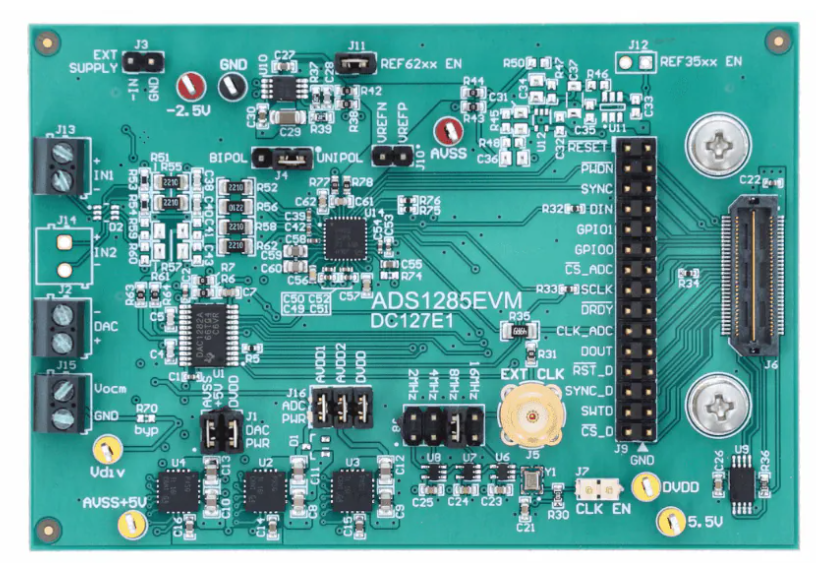

ADS1285EVM-PDK評估模塊技術解析:面向能源勘探的高精度32位ADC解決方案

每一個N型連接器,都是我與這世界握手的方式

TC3XX 的端口可以同時被 EvADC 和 DSADC 用于 ADC 轉換嗎?

FPGA利用DMA IP核實現ADC數據采集

Eplan編寫基于連接的線號命名格式要點記錄

RK3576 + FPGA并口通信方案,實測高達280MB/s

為何TI的GPMC并口,更常被用于連接FPGA、ADC?我給出3個理由

為何TI的GPMC并口,更常被用于連接FPGA、ADC?我給出3個理由

評論