6

復位要求和復位電路

共有十四種類型的復位。這些復位在Arm Cortex-M4器件和Arm Cortex-M33器件之間略有不同。

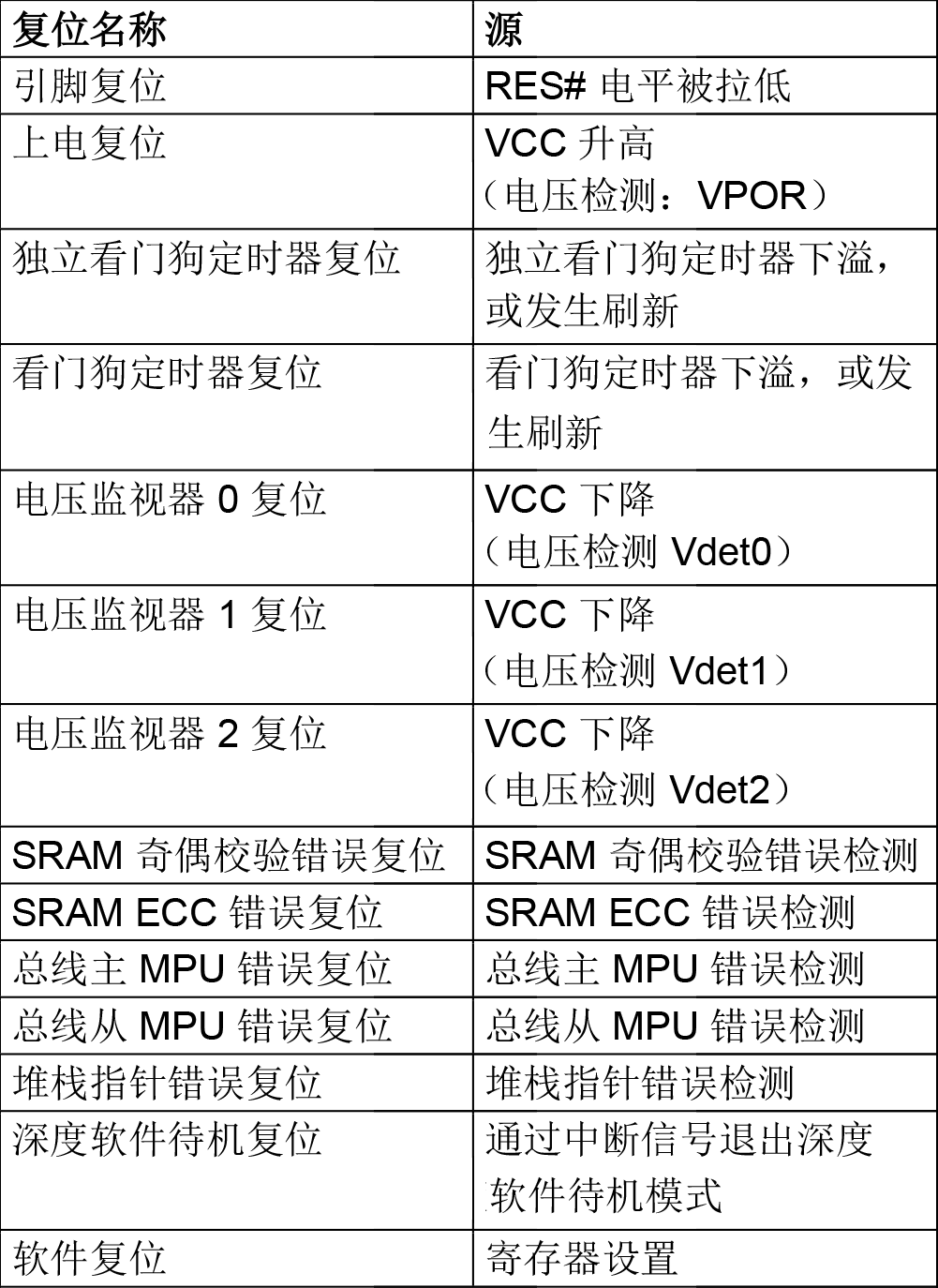

表11. Arm Cortex-M4器件復位

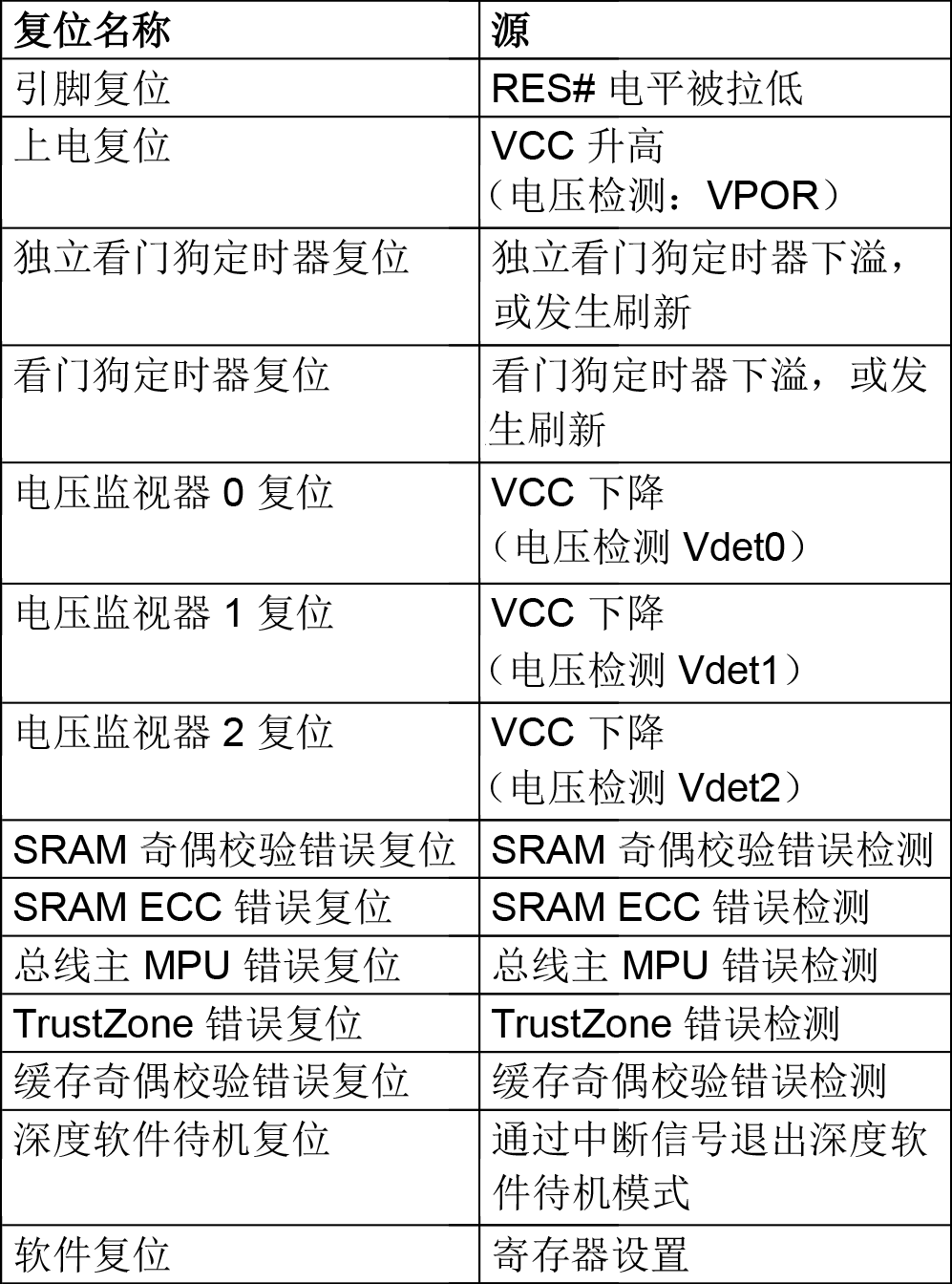

表12. Arm Cortex-M33器件復位

6.1 引腳復位

當RES#引腳電平被拉低時,所有處理都將中止,MCU進入復位狀態。要在運行中復位MCU,應在指定的復位脈沖寬度內將RES#保持為低電平。有關時序要求的更詳細信息,請參見《硬件用戶手冊》中“電氣特性”一章的“復位時序”部分。另請參見本系列文章的第2節“仿真器支持”,了解與調試支持相關的復位電路的詳細信息。

無需在RES#線路上使用外部電容,因為POR電路在內部將其保持為低電平以實現良好的復位,并且需要最小的復位脈沖來啟動此過程。

6.2 上電復位

有兩種情況會產生上電復位 (POR):

1

如果RES#引腳在接通電源后處于高電平狀態。

2

如果RES#引腳在VCC低于VPOR時處于高電平狀態。

在VCC超過上電復位電壓 (VPOR) 并經過上電復位時間 (tPOR) 之后,芯片將從上電復位狀態釋放。上電復位時間是允許外部電源和MCU達到穩定狀態的時間。有關電壓大小和時序的詳細信息,請參見《硬件用戶手冊》中“電氣特性”一章的“POR和LVD特性”部分。

由于POR電路依賴于RES#與VCC同時為高電平,因此請勿在復位引腳上放置電容。這將減慢RES#相對于VCC的上升時間,從而妨礙POR電路正確識別上電條件。

當電源 (VCC) 降至不超過VPOR時,如果RES#引腳為高電平,則會產生上電復位。在VCC上升到VPOR以上并且經過tPOR之后,芯片將從上電狀態釋放。

上電復位后,RSTSR0中的PORF位置1。引腳復位后,PORF清零。

這是由獨立看門狗定時器 (IWDT) 產生的內部復位。

當IWDT下溢時,可以選擇產生獨立看門狗定時器復位(可以改為產生NMI),并且RSTSR1中的IWDTRF位置1。短暫延遲(通常為320μs)后,將退出IWDT復位。

6.4 看門狗定時器復位

這是看門狗定時器 (WDT) 產生的內部復位。

當WDT下溢時,可以選擇產生看門狗定時器復位(可以改為產生NMI),并且RSTSR1中的WDTRF位置1。短暫延遲(通常為320μs)后,將退出WDT復位。

-

mcu

+關注

關注

147文章

18924瀏覽量

397994 -

瑞薩

+關注

關注

37文章

22481瀏覽量

90851

發布評論請先 登錄

深入解析MIC2212:雙μCap LDO與上電復位電路的卓越之選

MAX6443–MAX6452:具備長手動復位設置周期的微處理器復位電路

MAX6412 - MAX6420:低功耗單/雙電壓微處理器復位電路的設計指南

探索Renesas FPB - RA6E2:快速原型開發板的深度解析

【瑞薩RA6E2地奇星開發板試用】介紹、環境搭建、工程測試

【瑞薩RA6E2】評測開箱測試

【RA-Eco-RA6M4開發板評測】WDT實踐

【瑞薩RA6E2】開箱測試報告

【免費試用】瑞薩 RA6E2 開發板免費試用

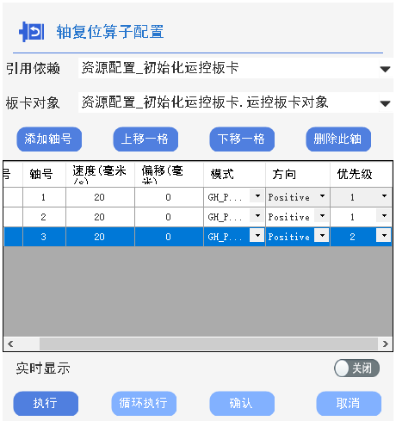

GraniStudio零代碼平臺軸復位算子支持多少個軸同時復位,有哪些回零模式?

RA6快速設計指南 [6] 復位要求和復位電路 (上)

RA6快速設計指南 [6] 復位要求和復位電路 (上)

評論