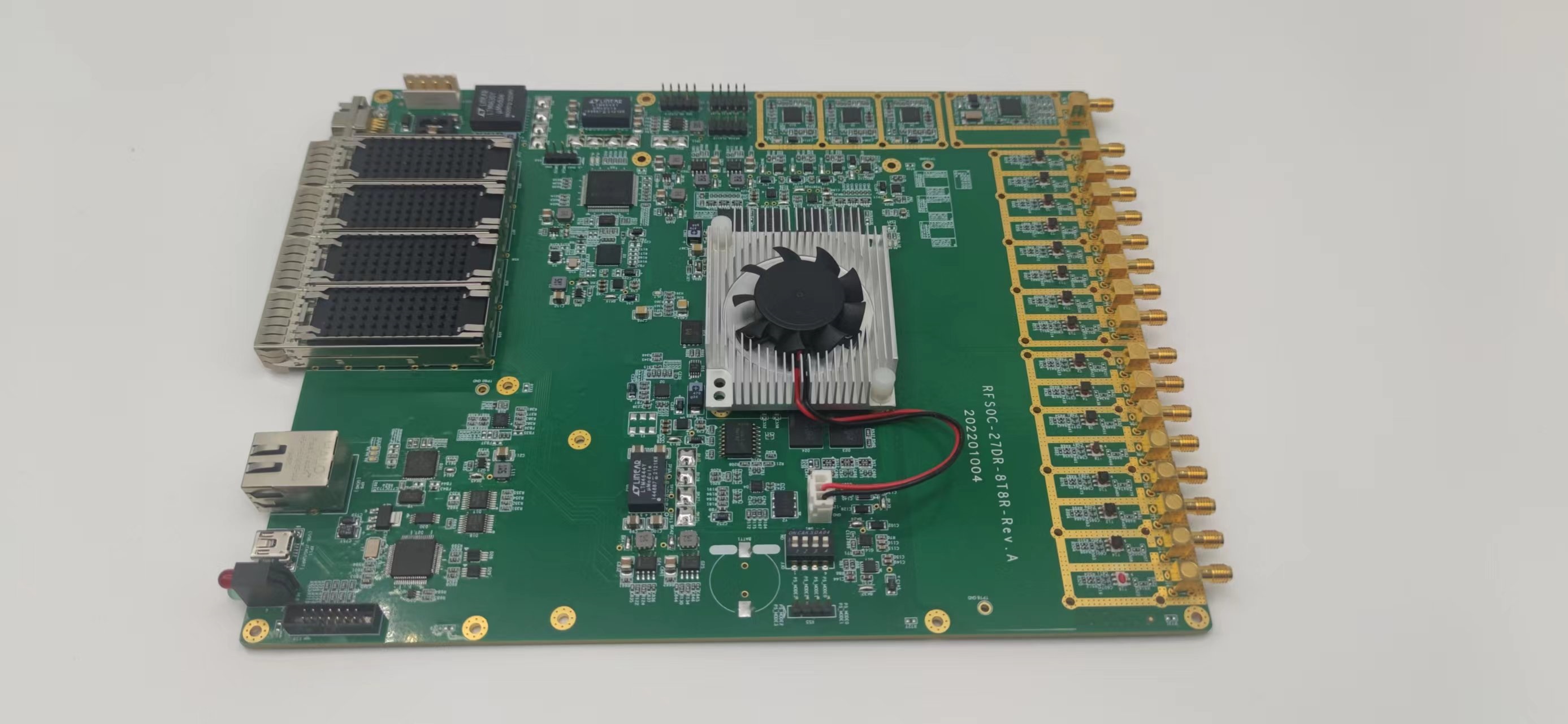

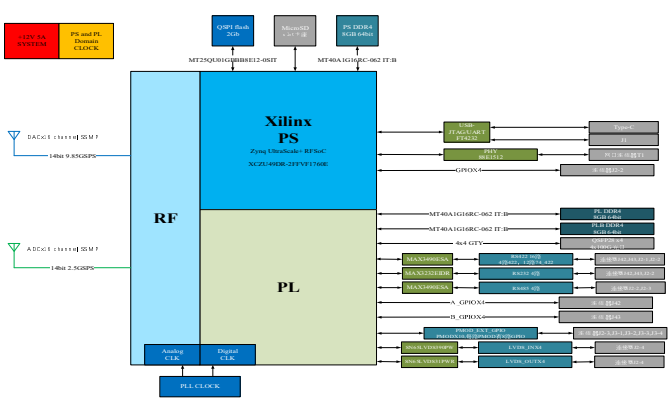

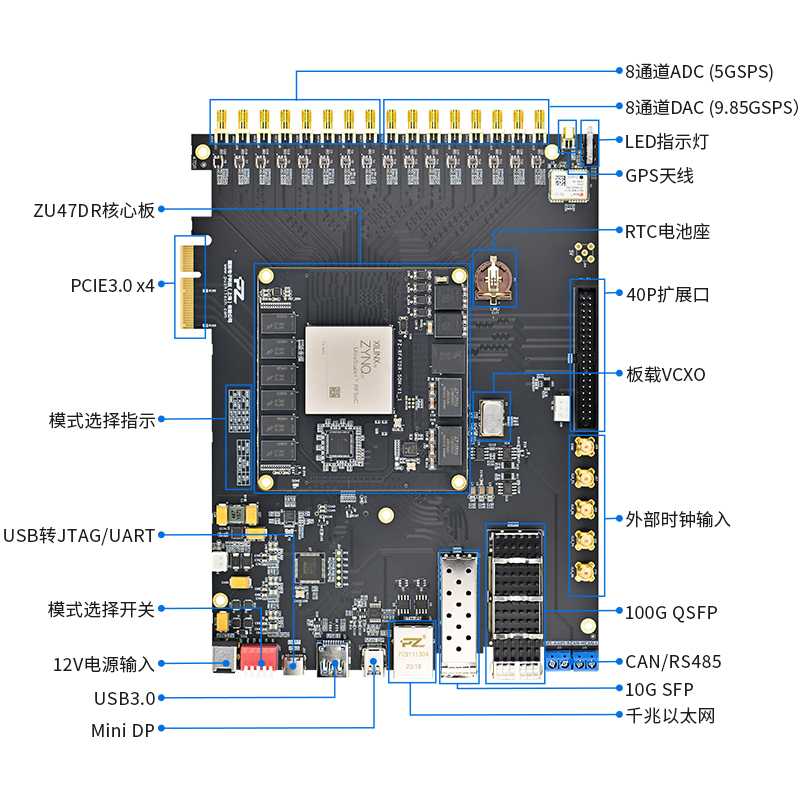

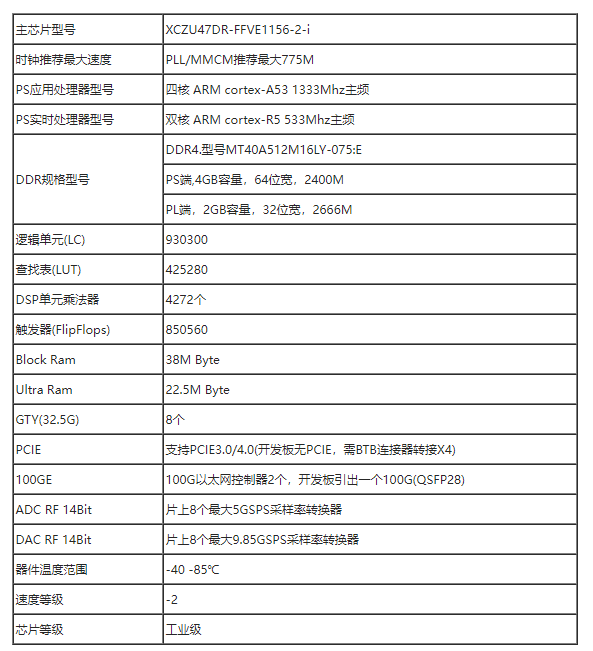

ZXB-27DR-8T8R 數(shù)模混合信號處理卡,采用Xilinx ZYNQ UltraScale+RFSoCZU27DR,可以訪問大型FPGA 門密度,8 路ADC / DAC 端口,可擴展I / O 端口和DDR4 內(nèi)存,適用于各種不同的可編程應(yīng)用,帶有ZU27DR FPGA 的ZXB-RFSOC-2T2R 由 4 路12 位,采樣率4.0GSPS ADC 和 4 路14 位,采樣率6.554 GSPS DAC 端口提供支持。

RF發(fā)送和RF接收端口通過高性能SMA側(cè)插RF連接器對外連接,以ZYNQ UltraScale+ RFSOC作為核心處理系統(tǒng),具有豐富的外設(shè)接口,用于匹配信號處理的外圍控制信號傳輸;

板載40Gbps QSFP 連接器提供光口,10Gbps SFP光口,可與模擬和數(shù)字轉(zhuǎn)換并行地有效處理高速數(shù)據(jù);

PS和PL分別配有內(nèi)存4GBDDR4和2GBDDR4內(nèi)存;支持Micro SD card (support UHS) 、10/100/1000 Ethernet ;

USB JTAG/UART 支持板卡JTAG 加載模式共用UART 輸出、1路RS232接口、1個GPS模塊、GPIO擴展接口,用于功能的擴展。

審核編輯黃宇

-

soc

+關(guān)注

關(guān)注

40文章

4576瀏覽量

229115 -

內(nèi)存

+關(guān)注

關(guān)注

9文章

3209瀏覽量

76357 -

RF

+關(guān)注

關(guān)注

66文章

3201瀏覽量

171795

發(fā)布評論請先 登錄

DR1 評估板 PL 端 FPGA 開發(fā)完全指南:基礎(chǔ)案例與 ADC 采集模塊詳解(一)

DR1M90 評估板 TD-FD 工程與 Linux 多場景應(yīng)用開發(fā)指南

探索 RTKA210030DR0000BU 演示板:高效電源解決方案

安路DR1M90評估板:從基礎(chǔ)外設(shè)到通信模塊測試指南

數(shù)字陣列板卡設(shè)計原理圖:889-基于RFSOC XCZU49DR的 16T16R的軟件無線電硬件

【CPKCOR-RA8D1】+ 6. 使用RA8D1實現(xiàn)UDS診斷之27安全訪問

【VPX361】青翼凌云科技基于3U VPX總線架構(gòu)的XCZU47DR射頻收發(fā)子模塊

睿海光電800G DR8光模塊:以尖端技術(shù)與高效交付重塑數(shù)據(jù)中心互聯(lián)標(biāo)桿

創(chuàng)龍科技DR1M90工業(yè)評估板的關(guān)鍵優(yōu)勢

璞致電子 UltraScale+ RFSoC 架構(gòu)下的軟件無線電旗艦開發(fā)平臺

PZSDR/璞致【PZ-ZU47DR-KFB】——RFSoC 架構(gòu)下的超寬帶軟件無線電開發(fā)平臺標(biāo)桿

高速數(shù)據(jù)采集卡設(shè)計:887-基于 RFSoC 47DR的8T8R 100Gbps 軟件無線電光纖前端卡

1.6T OSFP-XD DR8 光模塊的介紹

NW2-05D05DR3 NW2-05D05DR3

NW1-24D15DR3 NW1-24D15DR3

XilinxZYNQUltraScale+RFSoCZU27DR開源RFSOC算法-ZXB-27DR-8T8R驗證評估板

XilinxZYNQUltraScale+RFSoCZU27DR開源RFSOC算法-ZXB-27DR-8T8R驗證評估板

評論