高性能的時鐘器件是高帶寬、高速率、高算力、大模型的基礎。核芯互聯(lián)近日推出面向下一代數(shù)據(jù)中心應用的超低抖動全新20路LP-HCSL差分時鐘緩沖器CLB2000,其業(yè)界領先的附加抖動性能遠超PCIe Gen 5和PCIe Gen 6的標準。

1簡介

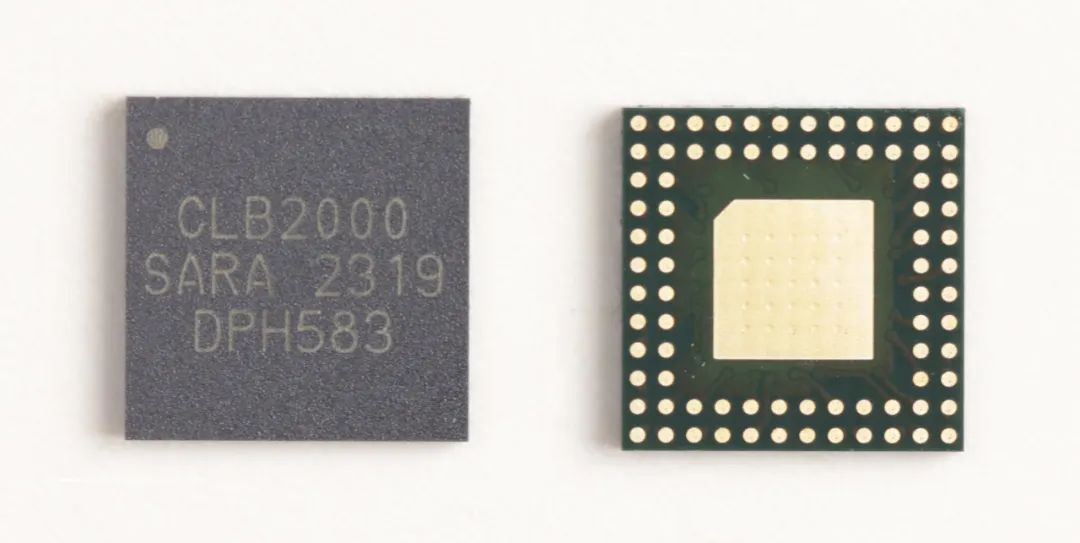

高性能的時鐘器件是高帶寬、高速率、高算力、大模型的基礎。核芯互聯(lián)近日推出面向下一代數(shù)據(jù)中心應用的超低抖動全新20路LP-HCSL差分時鐘緩沖器CLB2000,其業(yè)界領先的附加抖動性能遠超PCIe Gen 5和PCIe Gen 6的標準。

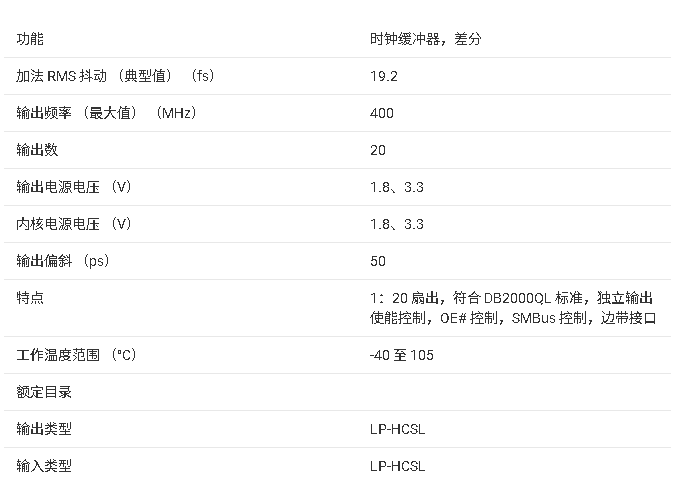

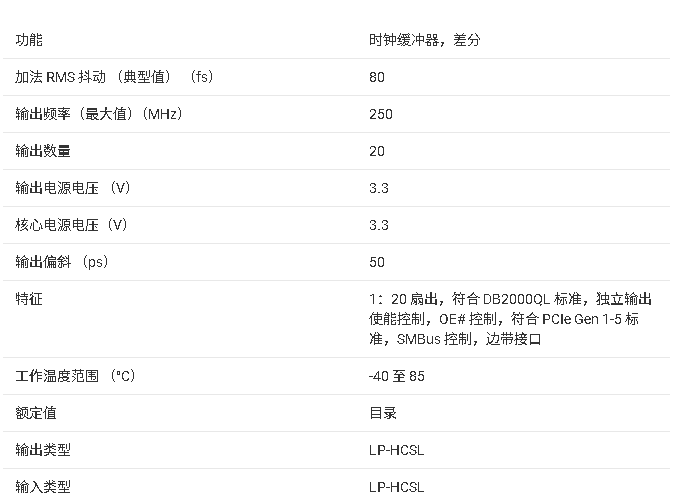

新推出的CLB2000符合最新的DB2000Q設計規(guī)范,可適用于下一代服務器、數(shù)據(jù)中心、存儲設備及其他PCIe應用,且同時滿足PCIe Gen1/2/3/4/5/6的規(guī)格。

2典型性能

輸出時鐘偏斜:<50ps;

輸出延遲:<3ns;

附加抖動DB2000QL:< 8fs;

附加抖動PCIe Gen 4:< 10fs;

附加抖動PCIe Gen 5:< 5fs;

附加抖動PCIe Gen 6:< 3fs;

符合英特爾DB2000QL規(guī)范;

3.3V電源供電;

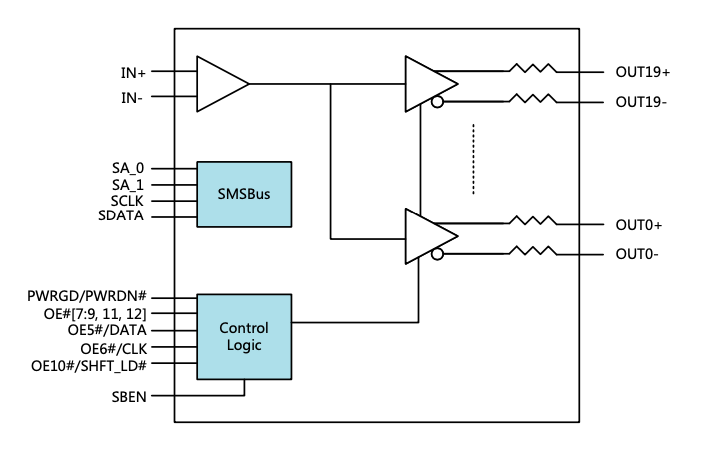

20路LP-HCSL輸出;

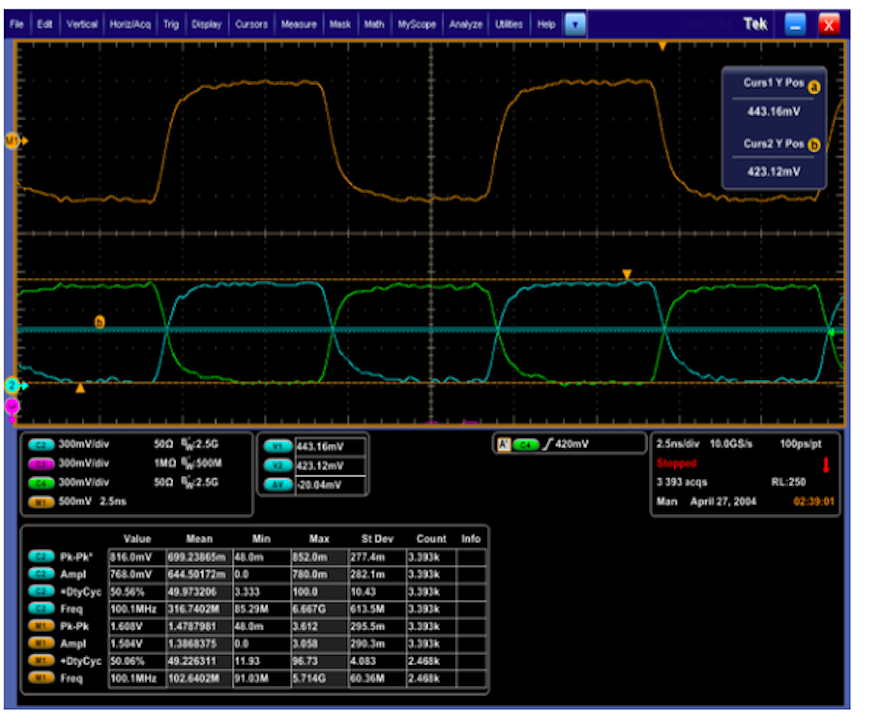

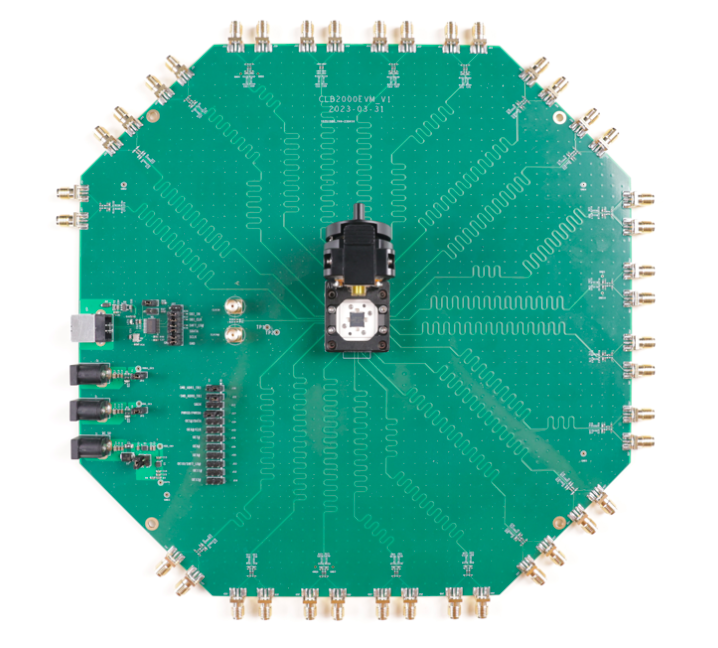

100M輸出波形

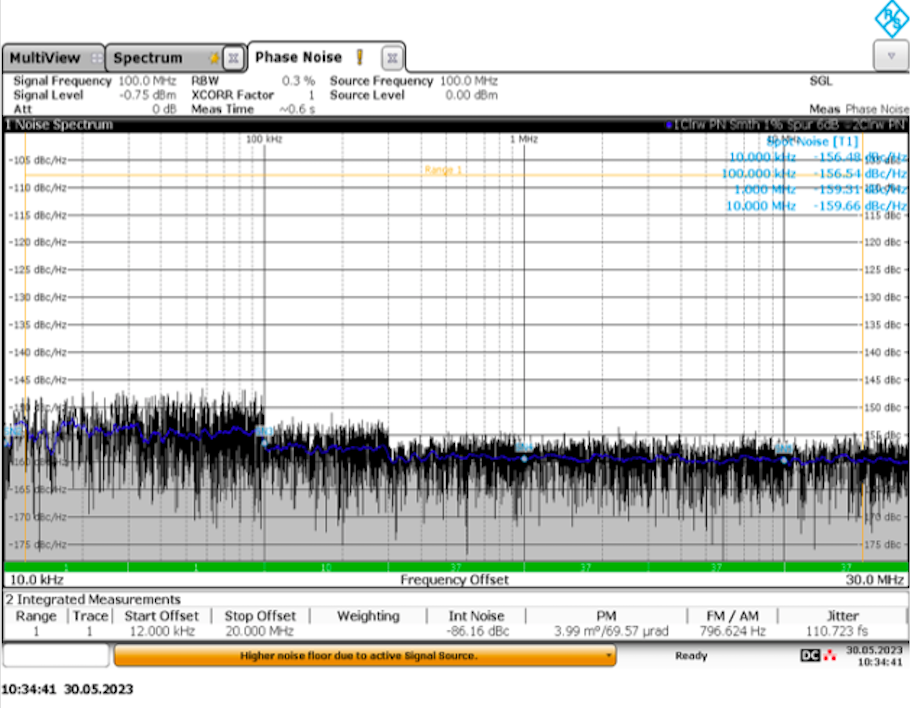

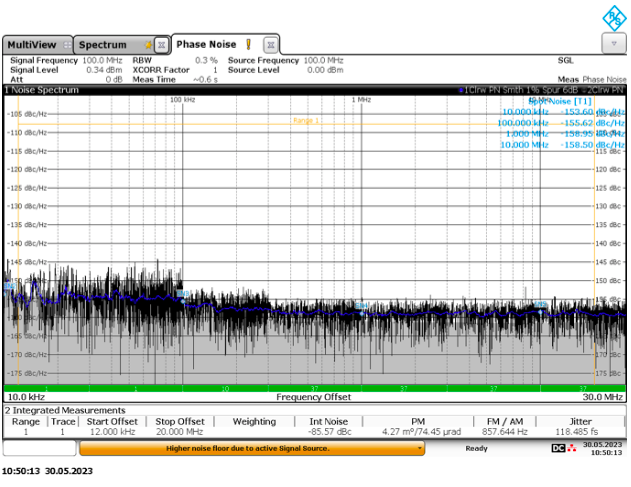

100M輸入Jitter

100M輸出Jitter

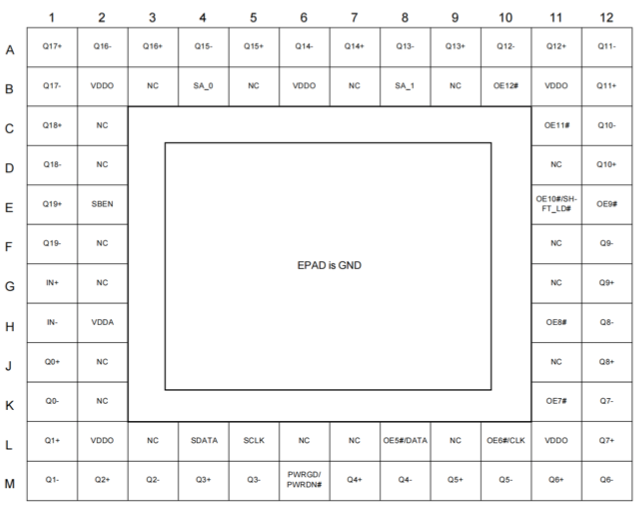

3管腳定義

4送樣

CLB2000已經開放送樣,請廣大客戶聯(lián)系對口銷售。

-

緩沖器

+關注

關注

6文章

2234瀏覽量

48966 -

時鐘器件

+關注

關注

0文章

16瀏覽量

8226 -

大模型

+關注

關注

2文章

3712瀏覽量

5231

發(fā)布評論請先 登錄

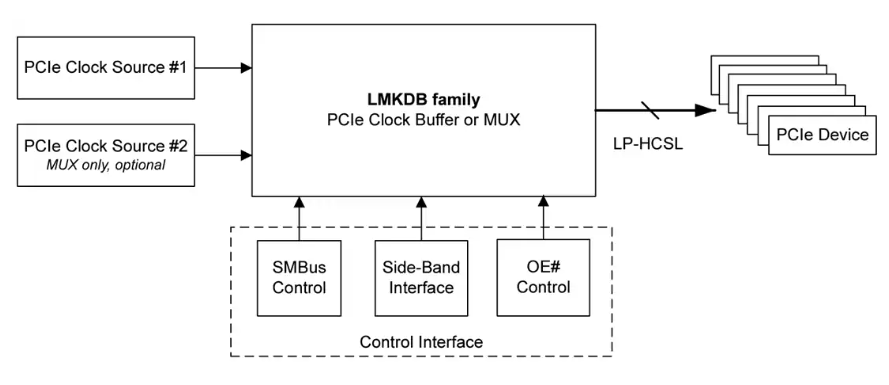

瑞薩電子推出符合PCIe Gen6標準的時鐘緩沖器和多路復用器

Microchip推出全新時鐘緩沖器 遠超PCIe?第五代(Gen 5)防抖標準

瑞薩電子推符合PCIe Gen6時鐘緩沖器和多路復用器

核芯互聯(lián)推出全新20路LP-HCSL差分時鐘緩沖器CLB2000

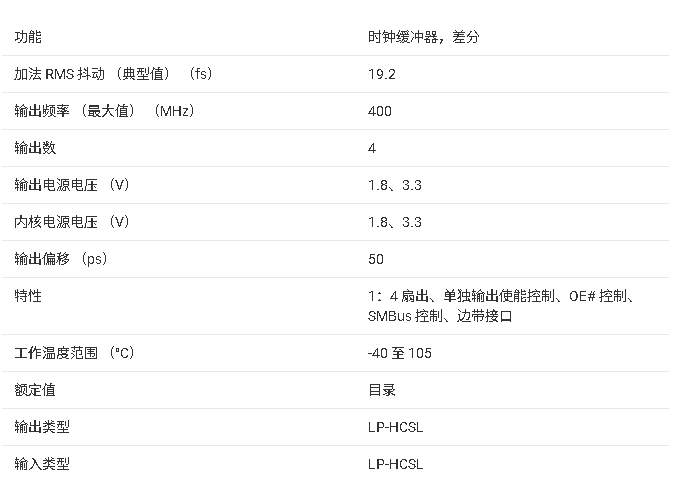

符合CDCDB2000 DB2000QL標準的20輸出時鐘緩沖器,適用于PCIe第1代到第5代數(shù)據(jù)表

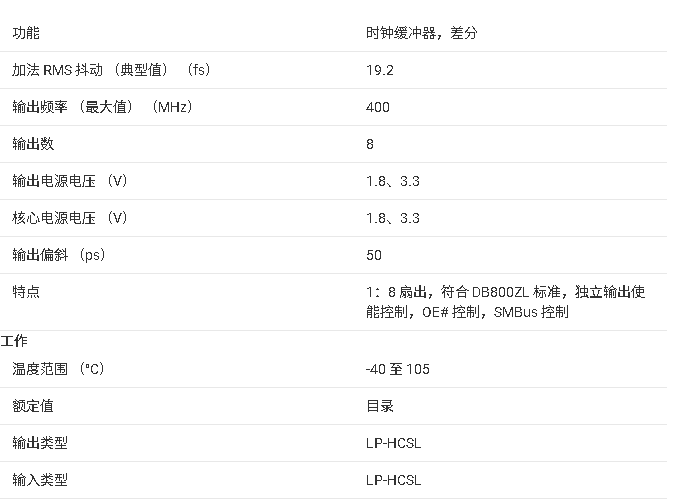

CDCDB800/803超低附加抖動、8路輸出PCIe Gen1至Gen5時鐘緩沖器

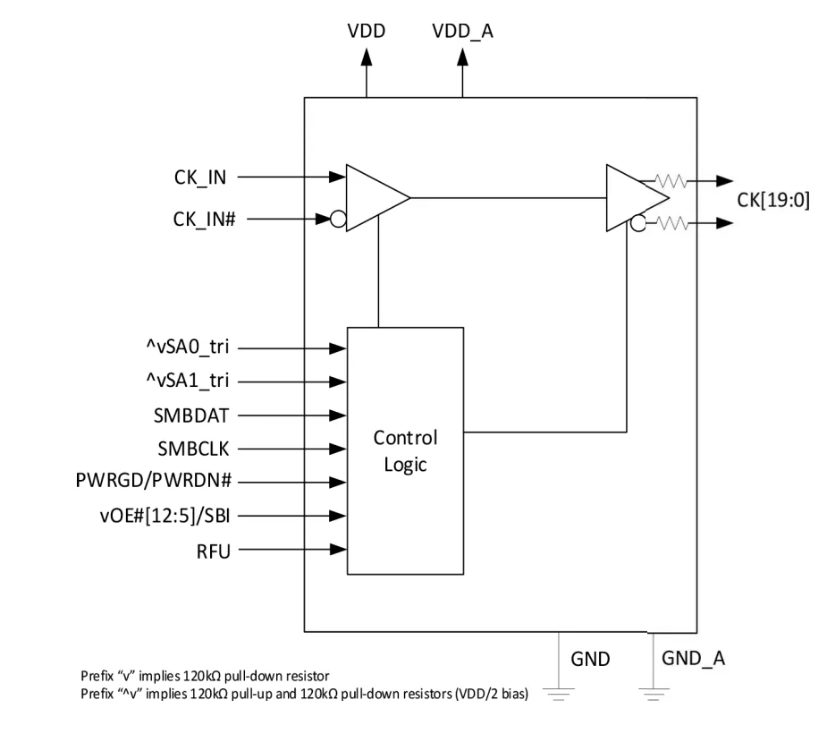

LMKDB1104 用于 PCIe Gen 1 至 Gen 7 的 4 輸出 LP-HCSL 時鐘緩沖器技術手冊

LMKDB1108 用于 PCIe Gen 1 至 Gen 7 的 8 輸出 LP-HCSL 時鐘緩沖器技術手冊

ZL40294B:面向PCIe Gen6的超低附加抖動時鐘扇出緩沖器

核芯互聯(lián)推出符合DB2000QL及PCIe Gen5和Gen 6標準的低抖動時鐘緩沖器CLB2000

核芯互聯(lián)推出符合DB2000QL及PCIe Gen5和Gen 6標準的低抖動時鐘緩沖器CLB2000

評論