在BSIM3的基礎(chǔ)上,UC Berkley的BSIM小組緊接著又推出了BSIM4模型。

BSIM4模型是在BSIM3模型的基礎(chǔ)上發(fā)展而來(lái)的,主要針對(duì)深亞微米到納米的工藝進(jìn)行了改進(jìn)和擴(kuò)展。與BSIM3模型相比,BSIM4模型有以下幾個(gè)區(qū)別:

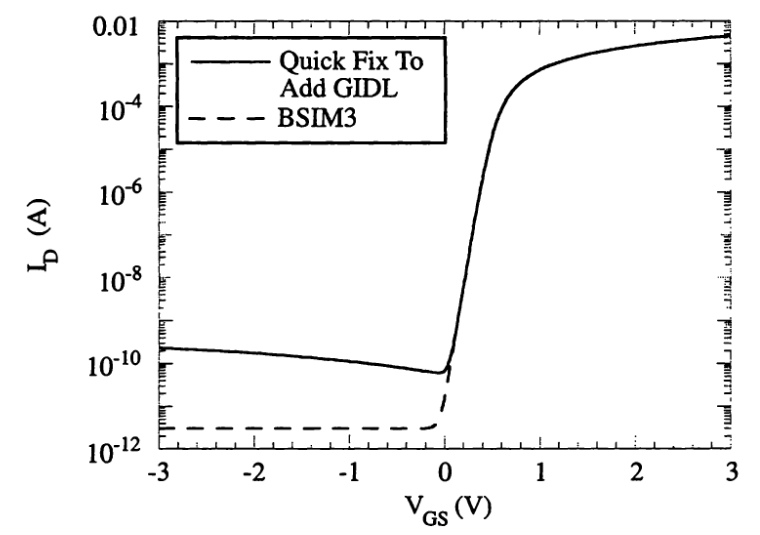

BSIM4模型增加了對(duì)多晶硅柵極極化效應(yīng)、柵極漏電流、柵極隧穿電流、柵極直接隧穿電流等現(xiàn)象的建模。通過(guò)對(duì)GIDL現(xiàn)象建模,使得在負(fù)柵壓下仍可準(zhǔn)確預(yù)測(cè)體電流。工藝發(fā)展到90nm節(jié)點(diǎn)后,由于柵氧層過(guò)薄而引起的柵極隧穿電流不再可忽略,BSIM4建立了詳細(xì)的隧穿模型來(lái)描述柵極電流。

圖:BSIM4中增加了對(duì)GIDL現(xiàn)象的模型(實(shí)線),而BSIM3模型則不能描述(虛線)

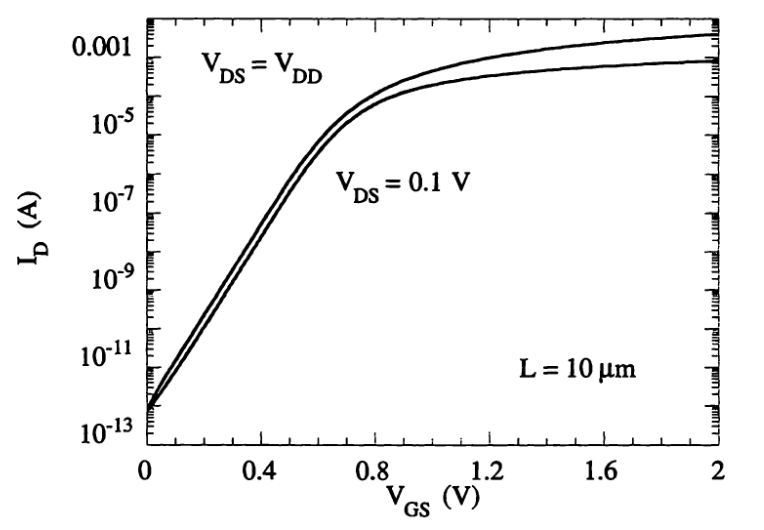

BSIM4模型改進(jìn)了對(duì)短溝道效應(yīng)、窄溝道效應(yīng)、溝道長(zhǎng)度調(diào)制效應(yīng)、溝道電荷分布效應(yīng)等現(xiàn)象的建模。BSIM4增添了pocket/retrograde新工藝對(duì)閾值電壓的影響,并改進(jìn)短溝系數(shù)以消除閾值電壓roll—up現(xiàn)象。

圖:Pocket Implant引入后仿真的IdVg曲線

BSIM4模型引入了對(duì)射頻電路設(shè)計(jì)相關(guān)的參數(shù)和效應(yīng)的建模,如輸出導(dǎo)納、輸出電阻、輸出電容等。BSIM4改進(jìn)了器件的輸出電阻模型、NQS模型和1/f噪聲模型,并增加了柵電阻、熱噪聲及噪聲分配方案和襯底電阻網(wǎng)絡(luò)的描述。

BSIM4模型提供了更多的可選參數(shù)和功能,如溫度依賴性、工藝變異性、器件匹配性、噪聲分析等。BSIM4還分析了版圖設(shè)計(jì)(多finger布圖、串并聯(lián)等)對(duì)器件寄生參數(shù)的影響。

總之BSIM4是對(duì)BSIM3的全面提升,一般認(rèn)為BSM3主要適用于微米、亞微米器件,而BSIM4主要適用于亞微米到納米級(jí)平面器件(130nm-20nm)。繼BSIM3之后,BSIM4也被Compact Model Council采納為標(biāo)準(zhǔn)模型。

審核編輯:劉清

-

射頻電路

+關(guān)注

關(guān)注

36文章

455瀏覽量

44784 -

輸出電容

+關(guān)注

關(guān)注

0文章

121瀏覽量

8892 -

閾值電壓

+關(guān)注

關(guān)注

0文章

98瀏覽量

52588

發(fā)布評(píng)論請(qǐng)先 登錄

如何用DC掃描提取BSIM3電容?

如何在ADS中添加晶體管的spice模型

概倫電子通用并行電路仿真器NanoSpice?介紹

概倫電子千兆級(jí)電路仿真器NanoSpiceGiga?介紹

業(yè)界領(lǐng)先的半導(dǎo)體器件SPICE建模平臺(tái)介紹

PDK 驗(yàn)證軟件PQLab的優(yōu)勢(shì)和技術(shù)指標(biāo)

探究Linux電源管理模型

探究BUCK/BOOST開(kāi)關(guān)電路

EDA技術(shù)探索之BSIM3模型

BSIM4模型與BSIM3模型的區(qū)別

在SPICE模擬器中應(yīng)該調(diào)諧優(yōu)化哪些模型參數(shù)?需要全部調(diào)優(yōu)嗎?

一文詳解BSIM-SOI模型

探究BSIM4模型

探究BSIM4模型

評(píng)論