點擊上方藍字關注我們

芯片設計流程概述

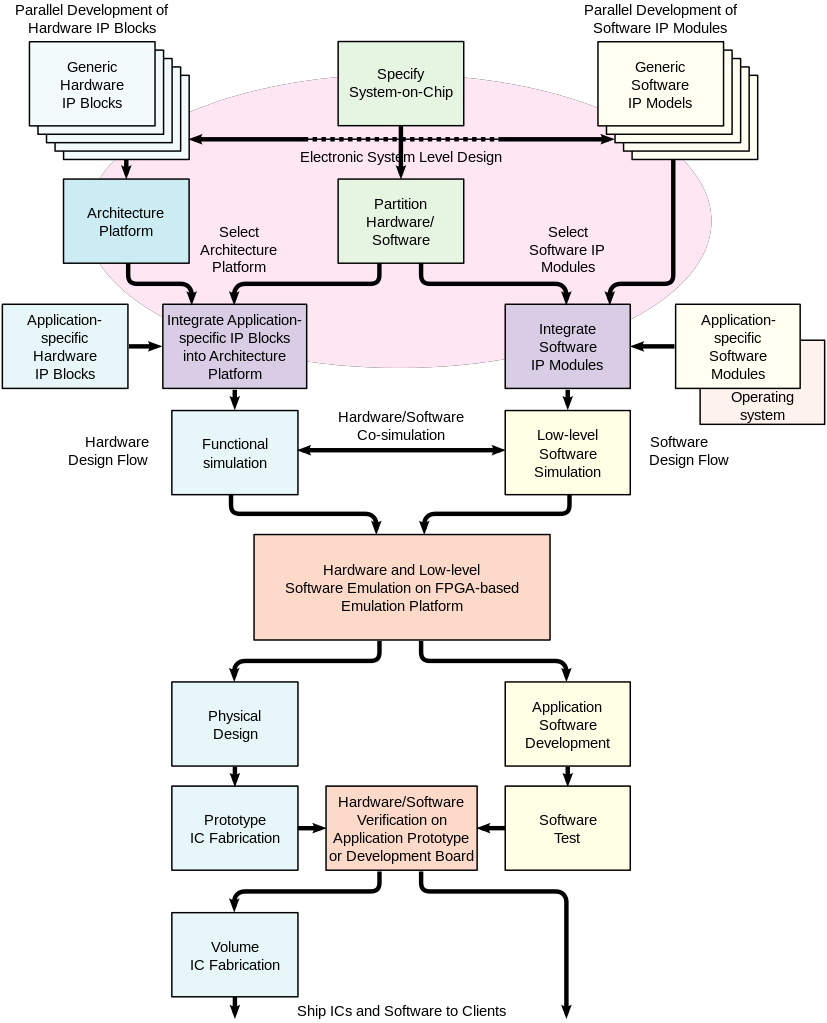

芯片設計分為前端設計和后端設計,前端設計(也稱邏輯設計)和后端設計(也稱物理設計)并沒有統一嚴格的界限,涉及到與工藝有關的設計就是后端設計。

1. 規格制定

芯片規格,也就像功能列表一樣,是客戶向芯片設計公司(稱為Fabless,無晶圓設計公司)提出的設計要求,包括芯片需要達到的具體功能和性能方面的要求。

2. 詳細設計

Fabless根據客戶提出的規格要求,拿出設計解決方案和具體實現架構,劃分模塊功能。

3. HDL編碼

使用硬件描述語言(VHDL,Verilog HDL,業界公司一般都是使用后者)將模塊功能以代碼來描述實現,也就是將實際的硬件電路功能通過HDL語言描述出來,形成RTL(寄存器傳輸級)代碼。

4. 仿真驗證

仿真驗證就是檢驗編碼設計的正確性,檢驗的標準就是第一步制定的規格。看設計是否精確地滿足了規格中的所有要求。規格是設計正確與否的黃金標準,一切違反,不符合規格要求的,就需要重新修改設計和編碼。設計和仿真驗證是反復迭代的過程,直到驗證結果顯示完全符合規格標準。

仿真驗證工具Synopsys的VCS,還有Cadence的NC-Verilog。

5. 邏輯綜合――Design Compiler

仿真驗證通過,進行邏輯綜合。邏輯綜合的結果就是把設計實現的HDL代碼翻譯成門級網表netlist。綜合需要設定約束條件,就是你希望綜合出來的電路在面積,時序等目標參數上達到的標準。邏輯綜合需要基于特定的綜合庫,不同的庫中,門電路基本標準單元(standard cell)的面積,時序參數是不一樣的。所以,選用的綜合庫不一樣,綜合出來的電路在時序,面積上是有差異的。一般來說,綜合完成后需要再次做仿真驗證(這個也稱為后仿真,之前的稱為前仿真)。

邏輯綜合工具Synopsys的Design Compiler。

6. STA

Static Timing Analysis(STA),靜態時序分析,這也屬于驗證范疇,它主要是在時序上對電路進行驗證,檢查電路是否存在建立時間(setup time)和保持時間(hold time)的違例(violation)。這個是數字電路基礎知識,一個寄存器出現這兩個時序違例時,是沒有辦法正確采樣數據和輸出數據的,所以以寄存器為基礎的數字芯片功能肯定會出現問題。

STA工具有Synopsys的Prime Time。

7. 形式驗證

這也是驗證范疇,它是從功能上(STA是時序上)對綜合后的網表進行驗證。常用的就是等價性檢查方法,以功能驗證后的HDL設計為參考,對比綜合后的網表功能,他們是否在功能上存在等價性。這樣做是為了保證在邏輯綜合過程中沒有改變原先HDL描述的電路功能。

形式驗證工具有Synopsys的Formality。

前端設計的流程暫時寫到這里。從設計程度上來講,前端設計的結果就是得到了芯片的門級網表電路。

Backend design flow :

1. DFT

Design For Test,可測性設計。芯片內部往往都自帶測試電路,DFT的目的就是在設計的時候就考慮將來的測試。DFT的常見方法就是,在設計中插入掃描鏈,將非掃描單元(如寄存器)變為掃描單元。關于DFT,有些書上有詳細介紹,對照圖片就好理解一點。

DFT工具Synopsys的DFT Compiler

2. 布局規劃(FloorPlan)

布局規劃就是放置芯片的宏單元模塊,在總體上確定各種功能電路的擺放位置,如IP模塊,RAM,I/O引腳等等。布局規劃能直接影響芯片最終的面積。

工具為Synopsys的Astro

3. CTS

Clock Tree Synthesis,時鐘樹綜合,簡單點說就是時鐘的布線。由于時鐘信號在數字芯片的全局指揮作用,它的分布應該是對稱式的連到各個寄存器單元,從而使時鐘從同一個時鐘源到達各個寄存器時,時鐘延遲差異最小。這也是為什么時鐘信號需要單獨布線的原因。

CTS工具,Synopsys的Physical Compiler

4. 布線(Place & Route)

這里的布線就是普通信號布線了,包括各種標準單元(基本邏輯門電路)之間的走線。比如我們平常聽到的0.13um工藝,或者說90nm工藝,實際上就是這里金屬布線可以達到的最小寬度,從微觀上看就是MOS管的溝道長度。

工具Synopsys的Astro

5. 寄生參數提取

由于導線本身存在的電阻,相鄰導線之間的互感,耦合電容在芯片內部會產生信號噪聲,串擾和反射。這些效應會產生信號完整性問題,導致信號電壓波動和變化,如果嚴重就會導致信號失真錯誤。提取寄生參數進行再次的分析驗證,分析信號完整性問題是非常重要的。

工具Synopsys的Star-RCXT

6. 版圖物理驗證

對完成布線的物理版圖進行功能和時序上的驗證,驗證項目很多,如LVS(Layout Vs Schematic)驗證,簡單說,就是版圖與邏輯綜合后的門級電路圖的對比驗證;DRC(Design Rule Checking):設計規則檢查,檢查連線間距,連線寬度等是否滿足工藝要求, ERC(Electrical Rule Checking):電氣規則檢查,檢查短路和開路等電氣 規則違例;等等。

工具為Synopsys的Hercules

實際的后端流程還包括電路功耗分析,以及隨著制造工藝不斷進步產生的DFM(可制造性設計)問題,在此不說了。

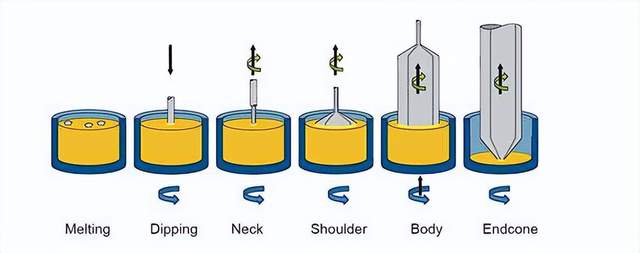

物理版圖驗證完成也就是整個芯片設計階段完成,下面的就是芯片制造了。物理版圖以GDS II的文件格式交給芯片代工廠(稱為Foundry)在晶圓硅片上做出實際的電路,再進行封裝和測試,就得到了我們實際看見的芯片。

往期推薦

往期推薦

掃碼二維碼

獲取更多精彩

FPGA設計論壇

原文標題:芯片設計流程概述

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636374

原文標題:芯片設計流程概述

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

芯片ATE測試詳解:揭秘芯片測試機臺的工作流程

ATE(自動測試設備)是芯片出廠前的關鍵“守門人”,負責篩選合格品。其工作流程分為測試程序生成載入、參數測量與功能測試(含直流、交流參數及功能測試)、分類分檔與數據分析三階段,形成品質閉環。為平衡

航天級抗輻照電源芯片研發全流程:從設計到上市的10大核心環節

電源管理芯片是電子設備的“能量心臟”,而國科安芯ASP3605作為一款 航天級抗輻照DC/DC Buck電源芯片 (其裸die常作為核心模塊用于航天集成電源方案),其研發流程需額外攻克極端太空環境下

使用6e00系列的芯片,clc計算流程求解?

大家好,請教個問題,我在使用6e00系列的芯片,調試時遇到了疑惑:clc單元,設置所有的系數為0,pwm_period為0x13870, 反饋值也是0,期望值也是0,此時應該輸出0才對,但是此時

發表于 11-09 23:06

ADI Power Studio工作流程與工具概述

ADI Power Studio是一套面向應用工程師及高級電源設計用戶的綜合性產品系列,能夠有效簡化整個電源系統的設計流程,提供從初步概念到測量和評估的全程支持。Power Studio提供統一

芯片開封(Decap)的流程

在集成電路分析領域,芯片開封(Decapsulation,簡稱Decap)是一項至關重要的技術環節。無論是進行失效分析還是反向工程研究,芯片開封都是打開微觀世界大門的第一把鑰匙。這項技術旨在精確移除

霍爾芯片鹽霧試驗測試流程

霍爾芯片鹽霧試驗的測試流程涵蓋預處理、試驗箱配置、樣品放置、參數控制、周期測試、結果評估及報告生成等關鍵環節,具體流程如下: 1、樣品準備與預處理: 清潔:使用乙醇或氧化鎂溶液等非研磨性清潔劑徹底

電源芯片一次篩選:復雜流程下的高要求與高效應對

一次篩選:芯片可靠性的“第一道防線”在集成電路從設計到量產的全流程中,一次篩選是保障產品質量的核心環節。它位于封裝測試階段前端,通過多維度的嚴格測試,如電性能測試、環境應力篩選(如高低溫、濕度測試

Thread標準認證概述

本篇知識庫文章概述了開發人員如何將其Thread物聯網設備進行Thread Group認證所需的步驟,并重點介紹使用Silicon Labs(芯科科技)的EFR32無線射頻器件的相關流程。

芯知識|廣州唯創電子語音芯片開發全流程解析:從選型到量產的實踐指南

一、語音芯片開發的核心邏輯與價值定位在智能化設備井噴式發展的背景下,語音交互已成為人機界面的重要入口。廣州唯創電子作為國內領先的語音芯片方案商,其開發流程設計始終圍繞功能適配性、開發效率和量產可靠性

從芯片制造流程,探尋國產芯片突圍之路

。從沙子到芯片,需歷經數百道工序。下面,讓我們深入了解芯片的制造流程。 一、從沙子到硅片(原材料階段) 沙子由氧和硅組成,主要成分是二氧化硅。芯片制造的首要步驟就是將沙子中的二氧化硅還

基于ISO 26262的汽車芯片認證流程解讀

通過一系列嚴格的車規認證才能應用于汽車制造。ISO 26262標準是汽車功能安全領域的權威標準,它為汽車芯片的設計、開發和認證提供了全面的指導。本文將詳細介紹基于ISO 26262標準的汽車芯片認證流程,并以國科安芯的AS32A

深入解析硅基光子芯片制造流程,揭秘科技奇跡!

特性,在高速通信、高性能計算、數據中心等領域展現出巨大的應用潛力。本文將深入探討硅基光子芯片制造技術,從其發展背景、技術原理、制造流程到未來展望,全方位解析這一前沿

芯片設計流程概述

芯片設計流程概述

評論