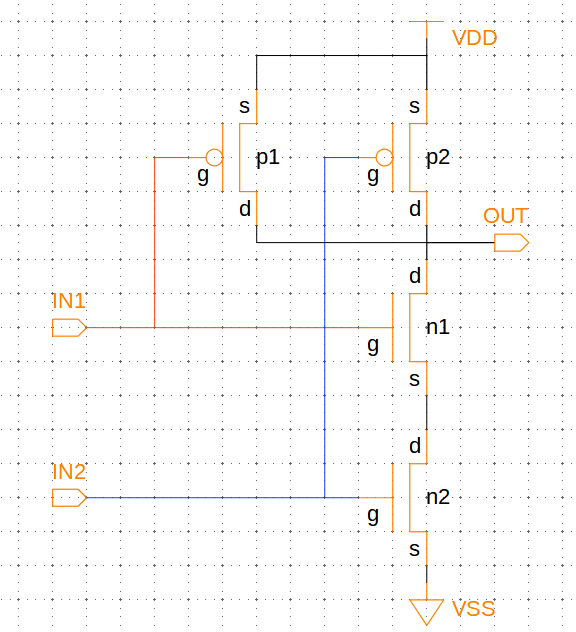

小編設計的集成MIPI DPHY的MCU版圖如下,今天梳理下DPHY的集成驗證。

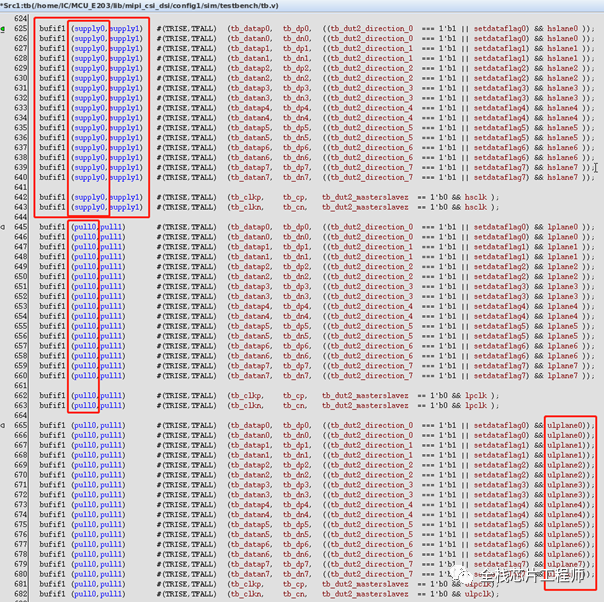

線網驅動強度(drive strength):

用于表示0的強度:highz0、supply0、strong0、pull0、weak0。

用于表示1的強度:highz1、supply1、strong1、pull1、weak1。

supply,strong,pull,weak強度依次下降,注意,supply0和supply1用于模型電源,就是只能提供0和1值的線網,通常只在Vendor提供的標準單元庫中使用,平時不用。

舉個例子MIPI DPHY的testbench的DP、DN接口在HS模式、LP模式/ULPS模式下的驅動力如下,仿真模式下,為了讓HS的驅動力最強,我們用supply來驅動bufif1,然后LP模式用pull來驅動bufif1。

我們以dphy_ipi_tests測試為例,具體仿真驅動函數如下:

initialize_dut函數對DUT初始化:

phy_testclr = 1'b1;

phy_testdin = 8'd0;

phy_testen = 1'd0;

phy_testclk = 1'd0;

presetn= 1'd0;

#(10)

presetn= 1'd1;

#(10)

update_phy_test_ctrl1;

update_phy_test_ctrl0;

給下面寄存器賦初始值(無效值):

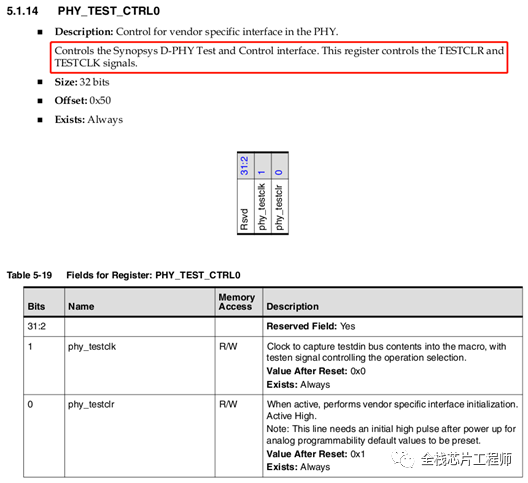

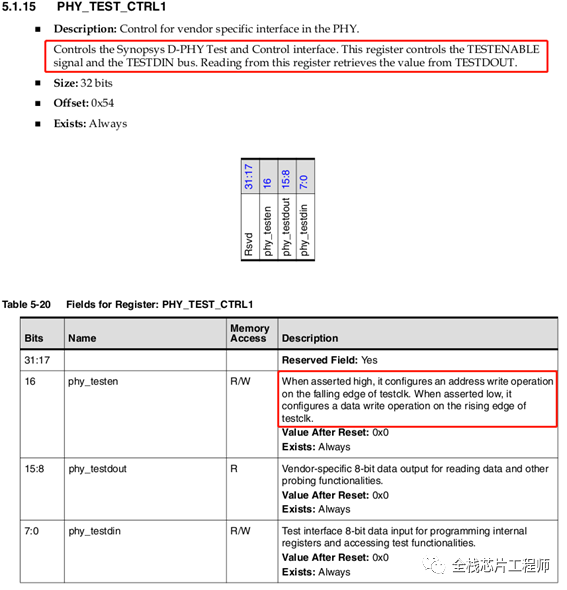

task update_phy_test_ctrl0; apbWrite(`CSI2_HOST_PHY_TEST_CTRL0_OS, {30'd0, phy_testclk, phy_testclr}); endtask task update_phy_test_ctrl1; apbWrite(`CSI2_HOST_PHY_TEST_CTRL1_OS,{15'd0, phy_testen, 8'd0, phy_testdin}); endtask

特別注意phy_test_ctrl1寄存器是用于DPHY的配置:

//CSI2 Controller Programming apbWrite(`CSI2_HOST_PHY_SHUTDOWNZ_OS, 32'hFFFF_FFFF); // 取消phy shutdown apbWrite(`CSI2_HOST_DPHY_RSTZ_OS , 32'hFFFF_FFFF); // 取消phy reset復位 apbWrite(`CSI2_HOST_CSI2_RESETN_OS , 32'hFFFF_FFFF); // 取消csi2 reset復位

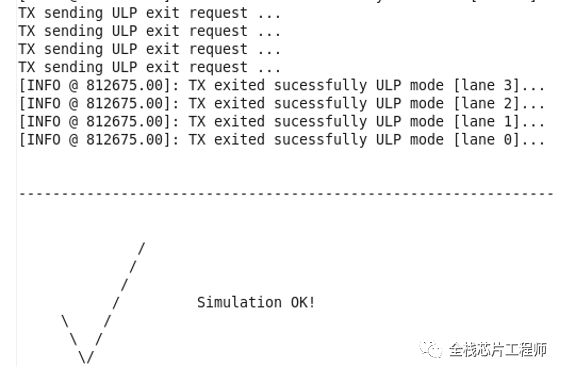

配置DPHY的帶寬為1GHz,配置接口時序如下:

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5608瀏覽量

129968 -

MIPI

+關注

關注

11文章

355瀏覽量

50879 -

DUT

+關注

關注

0文章

194瀏覽量

13450 -

MCU芯片

+關注

關注

3文章

260瀏覽量

12888

原文標題:MCU的DPHY+CSI2的驅動驗證(一)

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

梳理一下FreeRTOS任務管理單元實現思路

梳理一下FreeRTOS內核代碼規范

分析一下哪些人最能成大事

SN75DPHY440SS MIPI? CSI-2/DSI DPHY 重定時器

SN65DPHY440SS SN65DPHY440SS CSI-2/DSI DPHY 重定時器

梳理一下DPHY的集成驗證

梳理一下DPHY的集成驗證

評論