作者:泛林集團(tuán)半導(dǎo)體工藝與整合工程師 Sumant Sarkar

使用Coventor SEMulator3D?創(chuàng)建可以預(yù)測寄生電容的機(jī)器學(xué)習(xí)模型

減少柵極金屬和晶體管的源極/漏極接觸之間的寄生電容可以減少器件的開關(guān)延遲。減少寄生電容的方法之一是設(shè)法降低柵極和源極/漏極之間材料層的有效介電常數(shù),這可以通過在該位置的介電材料中引入空氣間隙來實(shí)現(xiàn)。這種類型的方式過去已經(jīng)用于后道工序 (BEOL) 中,以減少金屬互連之間的電容 [1-4]。本文中,我們將專注于前道工序 (FEOL),并演示在柵極和源極/漏極之間引入空氣間隙的SEMulator3D?模型[5]。SEMulator3D?是一個(gè)虛擬的制造軟件平臺,可以在設(shè)定的半導(dǎo)體工藝流程內(nèi)模擬工藝變量。利用SEMulator3D?設(shè)備中的實(shí)驗(yàn)設(shè)計(jì) (DoE) 功能,我們展示了寄生電容與刻蝕深度和其他用于制作空氣間隙的刻蝕工藝參數(shù)的相關(guān)性,以及它與空氣間隙大小和體積的相關(guān)性。

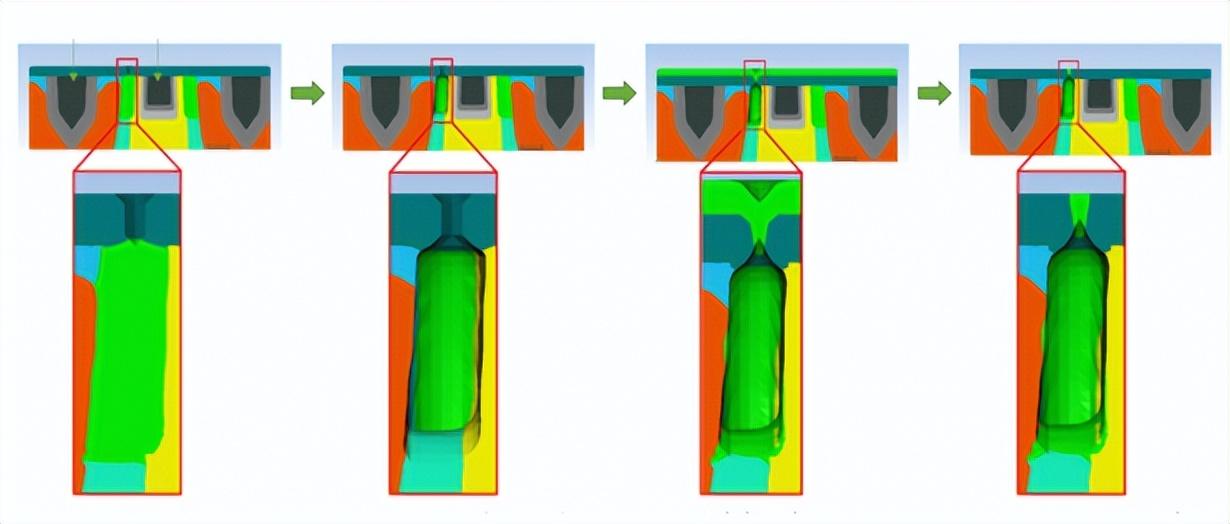

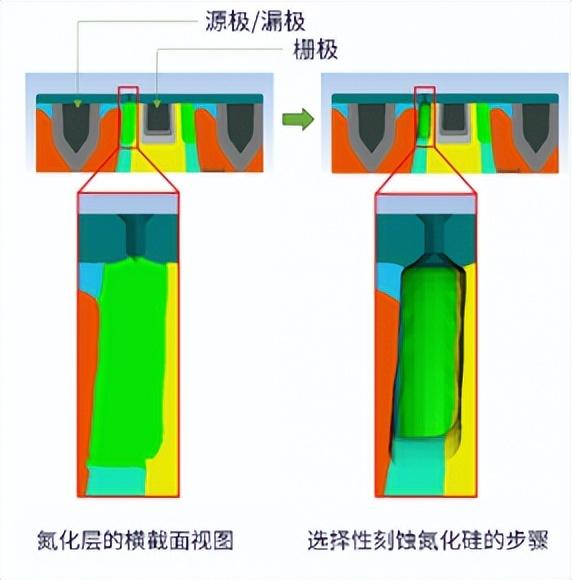

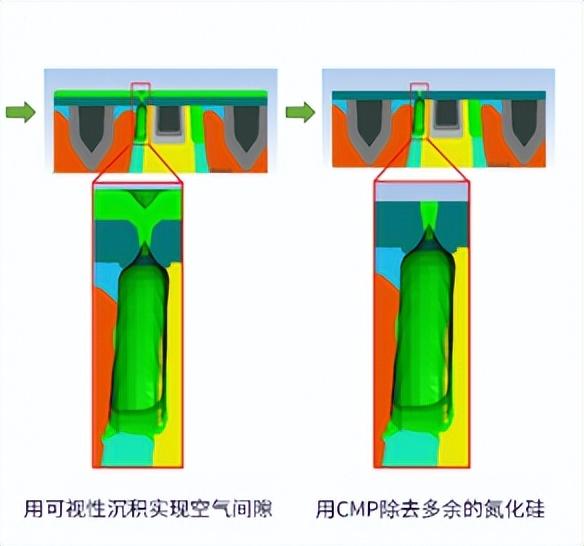

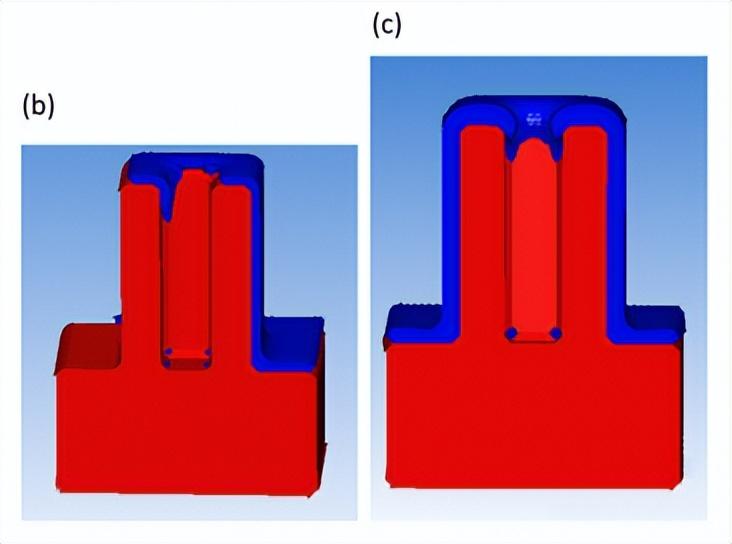

圖1顯示了SEMulator3D? FinFET模型的橫截面。為了在FinFET的柵極和源極/漏極之間引入空氣間隙,我們進(jìn)行了高選擇比的氮化硅刻蝕工藝,然后進(jìn)行經(jīng)過優(yōu)化的氮化硅沉積工藝,以封閉結(jié)構(gòu)并產(chǎn)生空氣間隙結(jié)構(gòu)。接著用氮化硅CMP(化學(xué)機(jī)械拋光)工藝對表面進(jìn)行平坦化處理。

圖1:在FinFET模型中引入空氣間隙的SEMulator3D工藝流程。可視性沉積的步驟通過在頂端夾止的方式產(chǎn)生空氣間隙,然后進(jìn)行CMP步驟除去多余的氮化硅。空氣間隙減少了柵極和源極/漏極之間的寄生電容。空氣間隙的大小可以通過改變刻蝕反應(yīng)物的刻蝕深度、晶圓傾角和等離子體入射角度分布來控制。

使用SEMulator3D的虛擬測量功能測量以下指標(biāo):

1 柵極金屬和源極/漏極之間的寄生電容

2 空氣間隙的體積

3 空氣間隙z軸的最小值,代表空氣間隙的垂直尺寸

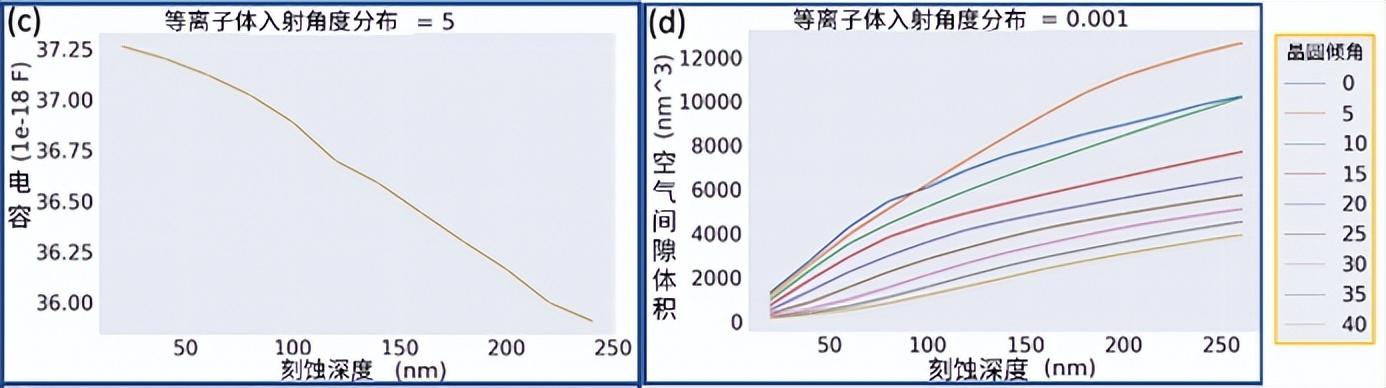

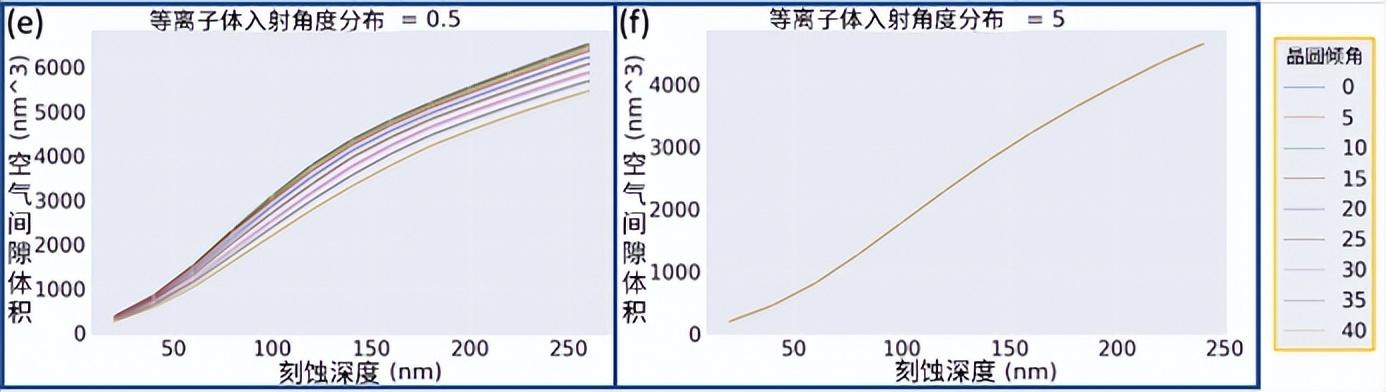

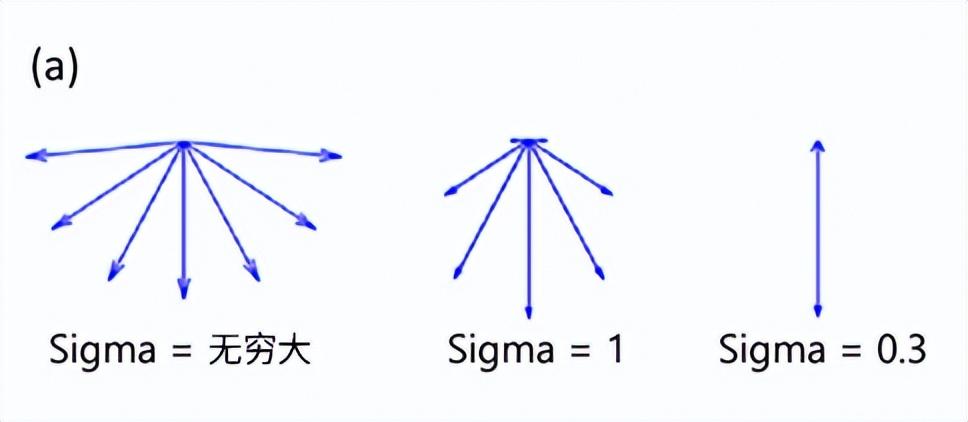

在氮化硅刻蝕步驟中,刻蝕深度、刻蝕反應(yīng)物等離子體入射角度分布(在文獻(xiàn)中稱為等離子體入射角度分布)和晶圓傾角(假定晶圓旋轉(zhuǎn))在實(shí)驗(yàn)設(shè)計(jì)期間是變化的。圖2a-f 顯示了在不同的晶圓傾角和等離子體入射角度分布值下,電容和空氣間隙的體積如何跟隨刻蝕深度發(fā)生變化。隨著刻蝕深度的增加,產(chǎn)生的空氣間隙也變大(圖2d)。因?yàn)榭諝獾慕殡姵?shù)比氮化物要低很多,所以這降低了有效的介電常數(shù)。相應(yīng)地,柵極和源極/漏極之間的寄生電容就減小了。傾斜角減小會(huì)將刻蝕反應(yīng)物從側(cè)壁移開,并將其推向所產(chǎn)生的空氣間隙底部(圖3b-c)。這解釋了為什么在給定的深度和等離子體入射角度分布值下,晶圓傾角越小,空氣間隙越大,電容越小(圖2a&d)。另一個(gè)重要的結(jié)果是,等離子體入射角度分布的增加會(huì)導(dǎo)致晶圓傾角影響減弱。當(dāng)?shù)入x子體入射角度分布設(shè)置為5度(對應(yīng)較寬/等向性的角分散)的時(shí)候,晶圓傾角對電容和空氣間隙體積完全沒有影響(圖2c&f)。這與等離子體入射角度分布增加對刻蝕的影響是一致的。等離子體入射角度分布增加會(huì)使刻蝕反應(yīng)物更等向性地轟擊基板(圖3a)。這意味著相比等離子體入射角度分布值低的時(shí)候,晶圓傾角不再影響刻蝕行為。

圖2:隨著刻蝕深度增加,空氣間隙體積增大,寄生電容減少(圖2a&d)。隨著晶圓傾角降低,這種下降更為急劇。但晶圓傾角的影響隨著等離子體入射角度分布的增加而減小,當(dāng)?shù)入x子體入射角度分布為5度時(shí),晶圓傾角對電容和空氣間隙體積沒有影響(圖2c&f)。

圖3:(a) 角分散 (sigma) 對刻蝕反應(yīng)物方向性的影響;(b) 45度晶圓傾角的影響(晶圓被固定);(c) 80度晶圓傾角的影響(晶圓旋轉(zhuǎn))

圖片來源:SEMulator3D產(chǎn)品文檔

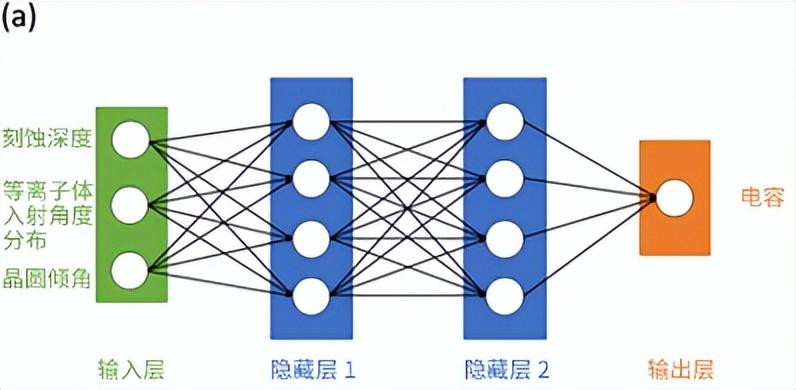

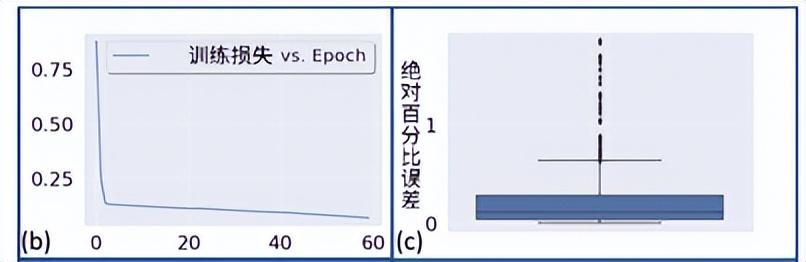

運(yùn)行大型的實(shí)驗(yàn)設(shè)計(jì)需要消耗很多時(shí)間和算力資源。但這在工藝優(yōu)化中很有必要——實(shí)驗(yàn)設(shè)計(jì)參數(shù)空間上的任何減少都有助于減少所需的時(shí)間和資源。能夠基于自變量預(yù)測結(jié)果的機(jī)器學(xué)習(xí)模型非常有用,因?yàn)樗軠p少為所有自變量組合進(jìn)行實(shí)驗(yàn)設(shè)計(jì)的需求。為了這一目標(biāo),將從實(shí)驗(yàn)設(shè)計(jì)中收集到的數(shù)據(jù)分成訓(xùn)練集 (70%) 和測試集 (30%),然后將其輸入人工神經(jīng)網(wǎng)絡(luò) (ANN)。該模型有兩個(gè)隱藏層(圖4a),用網(wǎng)格搜索法進(jìn)行超參數(shù)調(diào)優(yōu)。該模型在測試數(shù)據(jù)上運(yùn)行,發(fā)現(xiàn)其平均準(zhǔn)確度為99.8%。四分之三測試集的絕對百分比誤差 (APE) 為0.278%及以下(圖4c)。圖4e顯示了預(yù)測和實(shí)際寄生電容的測試行樣本。這種機(jī)器學(xué)習(xí)的應(yīng)用使我們能夠降低實(shí)驗(yàn)設(shè)計(jì)的規(guī)模,減少所需時(shí)間。我們可以大幅減小參數(shù)空間,與此同時(shí)并沒有明顯降低結(jié)果的準(zhǔn)確性。在我們的案例中,實(shí)驗(yàn)設(shè)計(jì)的規(guī)模從~5000減少到~2000個(gè)參數(shù)組合。SEMulator3D的自定義python步驟將這種類型的機(jī)器學(xué)習(xí)代碼整合到工藝模擬中,其結(jié)果可以導(dǎo)入半導(dǎo)體工藝模型的下一個(gè)步驟。

圖4:根據(jù)刻蝕深度、晶圓傾角和等離子體入射角度分布來預(yù)測寄生電容的人工神經(jīng)網(wǎng)絡(luò) (ANN) 模型。測試數(shù)據(jù)的預(yù)測準(zhǔn)確度為99.8%。衡量預(yù)測電容和實(shí)際電容之間差異的指標(biāo)是絕對百分比誤差 (APE)。75%測試案例的APE值為0.28%或更低。準(zhǔn)確的機(jī)器學(xué)習(xí)模型可以幫助探索更小的參數(shù)空間,從而減少所需的時(shí)間和算力資源。

結(jié)論:

使用Coventor SEMulator3D? 在FinFET器件的柵極和源極/漏極之間引入虛擬空氣間隙,我們研究了空氣間隙對寄生電容的影響,并通過改變刻蝕工藝參數(shù),研究了對空氣間隙體積和寄生電容的影響。隨后,結(jié)果被輸入到人工神經(jīng)網(wǎng)絡(luò)中,以創(chuàng)建一個(gè)可以預(yù)測寄生電容的機(jī)器學(xué)習(xí)模型,從而減少為每個(gè)刻蝕參數(shù)值組合進(jìn)行實(shí)驗(yàn)設(shè)計(jì)的需求。

參考資料:

[1] Hargrove, M. (2017, October 18). Reducing BEOL Parasitic Capacitance using Air Gaps https://www.coventor.com/blog/reducing-beol-parasitic-capacitance-using-air-gaps[2] Nitta, S., Edelstein, D., Ponoth, S., Clevenger, L., Liu, X., & Standaert, T. (2008, June). Performance and reliability of airgaps for advanced BEOL interconnects. In 2008 International Interconnect Technology Conference (pp. 191-192). IEEE.[3] Shieh, B., Saraswat, K. C., McVittie, J. P., List, S., Nag, S., Islamraja, M., & Havemann, R. H. (1998). Air-gap formation during IMD deposition to lower interconnect capacitance. IEEE Electron Device Letters, 19(1), 16-18.[4] Fischer, K., Agostinelli, M., Allen, C., Bahr, D., Bost, M., Charvat, P., … & Natarajan, S. (2015, May). Low-k interconnect stack with multi-layer air gap and tri-metal-insulator-metal capacitors for 14nm high volume manufacturing. In 2015 IEEE International Interconnect Technology Conference and 2015 IEEE Materials for Advanced Metallization Conference (IITC/MAM) (pp. 5-8). IEEE.[5] Banna, S. (2016, August). Scaling challenges and solutions beyond 10nm. In 2016 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC) (pp. 181-186). IEEE.

審核編輯黃宇

-

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

30725瀏覽量

264049 -

電容

+關(guān)注

關(guān)注

100文章

6484瀏覽量

159328 -

刻蝕

+關(guān)注

關(guān)注

2文章

220瀏覽量

13776

發(fā)布評論請先 登錄

TH2839阻抗分析儀在LED驅(qū)動(dòng)集成電路寄生參數(shù)測試分析中的應(yīng)用

碳化硅MOSFET串?dāng)_抑制策略深度解析:負(fù)壓關(guān)斷與寄生電容分壓的根本性優(yōu)勢

前道工序品質(zhì):后道工序成敗的關(guān)鍵紐帶

運(yùn)放如何減少直流分量問題?

1.3 EMC是常規(guī)設(shè)計(jì)準(zhǔn)則的例外情況

電源功率器件篇:線路寄生電感對開關(guān)器件的影響

如何匹配晶振的負(fù)載電容

逆變器寄生電容對永磁同步電機(jī)無傳感器控制的影響

電源功率器件篇:變壓器寄生電容對高壓充電機(jī)輸出功率影響

【干貨分享】電源功率器件篇:變壓器寄生電容對高壓充電機(jī)輸出功率影響

LCR測試儀中LP(Parallel)與LS(Series)模式的區(qū)別

麥科信光隔離探頭在碳化硅(SiC)MOSFET動(dòng)態(tài)測試中的應(yīng)用

減少PCB寄生電容的方法

引入空氣間隙以減少前道工序中的寄生電容

引入空氣間隙以減少前道工序中的寄生電容

評論