這里提到的局部重配置技術(Partial Reconfiguration) 是現場可編程門陣列(呵呵,就是FPGA了) 器件中的一部分。指的是在FPGA其他部分還在正常運行的情況下對其局部進行的重新配置。

眾所周知,硬件也可以像軟件一樣做模塊化的設計。比如使用HDL在FPGA器件內部,先創建子模塊,再用更高級的模塊來封裝各種子模塊。在某些情況下,如果在FPGA的一部分還在正常工作時,能實時調整其他一個或多個子模塊功能,將是一個很有好處的事情。

一般情況下,要重新配置一個FPGA需要使其處于復位狀態,并通過外部控制器重新加載一個新設計到器件中。而局部重配置技術允許在FPGA內部或外部的控制器在加載一個局部設計到一個可重配置模塊中時,設計中的其他部分仍能繼續正常工作。局部重配置還可以用于存儲多種設計時的節省空間目的,比如說只存儲多種設計之間不同的局部,設計的相同部分僅保存一次,不會重復保存。

舉個常見例子,比如在通信產品中,如果一個FPGA器件控制多個連接,一些連接可能要加密,并且要加載不同的加密IP核來處理不同的連接,這時有了局部重配置技術就不用down掉整個控制器來切換了。

目前局部重配置技術還不能支持XILINX旗下全部的FPGA產品系列。當前版本的軟件中僅支持Virtex II, Virtex II Pro, and Virtex 4系列,更新的產品系列應該在更新的軟件版本中支持。一個特殊的軟件流程要在這種模塊設計過程中被強調注意。典型情況下,這種設計模塊是建立在FPGA內部經過良好定義的邊界上的,并且需要通過特別的設計,將其映射到內部硬件上。

從設計的功能性上來分,局部重配置可以分為以下兩種:

動態局部重配置(dynamic partial reconfiguration), 顯而易見,這是個可以活動的重配置,它允許FPGA的其他部分還在正常運行的情況下改變器件的一部分。

靜態局部重配置(static partial reconfiguration),在這種重配置處理期間,器件不是活動的。當局部數據被發送入FPGA時,器件的其余部分是停止的(處于shutdown模式),配置完成后其余部分才又開始運行。

XILINX的FPGA器件的局部重配置還可以分為以下兩種類型:

基于模塊的局部重配置(Module-based partial reconfiguration)允許重配置設計中特定的模塊元件。要確保通過可重配置模塊邊界的通信,需要事先準備好一種特殊的總線宏單元。該總線宏單元作為一種固定的路由橋工作,連接設計中空余部分的可重配置模塊。基于模塊的局部重配置在設計規范階段需要運行一套特定的Guidelines。最終為設計中的每個可重配置模塊都創建一個分立的bit流。這樣的bit流即可被用來運行局部重配置。

基于區別的局部重配置(Difference-based partial reconfiguration) 可以被用在對設計的一次小修改上。尤其是在改變LUT等式或存儲器塊內容時尤為有效。這樣的局部bit流僅包含現有設計結構和新結構之間的區別信息。基于區別的局部重配置有兩種方式:前端和后端。前端方式基于硬件描述語言(HDL)的修改。這種方式對于一個需要完全重復綜合和實現過程的解決方案來講是很清晰的。后端方式允許在原型設計的實現階段進行修改,因此不需要重新執行綜合過程。兩種方式的運用都會創建局部bit流,并都能用于FPGA的局部重配置功能。

需要提示注意的是:局部重配置僅能更新FPGA的一部分。更新期間不需要FPGA的任何部分繼續運行。

審核編輯 :李倩

-

FPGA

+關注

關注

1662文章

22480瀏覽量

638548 -

控制器

+關注

關注

114文章

17850瀏覽量

194809 -

賽靈思

+關注

關注

33文章

1798瀏覽量

133607

原文標題:談談賽靈思的局部重配置技術(Partial Reconfiguration)

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

賽靈思FPGA電源解決方案全解析

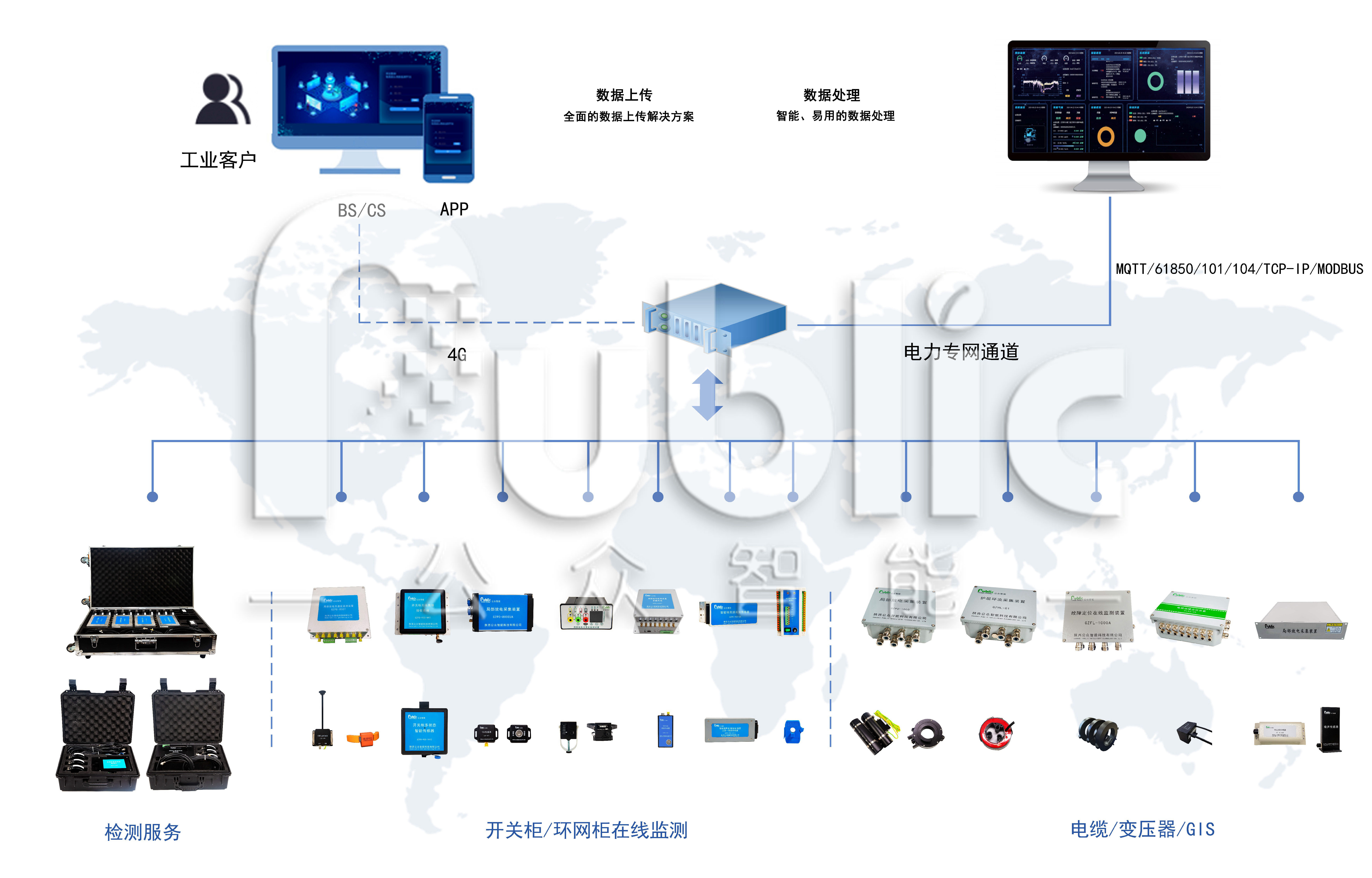

局部放電監測設備在不同場景下的配置應用

強強聯合進軍萬億晶振市場,賽思電子與一晶科技成立合資公司

易靈思與思特威第二屆機器視覺方案大會圓滿收官

易靈思 FPGA TJ375的PLL的動態配置

授時系統廠家,授時系統哪家好?賽思高精度授時系統助力華福證券授時服務新升級!

賽思快訊 | 嘉興市委書記陳偉一行蒞臨賽思調研

賽靈思的局部重配置技術(Partial Reconfiguration)

賽靈思的局部重配置技術(Partial Reconfiguration)

評論