視覺是人類最高級別的感知,以視頻、圖像等形式為信息載體可以創造出豐富多彩的應用。視覺信息處理技術的實現和發展極大改變了現代社會的生產活動:智能設備的拍照和視頻、醫學成像、人臉識別、科學可視化、行車記錄、安防監控、國防探測、太空探索等前沿領域無不滲透著視覺信息處理技術,視覺信息處理已無處不在,并形成龐大的上下游產業。

隨著算法水平不斷進步和計算機處理能力以及存儲能力的提升,再加上市場日益增長的消費應用升級的推動,從真實世界中得到的視覺信息數據通過ADC采集、再到數字化的算法處理分析、再經過DAC的轉換輸出技術,已經發展到相當復雜的水平,其中圖像傳感器采集數據的像素不斷提升,圖像信號處理器能夠實現自動對焦、自動曝光、壞點去除、鏡頭陰影矯正、去馬賽克、顏色矯正、伽馬矯正、降噪、數據的壓縮和存儲等各種功能,滿足更前沿的應用場景使得當前圖像處理設計需要支持復雜多樣的功能,同時當前數字圖像處理的應用越來越趨向于小型化SoC系統以適應移動互聯網的蓬勃發展,實現多重功能和高集成度需求使得當前的SoC設計復雜度指數級提升,同時對設計的仿真驗證提出了更高要求,不僅需要對圖形處理設計模塊進行大量測試驗證,還需要對目標SoC進行充分的評估和驗證。

亞科鴻禹VeriTiger原型驗證系統

圖像處理解決方案

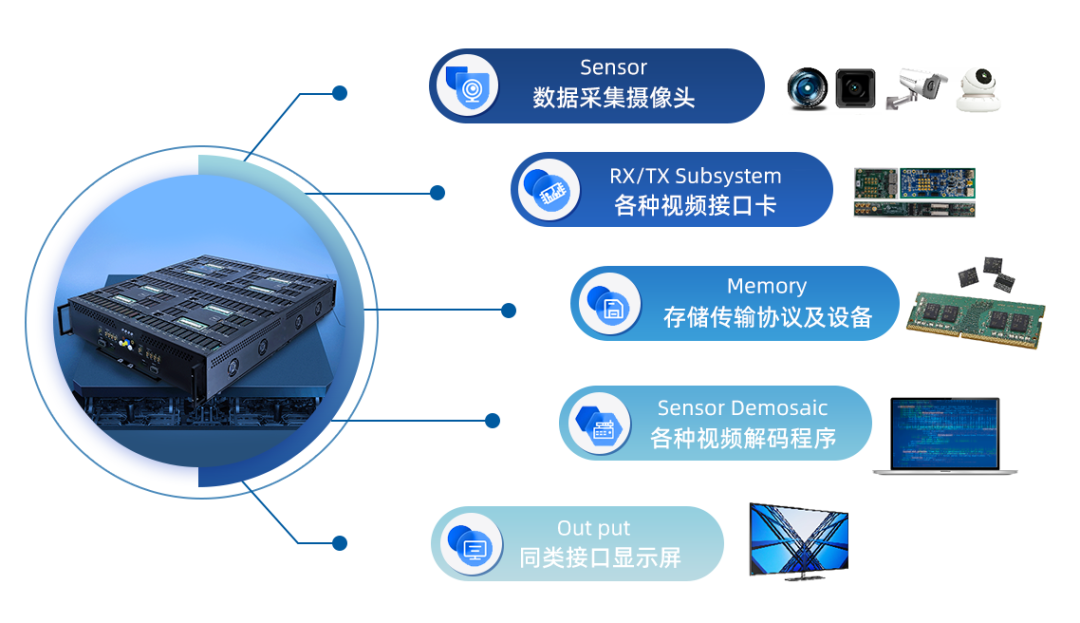

圖像處理是最直觀可視的應用功能實現,FPGA原型驗證系統利用真實的傳感設備和輸出顯示設備提供直觀可視的DUT執行結果展現,是最適合進行圖像處理設計功能驗證的手段。亞科鴻禹VeriTiger原型驗證系統為各類圖像處理設計提供高性能原型驗證解決方案。

VeriTiger圖像處理原型驗證解決方案整體框架

VeriTiger原型驗證系統圖像處理解決方案的硬件環境由VeriTiger原型驗證母板、配套功能子卡、采集攝像頭、輸出顯示器、數據傳輸連接線組成,通過子卡提供真實的外設來構建設計原型,進行功能驗證并提供深度調試。配合我司自研軟件ProtoWizard可以進行時鐘電壓的配置,bit文件的燒錄以及統一的子卡管理。

為應對不同的視覺信息處理場景,圖像處理SoC設計會選用各種類型的接口協議以滿足對采集像素、傳輸速度、集成度等的不同需求。DP、HDMI、MIPI是當前最為常見的多媒體處理接口類型,亞科鴻禹基于VeriTiger原型驗證平臺,提供成熟的DP、HDMI、MIPI子卡硬件以及工程方案。在SoC原型驗證過程中,采用VeriTiger原型驗證平臺和相關子卡組成完整的驗證解決方案,進行SoC相關場景接口的驗證,可極大縮短原型驗證平臺的搭建時間,提升驗證效率,從而進一步縮短SoC的開發時間。

01

“DP外設驗證需求” 解決方案:

通過亞科鴻禹自研的HSMGT-DSIP、HSPI2-GPIO等子卡完成原型環境創建,啟動工程驗證。HSMGT-DSIP為DISPLAY輸入輸出子卡,該方案支持Xilinx原生的DISPLAY協議,通過調用Xilinx提供的DisplayPort 1.4 RX Subsystem和DisplayPort 1.4 TX Subsystem IP,選擇本地或AXI4-Stream視頻輸入接口,支持MST和SST輸出。其中包含一個專用輸入DP接口和一個專用輸出DP接口,一組GPIO。使用時可單獨開發DP的TX發送端或RX接收端功能;RX端可將HPD、AUX等信號抓取,針對調試DP握手時遇到的問題提供更多的解決思路。

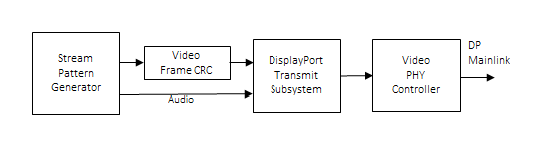

TX工程整體結構如下圖:

視頻數據由Stream Pattern Generator產生,通過CRC校驗后傳輸給TX Subsystem,經過處理后給到Video PHY Controller,最后通過DP Mainlink輸出。

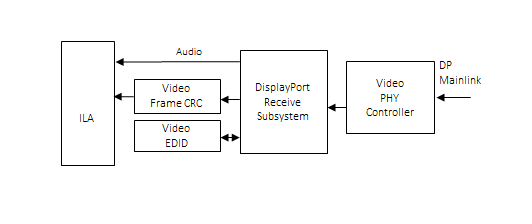

RX工程整體結構如下圖:

數據由DP Mainlink進入,經過Video PHY Controller處理后給到RX Subsystem,隨后進行EDID等數據的確認,建立握手后數據經過CRC校驗,給到ILA。

方案適用于驗證:

大型視頻處理系統中串行數字視頻數據接收和發送的插件設計。

02

“HDMI外設驗證需求” 解決方案:

通過亞科鴻禹自研的HSMGT-HD20等子卡完成原型環境創建,啟動工程驗證。HSMGT-HD20子卡為HDMI2.0輸入輸出子卡。該方案通過調用Xilinx提供的HDMI Transmitter/Receiver Subsystem IP,從PHY層接收捕獲的TMDS數據,然后從HDMI流中提取視頻和音頻流,并將其轉換為視頻和音頻流,以便進行視頻、音頻的處理,隨后由HDMI Transmitter Subsystem將處理好的視頻和音頻流傳輸到HDMI流,從而完成視頻流的傳輸,可選擇AXI4-Stream、Native Video作為HDMI 1.4/2.0子系統的視頻接口。該子卡包含一個專用輸入HDMI接口和一個專用輸出HDMI接口,一個時鐘芯片,一個顯示端口重定時器。該子卡輸出為TI的PHY,輸入直接接到了FPGA的MGT通道。使用時可以單獨開發HDMI的TX或者RX功能;TX端掛載了顯示端口重定時器,支持高達6Gbps的數據速率。搭配時鐘芯片,可滿足不同分辨率輸出下所需求的時鐘速率。

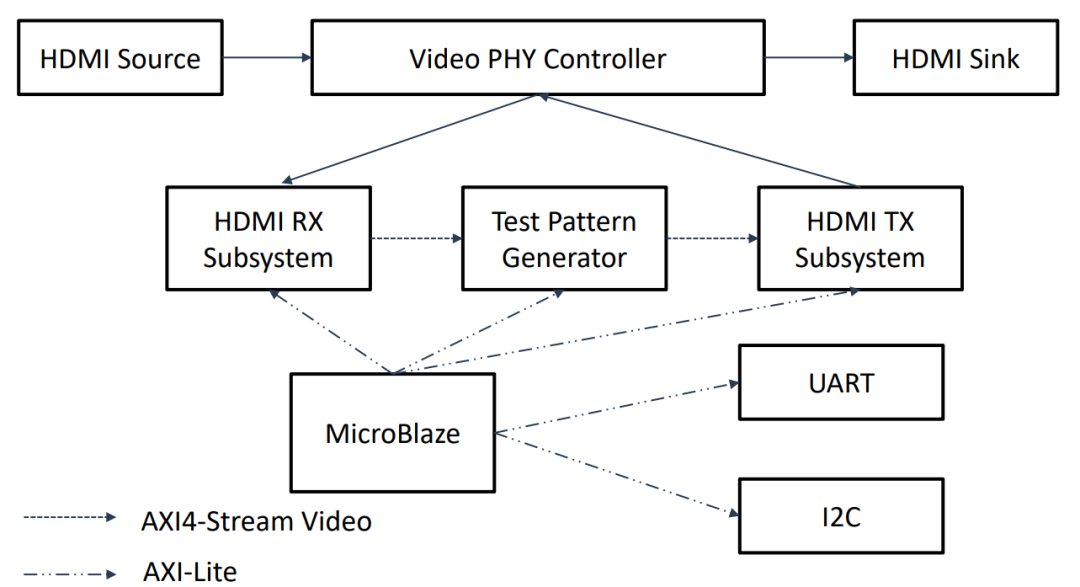

下圖為該工程整體結構:

工程支持兩種工作方式:

1. Passthrough工作模式。

該模式下,視頻數據通過Source端給入HDMI RX Subsystem,經過處理后由HDMI TX Subsystem輸出到Sink端,完成視頻數據的接收和發送。

2. TX工作模式。

該模式下,視頻數據由MicroBlaze產生,經過處理后通過HDMI TX Subsystem輸出到Sink端。

方案適用于驗證:

HDMI視頻系統中HDMI接收和發送的插件設計。

03

“MIPI(Mobile Industry

Processor Interface)

外設驗證需求”解決方案:

MIPI移動產業處理器接口(Mobile Industry Processorinterface)是為移動應用處理器制定的開放標準。現代移動應用設備由于高分辨率的要求,現在基本上都是基于MIPI協議來實現的。方案通過亞科鴻禹自研的HSPI2-MIPI等子卡完成原型環境創建,啟動工程驗證。HSPI2-MIPI子卡為MIPI攝像頭子板,用于視頻接收。該方案采用MIPI CSI-2 RX Subsystem IP,該子系統從MIPI CSI-2攝像機傳感器捕獲圖像,并輸出AXI4- Stream視頻數據,以便進行圖像處理。該子系統允許快速選擇頂級參數,并自動完成大部分較低級別參數化,AXI4-Stream視頻接口允許與其他基于AXI4-Stream的子系統無縫連接。該子卡包含兩路MIPI微型接頭,支持ov9281,ov9280;兩路FPC接口,支持ov5640;支持三路MMCX差分對。兩種不同的攝像頭接口,為客戶提供了不同的選擇。

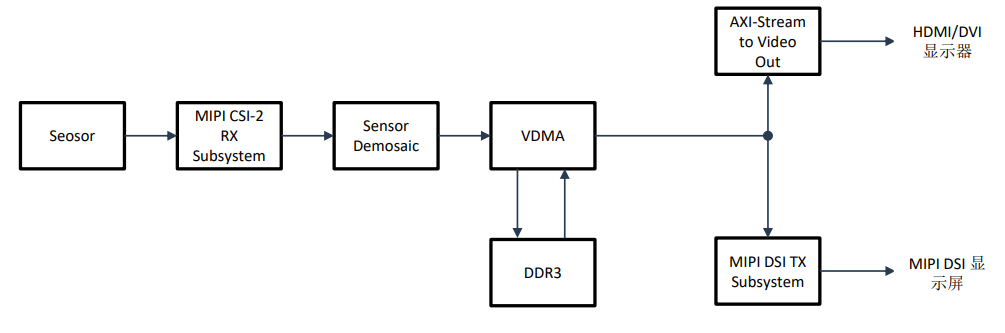

工程整體結構:

數據通過Sensor采集后給到 MIPI CSI-2 RX Subsystem,經過Sensor Demosaic,將拜爾圖像傳感器捕獲的圖像還原出符合色彩顯示設備的真實世界色彩后給到VDMA,VDMA將視頻數據緩存并輸出。輸出視頻數據格式支持AXI-Stream和MIPI PHY形式。

方案適用于驗證:

高集成度、高傳輸速率要求的移動設備圖像處理設計。

審核編輯:劉清

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636419 -

圖像傳感器

+關注

關注

68文章

2075瀏覽量

132214 -

圖像處理

+關注

關注

29文章

1342瀏覽量

59543 -

dac

+關注

關注

44文章

2713瀏覽量

197098 -

ADC采集系統

+關注

關注

0文章

4瀏覽量

2094

原文標題:基于FPGA原型驗證系統的圖像處理解決方案

文章出處:【微信號:于博士Jacky,微信公眾號:于博士Jacky】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

大科學裝置信號采集處理解決方案

RK3588采集Cameralink圖像快速搭建系統辦法

思爾芯榮登“國產EDA工具口碑榜”,以“芯神瞳”原型驗證解決方案賦能芯片創新

嵌入式和FPGA的區別

FPGA原型驗證實戰:如何應對外設連接問題

【喜報】芯神瞳原型驗證解決方案榮膺工博會“集成電路創新成果獎”

西門子桌面級原型驗證系統Veloce proFPGA介紹

超大規模芯片驗證:基于AMD VP1902的S8-100原型驗證系統實測性能翻倍

求一種基于FPGA原型驗證系統的圖像處理解決方案

求一種基于FPGA原型驗證系統的圖像處理解決方案

評論