No.1 案例背景

當芯片底部出現焊接不良的問題時,我們可以怎么進行失效分析呢?

本篇案例運用X-ray檢測——斷面檢測——焊錫高度檢測——SEM檢測的方法,推斷出芯片底部出現焊接不良的失效原因,并據此給出改善建議。

No.2 分析過程

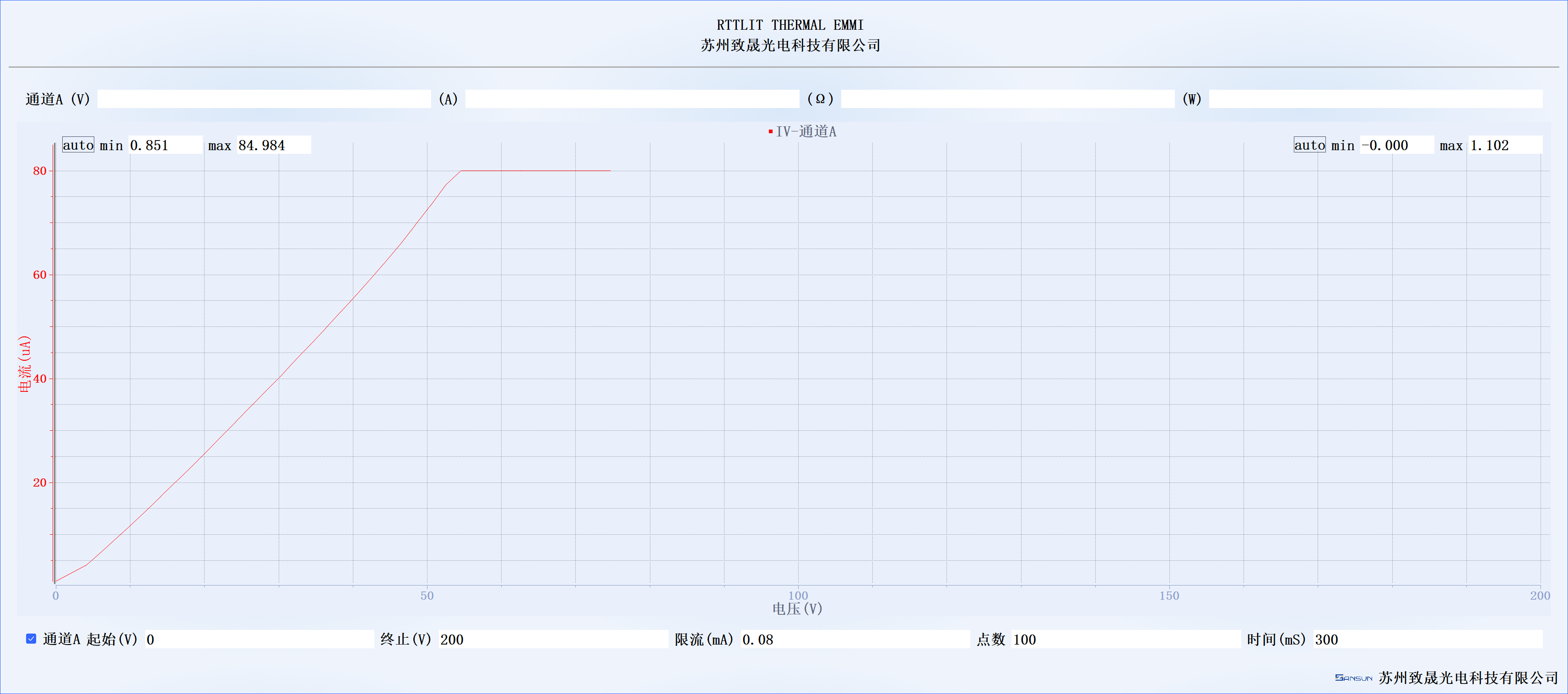

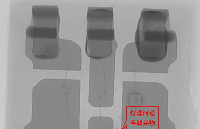

X-ray檢測

說明

對樣品進行X-ray檢測,存在錫少、疑似虛焊不良的現象。

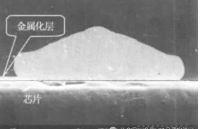

斷面檢測

#樣品斷面檢測研磨示意圖

位置1

位置2

位置3

說明

樣品進行斷面檢測,底部存在錫少,虛焊的現象。且芯片底部焊錫與PCB焊錫未完全融合。

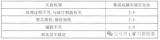

焊錫高度檢測

引腳焊錫高度0.014mm

芯片底部焊錫高度0.106mm

說明

芯片引腳位置焊錫高度0.014mm,芯片未浮起,芯片底部高度為0.106mm,錫膏高度要大于芯片底部高度才能保證焊接完好。

SEM檢測

說明

對底部焊接的位置進行SEM檢測,芯片與PCB之間焊錫有縫隙,焊錫未完全融合,IMC致密性差,高度5μm左右。

No.3 分析結果

通過X-ray、斷面分析以及SEM分析,判斷引起芯片底部焊接失效的原因主要有——

① 芯片底部存在錫少及疑似虛焊不良的現象;

② 芯片底部焊錫與PCB焊錫未完全融合的現象。而且,芯片焊接未浮起,芯片底部高度僅為0.106mm。只有當錫膏高度大于芯片底部高度時,才能保證焊接完好;

③ 芯片與PCB之間焊錫有縫隙,焊錫未完全融合,IMC致密性差,高度4-5μm左右;

根據以上綜合分析,造成芯片底部焊接虛焊的原因推測為:

1. 錫膏厚度不足導致底部焊接虛焊;

2.焊接時熱量不足導致焊錫液相時間不足。

No.4 改善方案

1. 建議實際測量錫膏高度(L)與芯片底部高度(A1)后進行調整;

2. 建議根據實際測量情況,適當調整芯片底部焊錫液相時間。

新陽檢測中心有話說:

本篇文章介紹了芯片底部焊接失效分析。如需轉載本篇文章,后臺私信獲取授權即可。若未經授權轉載,我們將依法維護法定權利。原創不易,感謝支持!

新陽檢測中心將繼續分享關于PCB/PCBA、汽車電子及相關電子元器件失效分析、可靠性評價、真偽鑒別等方面的專業知識,點擊關注獲取更多知識分享與資訊信息。

審核編輯黃宇

-

芯片

+關注

關注

463文章

54007瀏覽量

465949 -

失效分析

+關注

關注

18文章

250瀏覽量

67736

發布評論請先 登錄

芯片失效故障定位技術中的EMMI和OBIRCH是什么?

聚焦離子束(FIB)技術在芯片失效分析中的應用詳解

熱發射顯微鏡下芯片失效分析案例:IGBT 模組在 55V 就暴露的問題!

漢思新材料:底部填充膠可靠性不足如開裂脫落原因分析及解決方案

LED失效的典型機理分析

LED芯片失效和封裝失效的原因分析

聚徽解碼工業觸控一體機I/O端口接觸不良:焊接修復與防護策略

離子研磨在芯片失效分析中的應用

如何降低焊接不良對PCBA項目的影響?

芯片底部填充膠填充不飽滿或滲透困難原因分析及解決方案

芯片底部焊接不良失效分析

芯片底部焊接不良失效分析

評論