高K介質 (High-k Dielectric)和替代金屬柵 (RMG)工藝

2007年,Intel 公司宣布在 45nm CMOS 工藝節點上成功地使用高k氧化鉿基(Hf-oxide Based)介質和金屬柵工藝,可以顯著減少柵介質泄漏電流和增加柵導電能力。

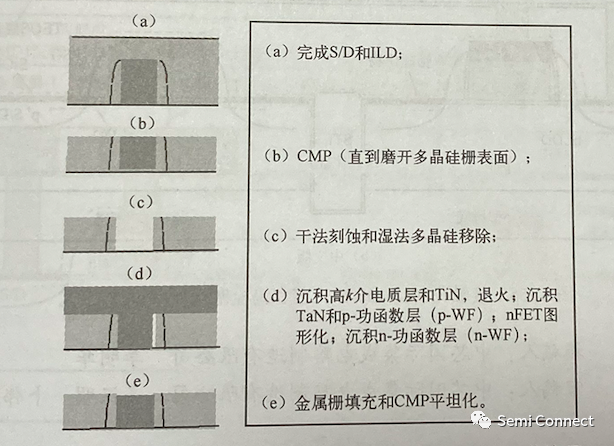

但高k氧化鉿基柵介質較易被源漏退火步驟的熱過程引起結晶化,導致較大的泄漏電流,因此高k介質金屬柵模塊工藝需要在源漏之后再形成,這被稱為后柵(Gate Last)工藝或替代金屬柵 ( Replacement Metal Gate, RMG)工藝,如圖所示。

因此,高k介質(如 HfO2、HfSiOx、HfSiON)和金屬柵(如TiN、TiAl、Al 或W等)模塊便成為 32nm/28nmn 和更先進節點上的標準配備;后柵工藝或替代金屬柵工藝也成為產業界先進 CMOS 工藝節點(28nm 節點之后)采用的主流工藝方案。

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

CMOS

+關注

關注

58文章

6217瀏覽量

242828 -

AMOL

+關注

關注

0文章

2瀏覽量

8749 -

RMGI

+關注

關注

0文章

2瀏覽量

5492

原文標題:中段集成工藝(MOL Integration Flow)- 2

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

高k金屬柵(HKMG)工藝詳解

隨著集成電路工藝技術不斷發展,為了提高集成電路的集成度,同時提升器件的工作速度和降低它的功耗,集成電路器件的特征尺寸不斷按比例縮小,工作電壓不斷降低。為了有效抑制短溝道效應,除了源漏的結深不斷降低

什么是本體偏壓/次臨界漏電 (ISUBTH)/High-k

什么是本體偏壓/次臨界漏電 (ISUBTH)/High-k 電介質/High-k 電介質/GIDL

本體偏壓通過改變電路上的電壓來減少電流泄漏的技術。將電路

發表于 03-05 15:29

?859次閱讀

高介電常數柵電介質/金屬柵極的FA CMP技術

高介電常數柵電介質和金屬柵極技術(以下簡稱HKMG)使摩爾定律在45/32納米節點得以延續。目前的HKMG工藝有兩種主流整合方案,分別是先柵

發表于 05-04 17:11

?8156次閱讀

IMEC發布后柵極HKMG制式細節,英特爾、三星受益

電子發燒友網訊:納米電子研究中心IMEC (Leuven, Belgium) 正評估用未來新型三極管替代金屬柵極(RMG)技術和當前高K金屬

發表于 06-14 11:45

?1883次閱讀

現代集成電路芯片14nm節點FinFET的制造工藝流程詳細資料說明

—LDD注入—側墻主隔離—漏源極形成(應變硅技術)—金屬硅化物—器件與金屬間介質層ILD—置換高k金屬

發表于 04-10 08:00

?161次下載

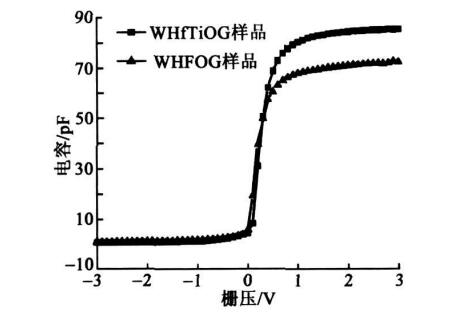

一文讀懂HfTiO高柵介質GeMOS電容

采用反應磁控濺射方法和濕氮退火工藝在Ge襯底上分別制備了HfO2和HfTiO高介電常數(k)柵介質薄膜。電特性測量表明,HfTiO樣品由于T

發表于 03-29 10:24

?27次下載

集成電路制造工藝的演進

為了提高晶體管性能,45nm/28nm以后的先進技術節點采用了高介電常數柵介質及金屬柵極(High-k Metal Gate,HKMG)

高K金屬柵工藝(HKMG)

目前,高K柵介質與金屬柵極技術已廣泛應用于 28mmn 以下高性能產品的制造,它在相同功耗情況下可以使集成電路的性能大幅度提高,泄漏電流大幅

高k柵介質NMOSFET遠程聲子散射對溝道遷移率的影響

器件溝道長度為1μm,HFO2柵介質厚度為4.88nm;SiO2柵介質厚度為2nm;P襯底摻雜濃度4E15cm^-3;柵電極為鋁

發表于 07-05 16:45

?1588次閱讀

High-k柵極堆疊技術的介紹

的尺寸持續縮減,二氧化硅層的厚度也相應變薄,這引發了嚴重的漏電問題,進而影響了元件的性能表現和功耗效率。High-k柵極堆疊技術則通過引入具備高介電常數的材料,對傳統二氧化硅柵極絕緣層進行了革新性替代。

集成電路新突破:HKMG工藝引領性能革命

隨著集成電路技術的飛速發展,器件尺寸不斷縮小,性能不斷提升。然而,這種縮小也帶來了一系列挑戰,如柵極漏電流增加、多晶硅柵耗盡效應等。為了應對這些挑戰,業界開發出了高K金屬柵(

高K介質(High-k Dielectric)和替代金屬柵(RMG)工藝介紹

高K介質(High-k Dielectric)和替代金屬柵(RMG)工藝介紹

評論