由于測試芯片的復(fù)雜性和覆蓋范圍的原因,單個(gè)小芯片對復(fù)合材料成品率下降的影響正在為晶圓測試帶來新的性能要求。從測試的角度來看,使小芯片成為主流技術(shù)取決于確保以合理的測試成本獲得“足夠好的模具”

在異構(gòu)集成系統(tǒng)中,由于單個(gè)小芯片而導(dǎo)致的復(fù)合成品率下降的影響,就晶圓復(fù)雜度和測試復(fù)雜性而言,為晶圓測試帶來了新的性能要求。從測試的角度來看,使小芯片成為主流技術(shù)取決于確保以合理的測試成本獲得“足夠好的模具”。

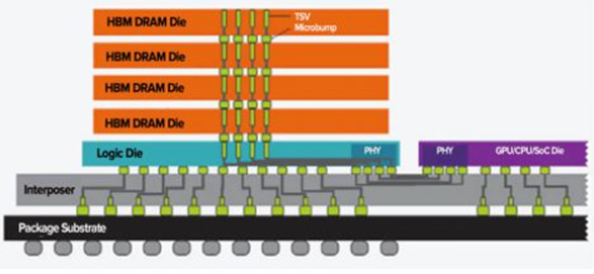

晶圓級測試在小芯片制造過程中扮演著至關(guān)重要的角色。以HBM(高帶寬內(nèi)存)為例,它可以及早發(fā)現(xiàn)有缺陷的DRAM和邏輯芯片,以便可以在復(fù)雜而昂貴的堆疊階段之前將其刪除。堆疊后晶圓的進(jìn)一步測試可確保完成的堆疊在切割成獨(dú)立組件之前具有完整的功能。理想情況下,每個(gè)DRAM芯片在堆疊之前都應(yīng)進(jìn)行已知良好芯片(KGD)測試,以獨(dú)立驗(yàn)證其性能。但這在經(jīng)濟(jì)上通常是不可行的。在某些時(shí)候,測試成本超過了系統(tǒng)完成后增加的價(jià)值。 因此,需要一種平衡測試成本和未做芯片不良率檢測的測試策略,以將異構(gòu)集成引入大批量生產(chǎn)。

得益于MEMS探針卡技術(shù)的創(chuàng)新,F(xiàn)ormFactor的產(chǎn)品可以幫助客戶實(shí)現(xiàn)全流程的KGD測試(例如支持45μm柵格陣列間距微凸點(diǎn)測試的Altius?探針卡,用于高速HBM和Interposer插入連接器的良品率驗(yàn)證),并且可以接受有限的測試成本(例如SmartMatrix?探針卡,通過同時(shí)測試300mm晶圓上的數(shù)千個(gè)芯片,大大降低了每個(gè)芯片的測試成本)。 最終,我們在小型芯片制造過程的每個(gè)階段獲得有關(guān)產(chǎn)品性能和成品率的更多信息,從而幫助客戶降低總體制造成本。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

463文章

54010瀏覽量

466098 -

晶圓測試

+關(guān)注

關(guān)注

1文章

45瀏覽量

13857 -

chiplet

+關(guān)注

關(guān)注

6文章

495瀏覽量

13604

發(fā)布評論請先 登錄

先進(jìn)封裝時(shí)代,芯片測試面臨哪些新挑戰(zhàn)?

半導(dǎo)體晶圓拋光有哪些技術(shù)挑戰(zhàn)

季豐電子嘉善晶圓測試廠如何保障芯片質(zhì)量

探秘晶圓宏觀缺陷:檢測技術(shù)升級與根源追蹤新突破

攻克存儲芯片制造瓶頸:高精度晶圓切割機(jī)助力DRAM/NAND產(chǎn)能躍升

聚氨酯墊性能優(yōu)化在超薄晶圓研磨中對 TTV 的保障技術(shù)

現(xiàn)代晶圓測試:飛針技術(shù)如何降低測試成本與時(shí)間

TC Wafer晶圓測溫系統(tǒng)當(dāng)前面臨的技術(shù)挑戰(zhàn)與應(yīng)對方案

提供半導(dǎo)體工藝可靠性測試-WLR晶圓可靠性測試

從技術(shù)封鎖到自主創(chuàng)新:Chiplet封裝的破局之路

晶圓揀選測試的具體過程和核心要點(diǎn)

從晶圓測試角度來看,使小芯片(Chiplet)成為主流技術(shù)所面臨的最大挑戰(zhàn)是什么?

從晶圓測試角度來看,使小芯片(Chiplet)成為主流技術(shù)所面臨的最大挑戰(zhàn)是什么?

評論