Verilog提供了很多對文件操作的系統任務和函數,例如打開關閉文件、向文件寫入值、從文件讀出值等等。

當我們使用這些文件操作時,需要注意文件屬性和變量內容,選擇正確的系統任務,提供相關參數,以避免一些不必要的錯誤。這里主要介紹關于文件打開/關閉、文件寫入和文件讀出相關的操作。

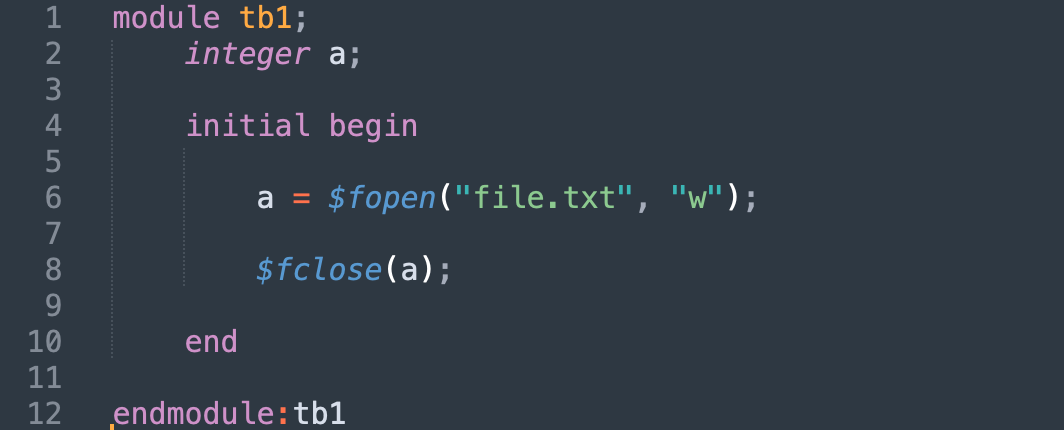

文件打開/關閉

| 文件打開 | a=$fopen("file.txt","w") | 打開file.txt文件,a為返回32bit文件描述符 |

| 文件關閉 | $fclose(a) | 關閉a描述的對應文件 |

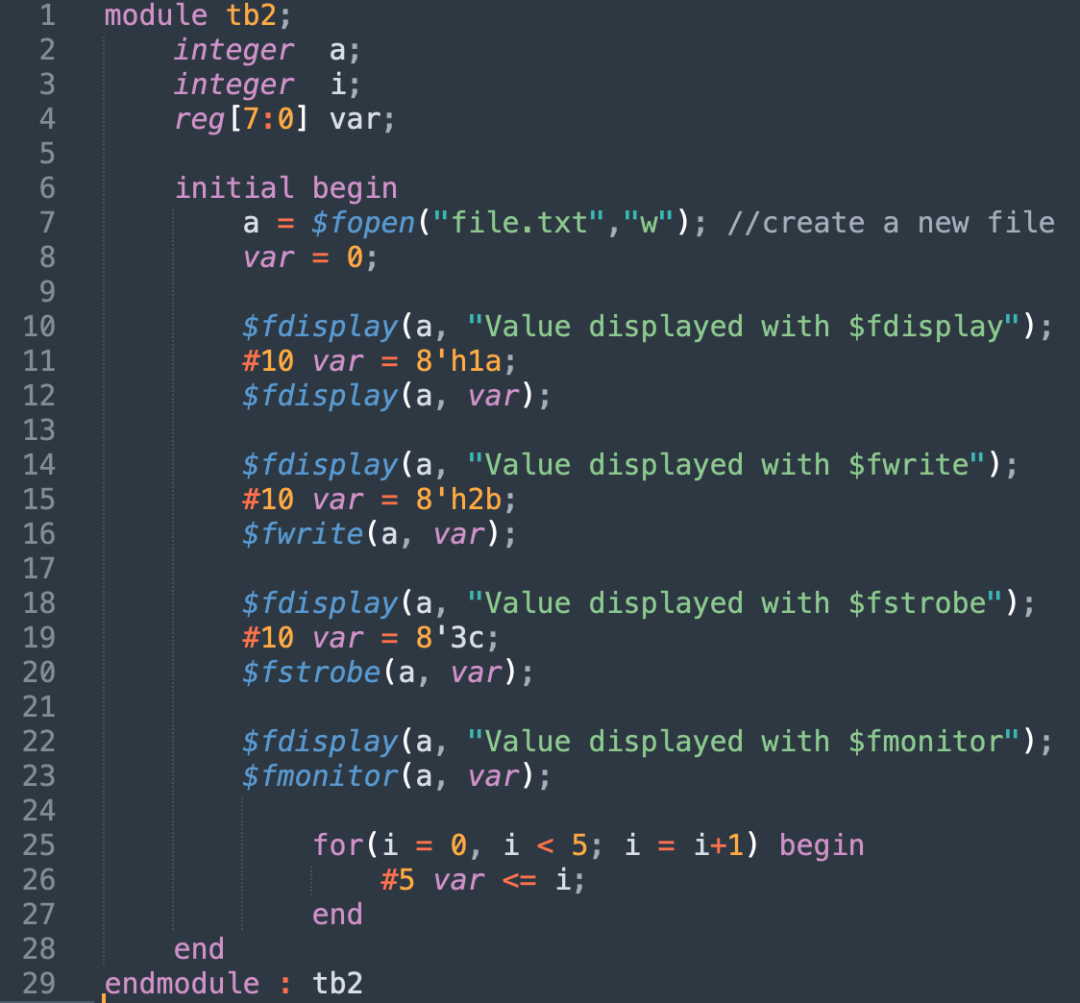

文件寫入

| $fdisplay | 按順序或條件寫,自動換行 |

| $fwrite | 按順序或條件寫,不自動換行 |

| $fstrobe | 語句執行完畢后選通寫文件 |

| $fmonitor | 只要有數據變換就寫文件 |

文件讀出

| $fgetc | 按字符讀文件 |

| $fgets | 按行讀文件 |

| $fscanf | 按格式讀文件 |

| $fread | 按二進制讀文件 |

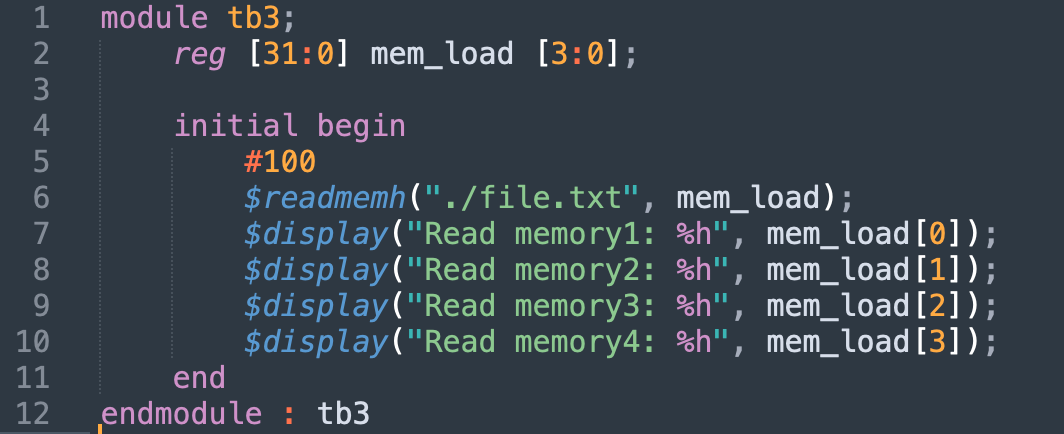

除此之外,還有兩個常用的系統任務$readmemb和$readmemh,用于從文件中讀取數據到存儲器中。讀取的內容只包括:空白位置(空格、換行、制表格(tab和form-feeds),注釋行、二進制或十六進制的數字。

假設file.txt文件中的數據為

12345678

5a5a5a5a

deadbeef

87654321

本文主要介紹常用的文件操作系統任務,其余沒介紹的大家可以按需學習。

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Verilog

+關注

關注

30文章

1374瀏覽量

114520 -

函數

+關注

關注

3文章

4417瀏覽量

67499 -

文件操作

+關注

關注

0文章

7瀏覽量

5473

原文標題:Verilog中關于文件操作的系統任務

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

關于verilog中的生成塊和任務

本帖最后由 耶穌牛肚 于 2017-1-4 20:27 編輯

自學verilog,看到生成塊和任務的時候有一些迷茫,希望大神講解一下。生成塊書上說本質是將多條重復語句化為一條起到簡化的作用

發表于 01-04 20:25

可以在硬件(Verilog)中更輕松地完成此任務嗎?

數據。我最初的想法是可以使用某種形式的軟件(C,C ++)來完成這項任務。我對回讀機制的理解是否正確?可以在硬件(Verilog)中更輕松地完成此任務嗎?對于那些做過回讀的人,你使用了

發表于 05-29 13:55

【資料】RT-Threa操作系統中任務的概念及實現任務所用到的數據結構

的概念,所有任務都在同一個地址空間中,此時系統中唯一的進程就是我們燒錄的整個系統可執行文件。通常在類似RT-Thread這類實地址運行的嵌入

發表于 03-23 15:11

ISE中的Verilog Test Fixture類型的.v文件為啥在Implementation中顯示?如何修改?

不知為啥,發現用于仿真的Verilog Test Fixture類型的.v文件在Implementation中顯示,看著很不舒服,但也不知道怎么改,如下圖所示,紅框中的TestDual

發表于 02-10 15:17

?2628次閱讀

如何使用Icarus Verilog+GTKWave來進行verilog文件的編譯和仿真

本文將介紹如何使用Icarus Verilog+GTKWave來進行verilog文件的編譯和仿真。 Icarus Verilog Icarus V

FPGA中如何使用Verilog處理圖像

的完整 Verilog 代碼 。 在這個FPGA Verilog項目中,一些簡單的處理操作都是在Verilog中實現的,比如反相、亮度控制和

UCOSIII操作系統學習筆記——任務

RTOS系統RTOS全程為:Real Time OS,就是實時操作系統。實時操作系統分為硬實時和軟實時。硬實時要求在規定時間內必須完成操作,硬件實時

發表于 12-02 13:51

?2次下載

Verilog數字系統設計——任務和函數二(系統任務readmemb或readmemh)

Verilog數字系統設計十任務和函數實驗2文章目錄Verilog數字系統設計十前言一、Verilog

發表于 12-05 19:06

?7次下載

Verilog設計中函數和任務的作用分析

任務和函數在Verilog中用于描述常用的功能行為。與其在不同的地方復制相同的代碼,不如根據需求使用函數或任務,這是一種良好且常見的做法。為了便于代碼維護,最好使用子例程之類的函數或任務

Verilog系統函數和邊沿檢測

“ 本文主要分享了在Verilog設計過程中一些經驗與知識點,主要包括Verilog仿真時常用的系統任務、雙向端口的使用(inout)、邊沿檢測”

verilog中函數和任務對比

在verilog中,函數和任務均用來描述共同的代碼段,并且在模式內任意位置被調用,提高代碼效率,讓代碼更加的直觀,提高代碼可讀性。但是在實際使用的過程中,函數和

verilog中for循環是串行執行還是并行執行

在Verilog中,for循環是并行執行的。Verilog是一種硬件描述語言,用于描述和設計數字電路和系統。在硬件系統

Verilog中關于文件操作的系統任務

Verilog中關于文件操作的系統任務

評論