本文將介紹如何使用Icarus Verilog+GTKWave來進行verilog文件的編譯和仿真。

Icarus Verilog

Icarus Verilog極其小巧,支持全平臺Windows+Linux+MacOS,并且源代碼開源。通過tb文件可以生成對應的仿真波形數據文件,通過GTKWave可以查看仿真波形圖,支持將Verilog轉換為VHDL文件。

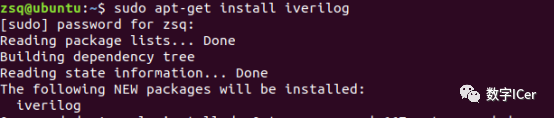

1.安裝iverilog:

sudo apt-get install iverilog

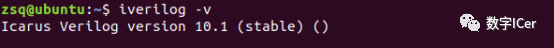

安裝完成查看版本

iverilog -v

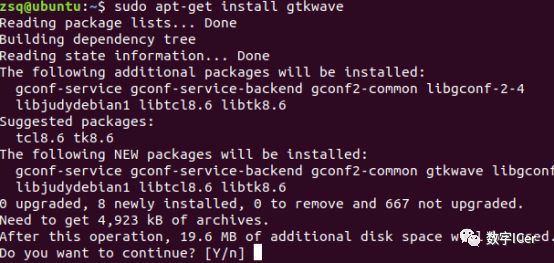

2.安裝gtkwave:

sudo apt-get install gtkwave

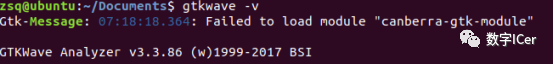

安裝完成查看版本

gtkwave -v

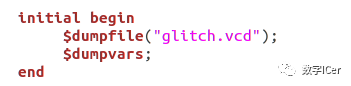

Tb中添加

3.編譯:

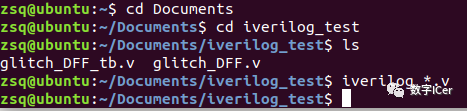

進入文件目錄,輸入命令:

iverilog *.v

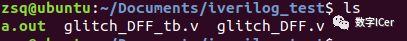

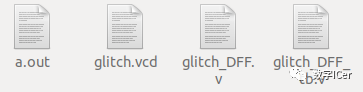

編譯完成出現.out文件

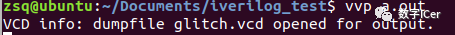

生成.vcd文件

vpp a.out

執行后產生的文件如下:

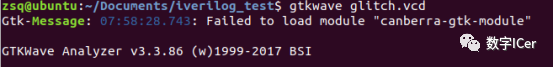

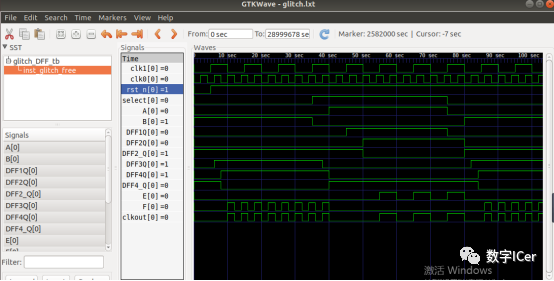

4.用GTKWave打開VCD文件:

gtkwave glitch.vcd

執行完成后,彈出界面

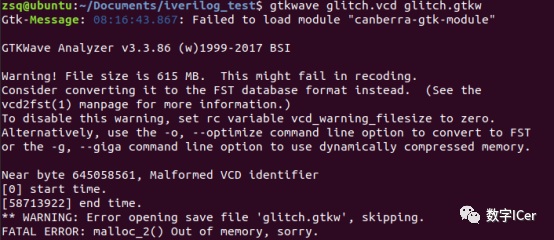

添加波形的時候卡死

glitch.vcd文件太大???

解決:

gtkwave,icarus支持vcd,lxt,lxt2 dump.

vcd通用但vcd dump太大,gtkwave不能很好的查看波形,導致崩潰。所以最好之前用lxt或將vcd轉化為lxt格式。lxt格式是gtkwave的專用格式。

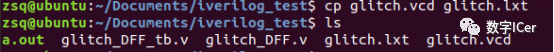

cp glitch.vcd glitch.lxt

添加波形

5.Verilog轉換為VHDL

將glitch.v文件轉換為VHDL文件glitch.vhd

iverilog -tvhdl -o glitch.vhd glitch.v

編輯:jq

-

仿真

+關注

關注

54文章

4466瀏覽量

138069

原文標題:開源verilog仿真工具iverilog+GTKWave初體驗

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

請問測試用例.verilog文件是怎么生成的呢?

利用 NucleiStudio IDE 和 vivado 進行軟硬件聯合仿真

使用NucleiStudio生成tb仿真需要的.verilog文件

芯來e203移植開發分享(二)——仿真文件簡述與itcm固化程序

在Ubuntu上安裝iverilog 12.0方法

NucleiStudio如何生成.verilog文件和.dasm文件,以及對.dasm文件中自定義指令反匯編結果分析

Linux使用coremark程序進行vcs仿真的注意事項

verilog模塊的調用、任務和函數

Verilog中signed和$signed()的用法

淺談Verilog和VHDL的區別

如何使用Icarus Verilog+GTKWave來進行verilog文件的編譯和仿真

如何使用Icarus Verilog+GTKWave來進行verilog文件的編譯和仿真

評論