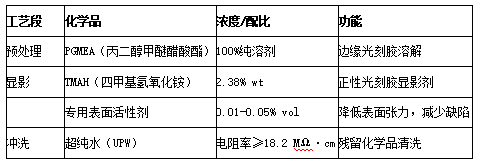

雙重圖形化又稱雙曝光或兩次曝光,其思路是將同一圖形層的數據分成兩次或兩張掩模版分別成像。隨著集成電路制造技術的發展,光刻技術面臨著巨大挑戰,從而對版圖設計的要求也更為嚴格。例如,為了保證圖形轉移的質量,設計規則傾向于將同一層圖形的線條按一個方向排列。盡管如此,當同一方向排列的線條的節距接近 80nm 時,也已達到 193nm 浸沒式光刻機單次曝光的極限;如果節距小于 80nm,在更先進的光刻機被應用于量產前,必須采用雙重或多重圖形化技術。目前,在工業界最常見的雙重圖形化技術有兩種,即自對準雙重圖形化 (Self-Aligned Double Patterning, SADP)技術和光刻-刻蝕-光刻-刻蝕(Litho-Eich-Litho-Etch,LELE)雙重圖形化技術。

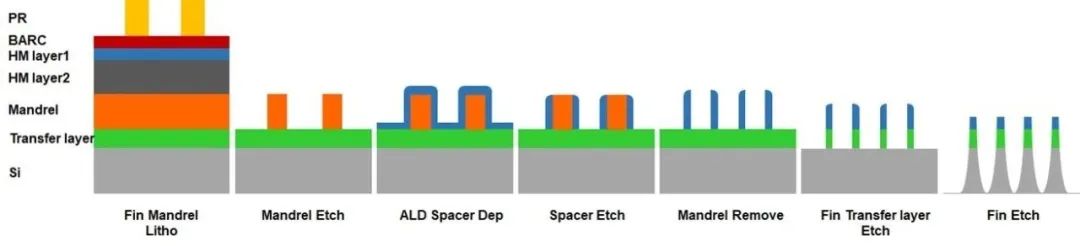

SADP 技術先利用浸沒式光刻機形成節距較大的線條,再利用側墻圖形轉移的方式形成 1/2 節距的線條,這種技術比較適合線條排列規則的圖形層,如 FinFET 工藝中的 Fin 或后段金屬線條。從SADP 技術還可發展出自對準四重圖形化(Self-Aligned Quadruple Patterning, SAQP)技術或自對準多重圖形化(Self-Aligned Multiple Patterning, SAMP)技術。SADP 技術大大降低了對光刻機的要求,而且也不存在套準的問題但增加了對設計圖形的限制;對于復雜分布的小尺寸高密度圖形,則需采用 LELE方式實現雙重圖形化。

LELE 雙重圖形化技術需要先將圖形按一定的算法拆分成兩層并分別制作掩模版,使得每一層圖形都能在光刻能力限制范圍內。常見的 LELE 工藝流程為,首先用第 1 張掩模版曝光并刻蝕,將圖形轉移到硬掩模上;然后用第2張掩模版曝光,利用第2次曝光形成的光刻膠及第1次刻蝕形成的硬掩模作為阻擋進行第 2 次刻蝕,同時將兩層掩模版的圖形轉移到目標圓片上。LELE 雙重圖形化技術根據應用場景的不同,在實施時稍有差別,但無論采用何種方式.關鍵是要保證最終圖形與設計圖形盡可能接近。LELE 方式的技術難點在于圖形的 拆分 與 組合,兩次曝光的套準,以及避免圖形在多次轉移過程中質量變差等。除了上達兩種雙重圖形化技術,還有對同一層曝光兩次,然后刻蝕一次的方式,但是這種方式對光刻膠的要求很高,在業界較少采用。

從嚴格意義上來說,32nm/28nm 節點是采用全部單次曝光技術的最后一代,雖然在柵極光刻中用到端對端切割技術,但也僅被認為是一種準雙重圖形化技術。20~14nm 節點關鍵層均開始采用雙重圖形化,包括 SADP 和LELE。到了 7nm節點,就可能需要采用 SAQP 和LE多次的技術,這種將一層圖形拆分成多層的方式突破了光刻機的極限,但也提高了工藝復雜度,所以對成品率有不利的影響。同時,由于掩模版是集成電路制造中價格最高的工藝材料,光刻機是價格最高的工藝設備,所以雙重或多重圖形化技術明顯增加了制造成本。隨著 EUV 光刻技術的成熟,在7nm/5nm 節點的關鍵圖層極有可能采用 EUV 光刻。

審核編輯 :李倩

-

集成電路

+關注

關注

5452文章

12571瀏覽量

374523 -

光刻機

+關注

關注

31文章

1199瀏覽量

48916

原文標題:雙重圖形化技術(Double Patterning Technology,DPT)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

我們在做一個支持多廠商 MCU 的圖形化配置工具,難點卻不在工具本身

德州儀器TVP7001:視頻與圖形數字化的理想之選

[工具討論] 如果有一款國產圖形化配置工具STM32Cube,支持所有內核和廠商MCU,你會用嗎?

定義光刻精度標準——華林科納顯影濕法設備:納米級圖形化解決方案

RUI Builder 圖形化UI設計工具

突破傳統桎梏,PPEC Workbench 開啟電源智能化設計新路徑

PPEC電源DIY套件:圖形化算法編程,解鎖電力電子底層算法實踐

微雙重驅動的新型直線電機研究

自對準雙重圖案化技術的優勢與步驟

PPEC新品發布丨圖形化編程數字電源專用 ARM Cortex-M4 MCU

可視化組態物聯網平臺是什么

一場圖形化編程與樹莓派的“跨界聯姻”?

雙重圖形化技術(Double Patterning Technology,DPT)

雙重圖形化技術(Double Patterning Technology,DPT)

評論