當今的自主和人工智能 (AI) 軍事系統(tǒng)處理的傳感器數(shù)據(jù)量不斷增加。為了處理這種極端的工作負載,系統(tǒng)架構師必須使用最快的 FPGA [現(xiàn)場可編程門陣列] 器件和英特爾多核處理器來設計電路板。如果沒有用于駐留數(shù)據(jù)和實時執(zhí)行的大量高速雙數(shù)據(jù)速率第四代 (DDR4) 存儲器,這些器件就無法提供峰值性能。

面對龐大的數(shù)據(jù)問題,架構師必須設計他們的系統(tǒng),以滿足更小、更敏捷的平臺的尺寸、重量和功率 (SWaP) 限制,這些平臺對于我們的作戰(zhàn)人員任務成功至關重要。為了支持系統(tǒng)要求,系統(tǒng)中的每個嵌入式板可能需要每個處理器至少 64 GB 的內(nèi)存,相當于超過 128 個獨立的商業(yè)級內(nèi)存設備或多個雙列直插式內(nèi)存模塊 (DIMM) 用于在印刷電路板上進行布局。

對于在惡劣的前沿部署環(huán)境中運行的超緊湊型軍事系統(tǒng)內(nèi)部的嵌入式板來說,這不是一個可行的解決方案。必須使用采用芯片堆疊技術的高密度軍用級存儲器來節(jié)省空間和功耗,同時在惡劣環(huán)境中保持可靠性。

問題堆積如山

芯片堆疊和引線鍵合的復雜性隨著設計高密度存儲器(例如單個 16 GB DDR4 設備)所需的每個額外芯片而增加。由于如此多的電路采用緊密堆疊的配置,信號完整性是設計考慮的首要因素。在本討論中,信號完整性受損的兩個主要組成部分是串擾和回波損耗性能。

串擾是由于強互感和互電容引起的不需要的電壓噪聲耦合。更簡單地說,它是芯片組中相鄰電路中的信號傳輸對一個電路中的信號造成的干擾。

回波損耗是由信號反射回其原點而不是傳遞到最終終端的部分引起的信號失真。它是由傳輸線中的阻抗不匹配或不連續(xù)引起的。

這些性能問題限制了堆疊存儲設備中的數(shù)據(jù)速度,包括整體系統(tǒng)性能和可靠性。在關鍵任務軍事應用中,它們還可能導致災難性事件。

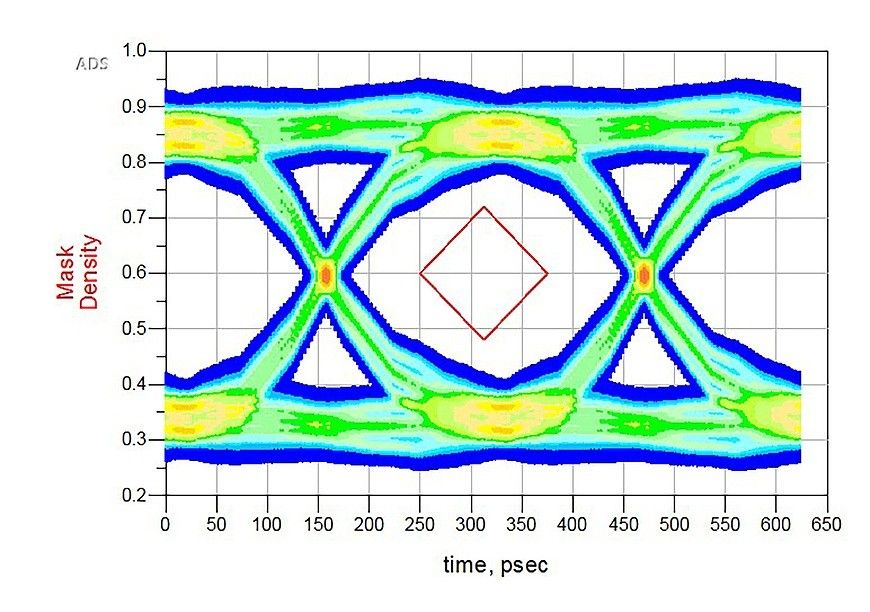

傳統(tǒng)的芯片堆疊設計拓撲有其局限性

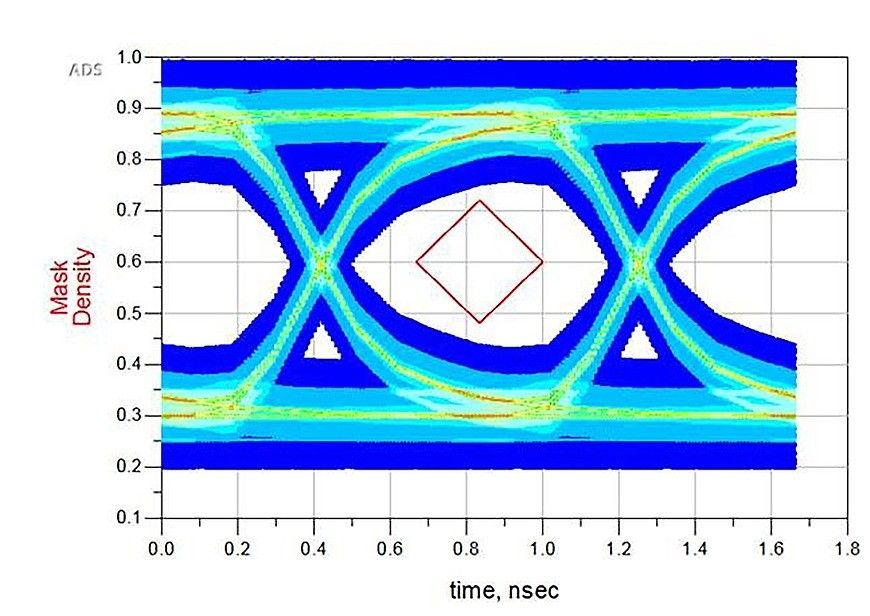

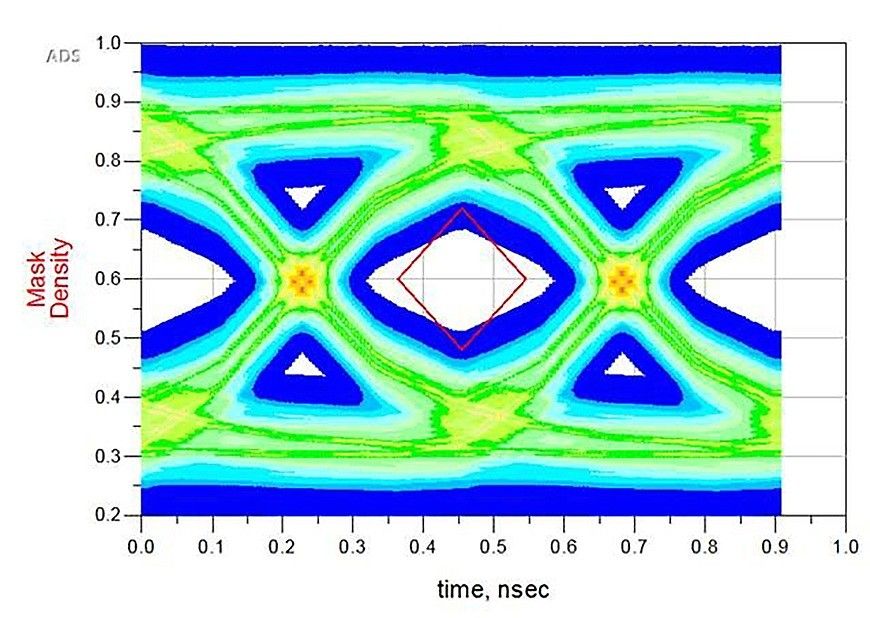

傳統(tǒng)的多芯片堆疊設計方法使用分支或星形拓撲。對于 DDR2 和 DDR3 設備來說,這是一種有效的設計方法,因為它可以實現(xiàn)這些代設備可以提供所需的數(shù)據(jù)速率和密度。(圖 1。巧妙設計的堆疊式DDR4設備可以通過這種方法實現(xiàn)。然而,高容量存在固有的限制,因為增加的終端路徑或總線長度會導致信號失真,并且由于反射而限制了傳輸線的最大帶寬。隨著堆疊芯片數(shù)量的增加,這些芯片繼續(xù)退化到有害點。分支拓撲達到其最大能力,因此排除了在高密度、高速 DDR4 和 DDR5 設備中使用的方法。(圖 2 和圖 3。信號完整性工程師必須尋找替代設計方法,以實現(xiàn)下一代更小、更靈活的軍事系統(tǒng)。

圖 2:使用分支拓撲的 2400 Mbps DDR4。

圖 3:使用分支拓撲的 4400 Mbps DDR5。

實現(xiàn)了高密度DDR4

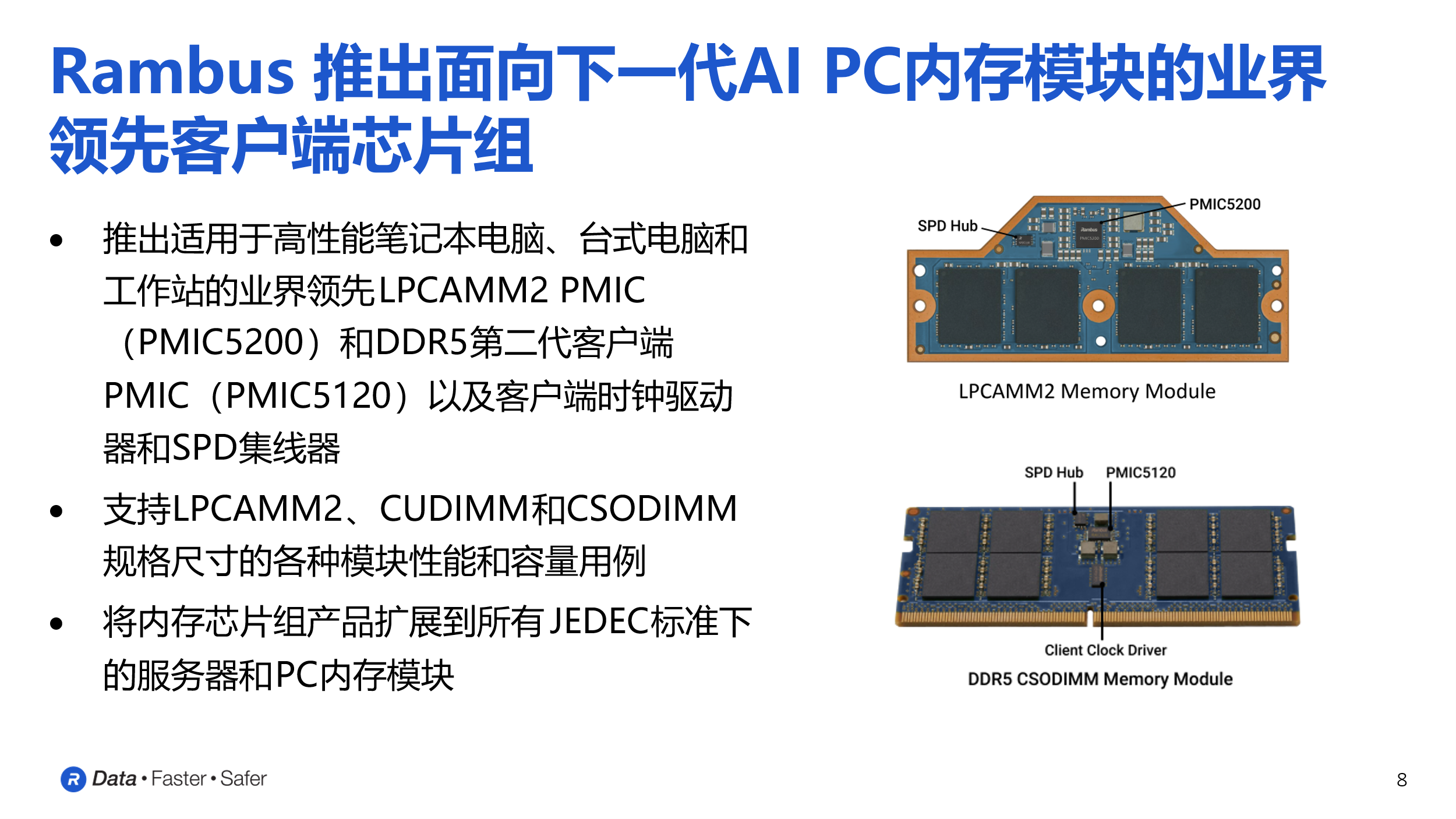

為了達到DDR4的高速要求,信號完整性工程師面臨兩個主要挑戰(zhàn):首先,減少串擾,這在使用非橫向電磁(TEM)導管(如再分布層(RDL)和鍵合線)的設計中尤為突出;其次,滿足最低-12 dB的回波損耗性能。

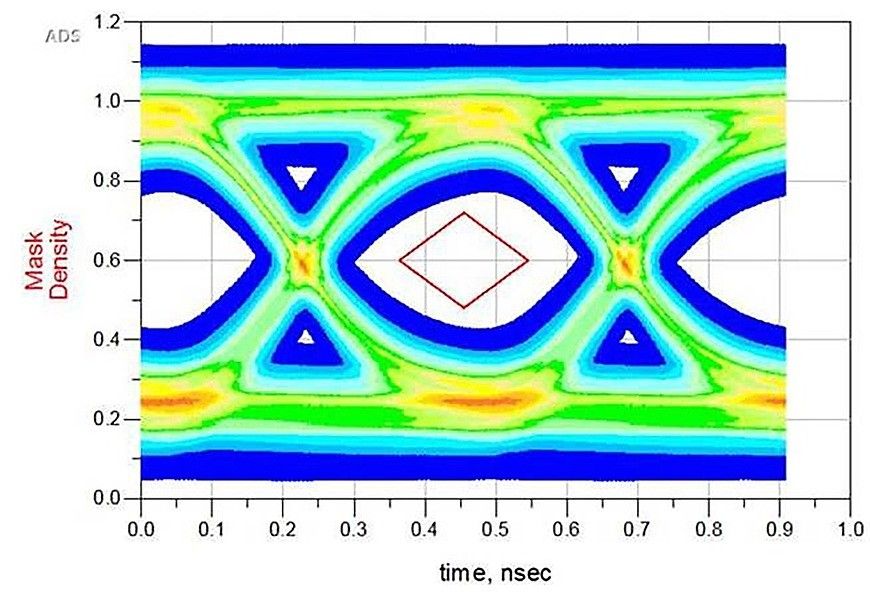

需要通過支持比分支拓撲更高頻率操作的共面拓撲來增強互連層。這縮短了兩個終端之間的路徑,同時消除了短截線,從而改善了信號完整性和時序。為了實現(xiàn)這一點,將信號從一個芯片按順序路由到下一個芯片,消除了與以前在分支設計中看到的短截線或額外走線相關的反射。通過添加微帶傳輸線來創(chuàng)建連續(xù)的信號返回路徑和線性總線路徑,可實現(xiàn)高速數(shù)據(jù)速率。此外,對信號和信號返回走線寬度的考慮進一步提高了數(shù)據(jù)速率并改善了回波損耗。

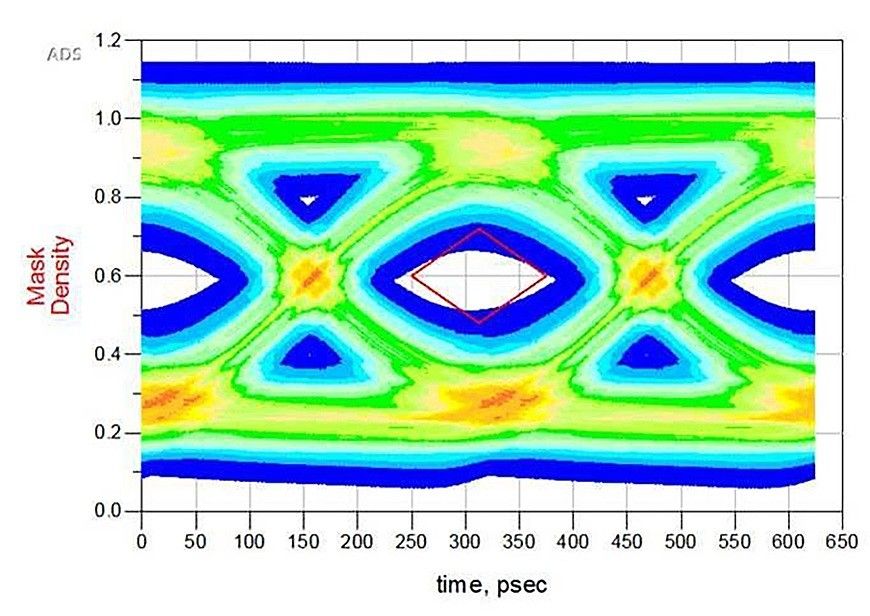

利用這種拓撲結構,通過帶串擾的精細平衡實現(xiàn)-16 dB的回波損耗,可以在單個緊湊封裝中實現(xiàn)18個存儲設備的小型化,同時在軍用溫度范圍內(nèi)提供2666 Mbps的數(shù)據(jù)速率。然而,雖然使用這種方法優(yōu)化了回波損耗,但仍需要改進串擾性能以滿足DDR5數(shù)據(jù)速度。(圖 4 和圖 5。

圖 4:使用高級共面拓撲的 4400 Mbps DDR5

圖 5:使用高級共面拓撲的 6400 Mbps DDR5。

通往軍用級 DDR5 的道路

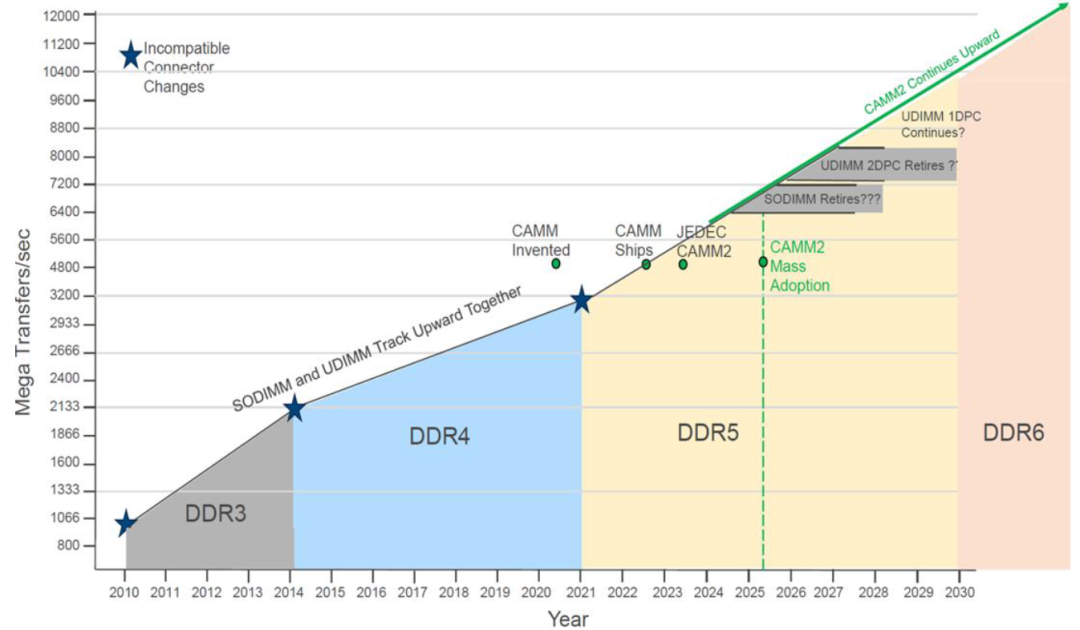

隨著DDR4的預期帶寬和密度增加一倍,以及功率和通道效率的提高,先進的軍事系統(tǒng)將使用DDR5設備來提高性能。然而,即使之前引入的高密度多芯片封裝的共面拓撲結構取得了進步,DDR5 的更高數(shù)據(jù)速度仍然無法實現(xiàn)。需要進一步改進串擾性能和芯片間網(wǎng)絡。開發(fā)應用于RDL的獨特多平面接地和信號走線布局可提高串擾隔離,從而將性能提高6dB。目前,沒有其他已知的芯片堆疊設計方法可用于在數(shù)據(jù)速率高達 6400 Mbps 的單一器件中實現(xiàn)高密度 DDR5 的商業(yè)化(圖 6)。

圖 6:6400 Mbps DDR5 使用高級多平面拓撲。

下一代軍事嵌入式系統(tǒng)的設計人員和用戶將很快實現(xiàn)其高速多核處理系統(tǒng)的最大性能,因為集成了高容量、高速堆疊DDR5,同時受益于更小的系統(tǒng)占用空間。

審核編輯:郭婷

-

傳感器

+關注

關注

2576文章

55041瀏覽量

791339 -

存儲器

+關注

關注

39文章

7739瀏覽量

171676 -

人工智能

+關注

關注

1817文章

50098瀏覽量

265386

發(fā)布評論請先 登錄

DDR4價格瘋漲!現(xiàn)貨市場狂飆!

深度解析:DDR4、DDR5 與 LPDDR6 內(nèi)存的驗證要點與挑戰(zhàn)

NV34C04:適用于DDR4 DIMM的4-Kb EEPROM串行SPD芯片

存儲市場現(xiàn)罕見倒掛:DDR4價格漲幅十倍于DDR5漲價潮持續(xù)蔓延

Amphenol ICC DDR5 SO - DIMM連接器:高速高密度的理想之選

華邦電子推出先進 16nm 制程 8Gb DDR4 DRAM 專為工業(yè)與嵌入式應用而生

DDR5 設計指南(一):DDR5 VS LPDDR5

三星正式啟動DDR4模組停產(chǎn)倒計時,PC廠商加速轉(zhuǎn)向DDR5,供應鏈掀搶貨潮

漲價!部分DDR4與DDR5價差已達一倍!

DDR內(nèi)存市場現(xiàn)狀和未來發(fā)展

上海貝嶺推出全新DDR5 SPD芯片BL5118

看點:三星DDR4內(nèi)存漲價20% 華為與優(yōu)必選全面合作具身智能

DDR4漲價20%,DDR5上調(diào)5%!

大型文件秒開、多開任務流暢——DDR5的優(yōu)勢遠不止頻率

堆疊式高速DDR4和DDR5內(nèi)存適用于惡劣的戰(zhàn)斗環(huán)境

堆疊式高速DDR4和DDR5內(nèi)存適用于惡劣的戰(zhàn)斗環(huán)境

評論