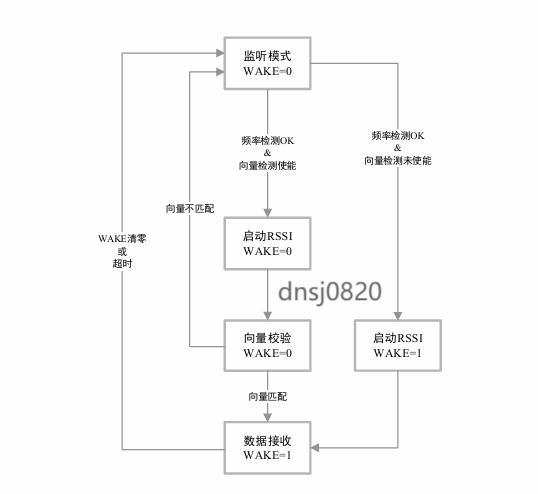

SI3933 的時鐘生成器可以是晶體振蕩器(R1<0>=1)、內部 RC 振蕩器(R1<0>=0)或外部時鐘源 (R1<0>=1)。晶體振蕩器具有較高的頻率精度和較高的電流消耗,并且需要三個外部元件(晶體和 兩個電容器)。RC 振蕩器是完全集成的,可以校準以提高其頻率精度。假如外部已有一個數字時鐘, 可以通過引腳 XOUT 直接使用它(此時 XIN 連接到 VCC)。 無論選擇哪種時鐘生成器,時鐘生成器的頻率必須根據載波頻率來設置。

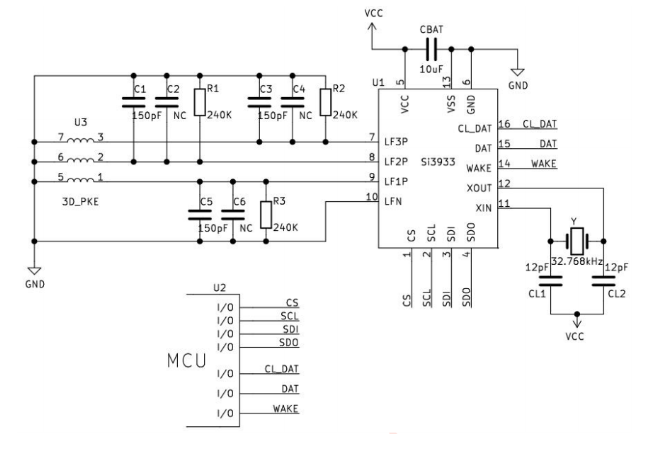

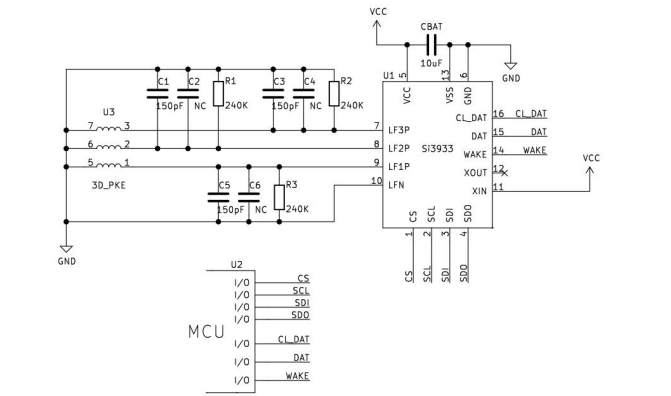

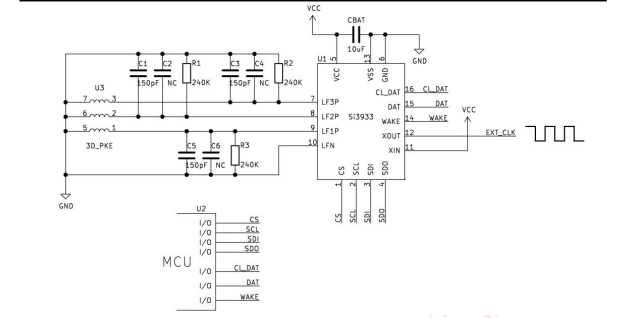

典型應用原理圖:

1.采用晶振的典型應用原理圖

2.采用 RC 振蕩器的典型應用原理圖

3.采用外部時鐘源的典型應用原理圖

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

原理圖

+關注

關注

1353文章

6427瀏覽量

246279 -

時鐘芯片

+關注

關注

2文章

296瀏覽量

42102

發布評論請先 登錄

相關推薦

熱點推薦

恩智浦MFRC522與SI522的性能功耗對比

生成器,簡化客戶開發環節,提供天線部分免費調試服務。

Si522 主要優勢點:

1. 直接PIN2PIN 兼容RC522,與FM17550/FM17520/RM5222. 完全替換RC522,接收

發表于 02-28 16:43

如何通過地址生成器實現神經網絡特征圖的padding?

,從而使卷積輸出特征圖結果滿足我們的需求,這種補零的操作稱之為padding,如下圖所示。

關于padding的實現,一般有兩種操作,第一種是使用稀疏地址生成器,尋找padding數據地址的規律,當

發表于 10-22 08:15

?CDCDLP223 時鐘合成器技術文檔總結

CDCDLP223是一款基于PLL的高性能時鐘合成器,針對DLP?系統進行了優化。它使用20 MHz晶體生成基頻,并導出100 MHz HCLK和300 MHz HCLK輸出的頻率。此外,該CDCDLP223在20 MHz輸出端

CDCE913 可編程1PLL VCXO時鐘合成器技術手冊

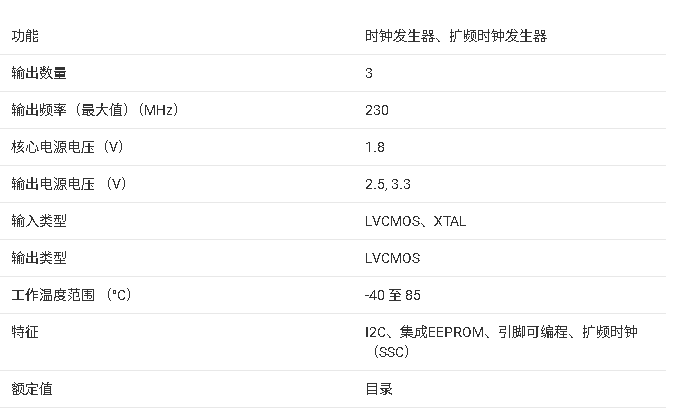

CDCE913和CDCEL913器件是基于PLL的模塊化、低成本、高性能、可編程時鐘合成器。這些器件從單個輸入頻率產生多達三個輸出時鐘。每個輸出都可以使用集成的可配置PLL在系統內針對

CDCE937 可編程 3-PLL VCXO 時鐘合成器技術手冊

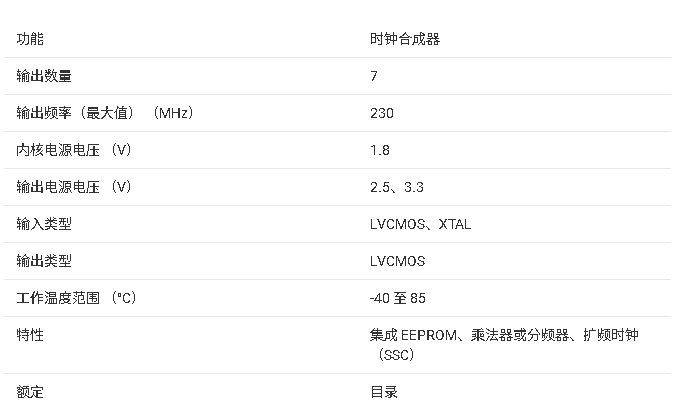

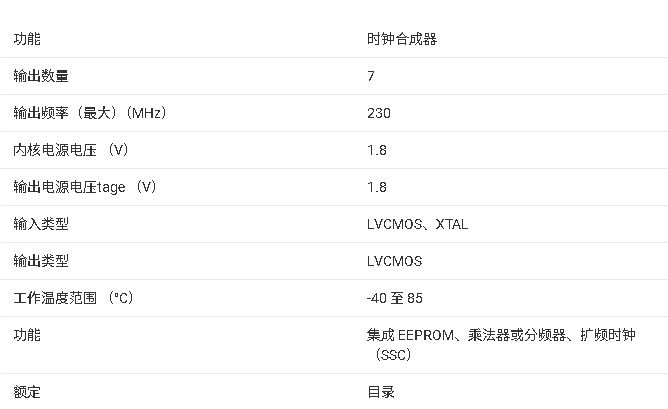

CDCE937和CDCEL937器件是基于模塊化PLL的低成本、高性能、可編程時鐘合成器、乘法器和分頻器。這些器件從單個輸入頻率生成多達 7 個輸出

?CDCE937/CDCEL937 時鐘發生器技術文檔總結

CDCE937和CDCEL937器件是基于模塊化PLL的低成本、高性能、可編程時鐘合成器、乘法器和分頻器。這些器件從單個輸入頻率生成多達 7 個輸出

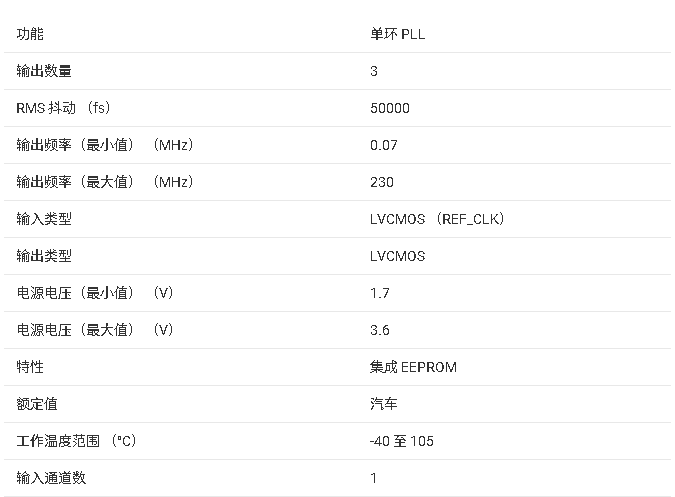

?CDCE813-Q1 可編程時鐘合成器與抖動清除器技術文檔總結

CDCE813-Q1器件是一款基于鎖相環(PLL)的模塊化、低成本、高性能、可編程時鐘合成器。它們從單個輸入頻率生成多達三個輸出時鐘。每個輸

非對稱密鑰生成和轉換規格詳解

|PRIMES_49+

RSA81925RSA8192|PRIMES_59+使用密鑰參數生成

從API版本10開始支持,使用密鑰參數生成RSA密鑰。

RSA密鑰參數,涉及三個整數,包括:

n:模數

發表于 09-01 07:50

PanDao:實際約束條件下成像系統的初始結構的生成

選定了三種差異比較顯著的設計(見圖2)。

圖2. (a)與(b)參考設計實例;(c)-(e)基于同等規格與約束條件,由FTR初始透鏡生成器生成的放大視圖系統

經PanDao分析,所有

發表于 05-07 08:57

125K SI3933與AS3933技術問題總匯

);(3) 距離比其他系列芯片更長,可達 5m 左右。4.之前用的是 BLE 方案,距離不夠穩定,SI3933 能符合 PKE 的產品嗎?穩定性怎么樣?符合。穩定性很好,經過市場檢驗的產品。

發表于 04-30 10:04

“Quantum Origin”成首個獲NIST驗證的軟件量子隨機數生成器

-Quantinuum的“Quantum Origin”成為首個通過NIST驗證的軟件量子隨機數生成器 Quantum Origin獲得NIST SP 800-90B對其驗證熵源的批準 增強了聯邦

EB Tresos狀態顯示無法運行生成器是什么原因導致的?

我正在嘗試集成 MCAL 包,但在生成過程中收到如下驗證錯誤:“無法為模塊”Dio_TS_T40D2M20I0R0“運行生成器

發表于 04-02 08:06

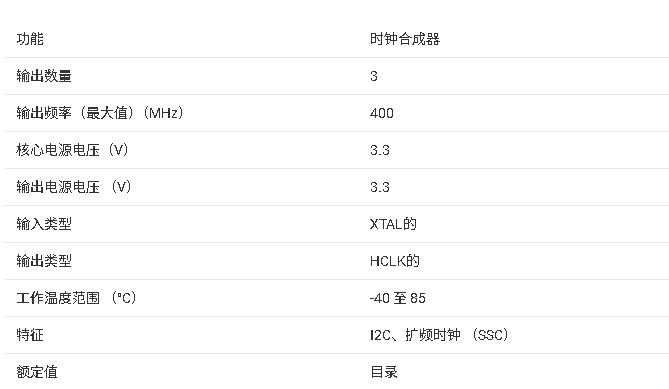

SI3933 三個時鐘生成器的典型應用原理圖

SI3933 三個時鐘生成器的典型應用原理圖

評論