系統級封裝 (SiP) 正迅速成為越來越多應用和市場的首選封裝選項,引發了圍繞新材料、方法和工藝的狂熱活動。

SiP是將多種功能集成到單個基板上的重要封裝平臺,可通過更短的互連實現更低的系統成本、設計靈活性和卓越的電氣性能。SiP 出現在 5G、物聯網、移動、消費者、電信和汽車應用程序中。其中,最大、或許也是最令人興奮的細分市場是消費者和可穿戴設備——從智能耳塞到電容器疼痛貼片——纖薄、舒適的設備,可快速提供人們想要的健康和健身數據。

在許多方面,SiP 和其他類型的先進封裝實現了曾經幾乎完全與摩爾定律相關的性能和成本優勢。“通過我們的扇出組合、倒裝芯片、BGA 和嵌入式解決方案,ASE 與臺積電一起努力工作,以擴展摩爾定律標準,我們希望將性能翻倍——也許不是成本的一半,但成本效益,”日月光銷售和營銷高級副總裁Yin Chang說。“這就是我們引入 VIP 平臺以提供解決方案工具箱的原因,為架構師提供最高級別的靈活性來創建差異化系統。”

其他人同意先進封裝在提高系統性能方面發揮著關鍵作用。“歸根結底,系統級性能才是最重要的,” Lam Research旗下 Coventor總裁 David Fried 說。“我們仍在努力克服功率、性能、功率、面積和成本 (PPAC) 障礙。只要市場不斷要求我們提供額外的計算能力和內存,我們只是在推動不同的參數以不斷提高系統級性能。”

封裝類型選擇通常歸結為平衡性能和成本。Yole Intelligence 的技術和市場分析師 Stefan Chitoraga 表示:“倒裝芯片主導了 RF AiP 毫米波市場,但存在開發扇出 AiP(封裝天線)的趨勢。“與倒裝芯片相比,扇出的優勢包括更小的外形尺寸、利用高密度 RDL 和細間距。盡管如此,扇出仍然過于昂貴,并且需要克服技術挑戰。”

這些挑戰包括模具移位和翹曲,各種工具和工藝修改正在解決這些問題。

為了在單個 SiP 中實現高性能、高效率和低成本,工程師們正在將新的成型材料、雙面 SiP、激光輔助鍵合 (LAB) 和下一代柔性基板用于扇出、倒裝芯片和嵌入式 SiP。

3D的 SiP

SiP 是行業 3D 革命的一部分。除了以更精細的間距容納更多 I/O 的趨勢外,還有許多其他努力將更多內容塞進封裝而不是單個芯片。這包括扇出中的多個重新分布層、橋接器和中介層以將不同的裸片連接在一起、雙面封裝以增加密度,以及嵌入式裸片選項以在更小的外形中實現更快的裸片到裸片處理,從而消耗更少的功率。

今天的 SiP 結合了各種組件,從 GPU 和 RF IC 到存儲器、傳感器、無源器件等等。“例如,ASE 的 SiP 技術支持集成不同的微控制器、ASIC、天線和傳感器,從而控制連續血糖監測儀 (CGM) 中的所有功能,”ASE 企業研發副總裁 CP Hung 表示。

Hung 還描述了將四方扁平無引線 (QFN) 封裝中的多個傳感器重新設計為具有硅通孔的晶圓級芯片級封裝 (WL-CSP),這可以提高 80% 的電氣性能,同時減少其足跡減少了 30%。Hung 表示,SiP 也有生物識別應用,包括用于測試血液的微流體通道的體外診斷、基于 SiP 的助聽器以及用于傳感器集線器的晶圓級 SiP,其占地面積比傳統封裝小 77%。

SiP 還動搖了供應鏈和成本結構。“你每天都會在手機上看到這一點。它們變得更薄、更輕,同時執行更多功能,但這要求封裝與這些設計保持同步,這意味著保持信號完整性、管理熱問題、減少干擾等,” QP高級工藝工程師 Sam Sadri 說技術。“但哪里有挑戰,哪里就有解決方案。使用倒裝芯片時,您在進行芯片貼裝時會嘗試從底部散發熱量,因此您在接口處使用散熱器和導熱硅脂。我見過帶有管道和冷卻液的 3D 基板。”

除了評估 SiP 中的所有流程和配置選項外,Sadri 還強調了對系統中 IP 保護的日益關注。

Yole 分析師估計,到 2025 年,SiP 市場將以 5% 的復合年增長率增長至 170 億美元,高于 2020 年的 138 億美元。市場領導者是 ASE、索尼、Amkor、JCET 和臺積電。大約 85% 的市場是移動和消費產品,其次是電信和基礎設施,然后是汽車封裝。

此外,SiP I/O 間距預計將從今天的 90-350μm 收窄到 2025 年的 80-90μm。使用銅柱的嵌入式硅橋,或使用 TSV 和微凸塊的硅中介層,”Chitoraga 說。

SiP 包含多種組裝方法,包括倒裝芯片和引線鍵合 SiP(收入和單位最大),其次是扇出 WLP,然后是嵌入式芯片封裝。Yole Intelligence 的技術和市場分析師 Gabriela Pereira 表示:“SiP 讓系統設計人員能夠靈活地混合和匹配 IC 技術、優化每個功能塊的性能并降低成本。”“完全集成的 SiP 解決方案使設計人員能夠以最少的設計工作將藍牙或攝像頭模塊等附加功能實現到系統中。”

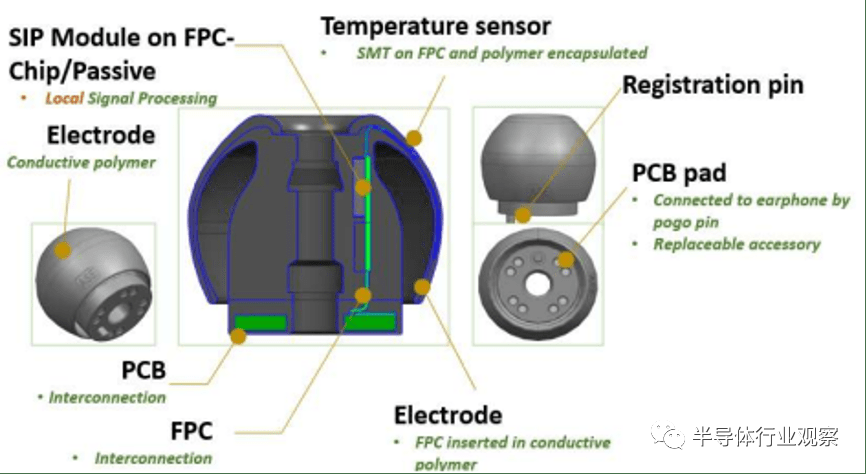

能夠測量體溫和拍攝心電圖 (ECG) 的原型無線耳塞是 ASE 及其客戶之一正在開發的可穿戴設備的最新示例(見圖 2)。ASE 的 Kueihao Tseng 及其同事強調了這樣一個事實,即工作電子、封裝和測試框架位于耳塞外部附近,通過圓形 PCB 中的彈簧針連接。這種方法提高了信號完整性并實現了組件更換。工程師優化了成型工藝和金屬聚合物材料以實現低電阻 (<0.05Ωm),同時保持柔韌性以確保舒適貼合。

圖 2:柔性基板上的 3D SiP 模塊將導電電極連接到溫度傳感器,再連接到 SiP 模塊,再到智能耳塞中的圓形 PCB。

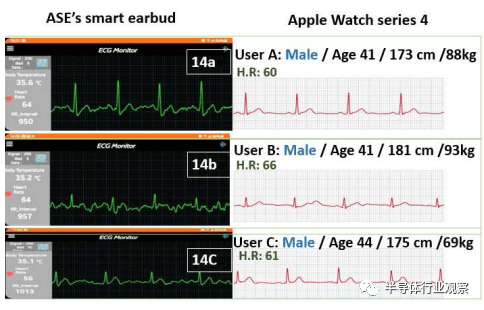

在柔性印刷電路上,信號處理 IC 和無源元件將 mV 級生物反饋信號轉換為數字信號。耳塞使用熱敏電阻測量溫度,它比 IR LED 便宜。通過流程修改,ECG 波形能夠與 Apple Watch 基準測試相匹配(見圖 3)。

圖 3:使用原型耳塞的心電圖結果與 Apple Watch 基準相關。

不斷發展的工藝

將裸片凸塊連接到基板焊盤有幾種主要選擇。其中:

大規模回流是最成熟和最便宜的。

熱壓鍵合 (TCB) 使用力和熱量,并且與低 k 電介質兼容,但它是一種較低吞吐量的工藝。

激光輔助鍵合 (LAB) 在比 TCB 更短的過程中提供局部加熱。

“對于小芯片應用,激光輔助鍵合效果非常好,只要芯片尺寸不太大,”ASE 的 Chang 說。“對于更大的芯片,熱壓鍵合可在大面積上提供均勻的加熱和壓力。”

LAB 由 Amkor 工程師于 2014 年開發,自 2018 年以來一直用于裝配線,用于倒裝芯片封裝。Amkor 目前正在開發下一代 LAB 技術,該技術特別針對與高性能封裝中的熱界面材料 (TIM) 的互連。

“最近,對細間距倒裝芯片凸塊和大/薄基板封裝的需求增加,由于其良好的質量和高生產率,引起了業界對 LAB 的興趣,” Amkor Technology Korea董事 SeokHo Na 表示。TIM 有助于在倒裝芯片 BGA 中使用金等導電界面將熱量從管芯散發到蓋子。但是具有金表面的硅芯片往往會反射大部分指向它的激光,從而導致傳統 LAB 的非濕式故障。

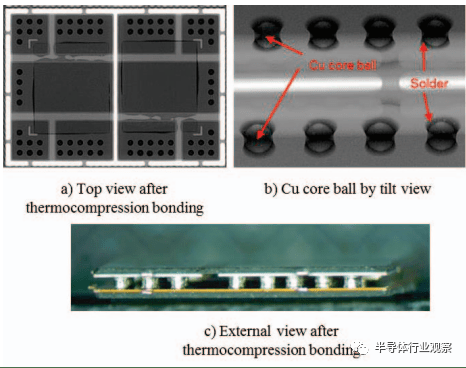

先進的 LAB 工藝將激光引導至封裝背面,穿過工具的載物臺真空塊。工程師調整了工藝條件,包括功率和曝光時間,以使用 SnAg 尖端形成更可靠的銅柱凸塊。Amkor 指出,與大規模回流焊相比,LAB 不太可能產生焊料側壁蠕變(芯吸),并且與大規模回流焊相關,并且可以適應更精細的凸點間距。其他架構,例如 2.5D 和 3D HBM(在 EMC 中),也可能會利用 LAB。“下一代 LAB 可能是帶有背面金屬 (TIM) 裸片的細間距凸塊器件的唯一解決方案,”Na 總結道。

嵌入式 SiP

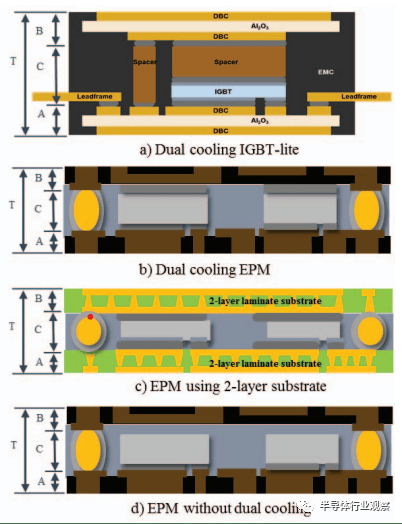

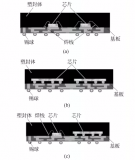

嵌入式 SiP 是一個快速發展的市場。在最近開發的 3D 嵌入式功率 SiP 中,模塑料 (EMC) 是最受關注的問題。該平臺的一個特點是圍繞夾在基板之間的功率 FET 的 EMC 填充工藝。EMC 必須滿足楊氏模量(拉伸)和玻璃化轉變溫度(流動)的特定參數,以最大限度地減少封裝翹曲——這在功率晶體管中尤其重要,因為它們無法獲得摩爾定律縮放的好處。翹曲是使用 Ansys 的全有限元模型軟件模擬的。

圖 4:通過使用優化的熱壓結合和成型材料從層壓基板切換到基于引線框架的工藝,使用單面冷卻的更緊湊的嵌入式 SiP 成為可能。

Amkor Technology Korea 高級總監 Byron Jin Kim 和他的團隊使用 ICEPAK 軟件比較了嵌入式 SiP 與雙冷卻 IGBT 在具有三個嵌入式結構的直接鍵合陶瓷上覆銅基板上的散熱結果(見圖 4)。選擇 (d) 的嵌入式工藝在底部基板上使用芯片連接,并且只需要單面冷卻。該團隊確定基于引線框架的工藝模塊表現出優于層壓基板設計的熱性能。此外,核心球的位置也很重要。

“銅芯球通過助焊劑印刷-球放置-回流工藝在頂部基板上進行。這種方法是在工藝參數設置中控制適當焊料潤濕的關鍵,”報告稱。展望未來,Amkor 預計會為類似系統提供各種嵌入式 SiP 選項,包括具有半橋和全橋應用的電源電路。

圖 5:熱壓鍵合工藝顯示芯片和銅球放置 (a),銅芯球潤濕顯示角度 (b) 的可布線微引線框架,以及成型前封裝的側視圖 (c)。

封裝天線

對于 5G 和 6G,天線技術具有挑戰性。天線的相控陣取代了單個天線,因為在毫米波和太赫茲 (THz) 頻率下,從半導體封裝到天線的長路徑會導致高損耗。這使得需要將這些天線集成到 SiP 中。

“在 2018 年之前,LGA SiP 被用于射頻行業,但由于雙面封裝的發展,BGA 已被廣泛采用,”Yole 的 Pereira 說。“博通、Qorvo 和 Skyworks 等廠商通過 DSBGA 和 DS-MBGA(雙面模壓 BGA)等解決方案實施逐步創新,而村田直接實施 DS-MBGA 以實現系統集成和小型化。臺積電的集成扇出型封裝天線 (InFO_AiP) 是另一個等待使用的創新解決方案,但由于成本效率低下而被推遲。”

除了不同的封裝類型外,用于高頻用途的基板也在發生變化。傳統PCB材料由于介電損耗和吸水率高,無法滿足5G太赫茲頻率的需求。業界目前正在評估各種液晶聚合物 (LCP) 基板的電性能、氣密性和材料靈活性。

“我們一直在努力尋找信號強度和信號損失之間的平衡點,就 5G 而言,我們正在研究許多不同的材料集、不同的 LCP 集成,”Chang 說。“希望這種最小損耗解決方案能夠簡化整體 AiP 設計。”

結論

封裝公司和代工廠正在尋求各種 SiP 以滿足移動消費、通信和基礎設施以及汽車應用之間的不同需求。為了降低成本和提高制造可靠性,正在為倒裝芯片、扇出和嵌入式 SiP 添加新材料和工藝。但是與保持信號完整性、更快地傳輸更多數據以及克服工具/基板限制相關的移動目標將繼續鼓勵下一代創新。

審核編輯:郭婷

-

SiP

+關注

關注

5文章

540瀏覽量

107721 -

物聯網

+關注

關注

2945文章

47819瀏覽量

414863 -

sip封裝

+關注

關注

4文章

69瀏覽量

16014

原文標題:SiP封裝,越來越受歡迎

文章出處:【微信號:晶揚電子,微信公眾號:晶揚電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

存儲芯片SiP封裝量產,PCB密度要求翻3倍,國內產能缺口達30%

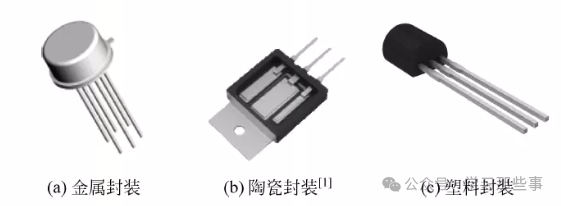

半導體封裝介紹

系統級封裝技術解析

SiP 封裝與錫膏等焊料協同進化之路?

harmony-utils之PreferencesUtil,首選項工具類

芯片傳統封裝形式介紹

harmony OS NEXT-通過用戶首選項實現數據持久化

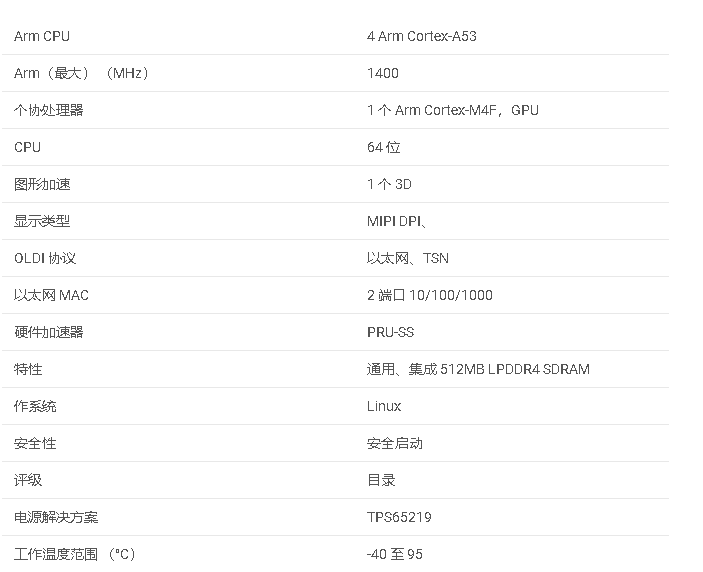

AM625SIP 通用系統級封裝,采用 Arm? Cortex-A53? 和集成 LPDDR4數據手冊

3D封裝與系統級封裝的背景體系解析介紹

SiP封裝成為更多應用和市場的首選封裝選項

SiP封裝成為更多應用和市場的首選封裝選項

評論