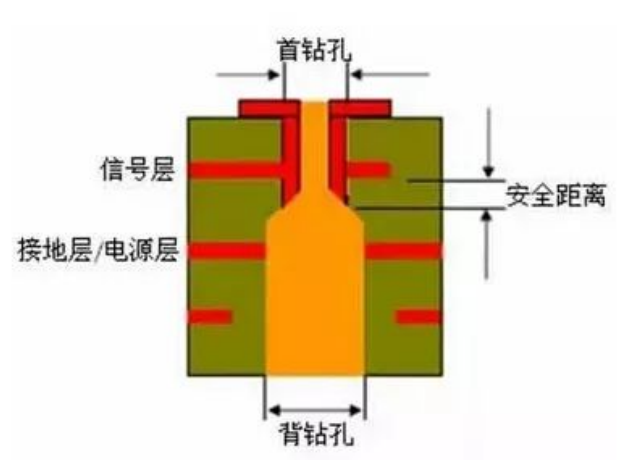

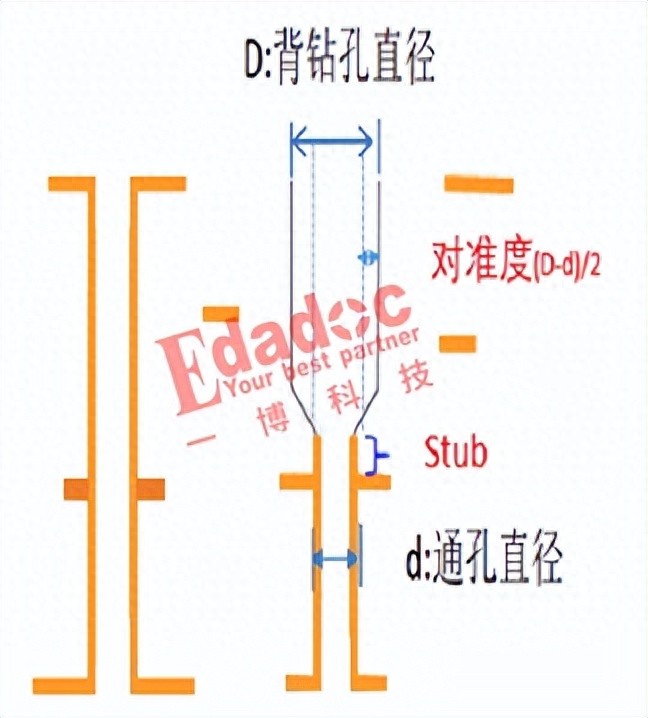

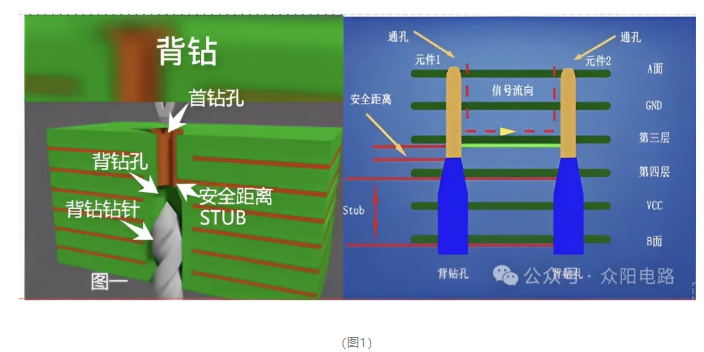

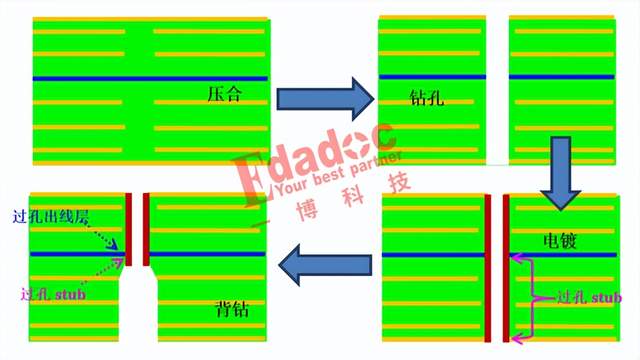

背鉆其實就是控深鉆比較特殊的一種,在多層板的制作中,例如12層板的制作,我們需要將第1層連到第9層,通常我們鉆出通孔(一次鉆),然后陳銅。這樣第1層直接連到第12層,實際我們只需要第1層連到第9層,第10到第12層由于沒有線路相連,像一個柱子,如圖1所示。

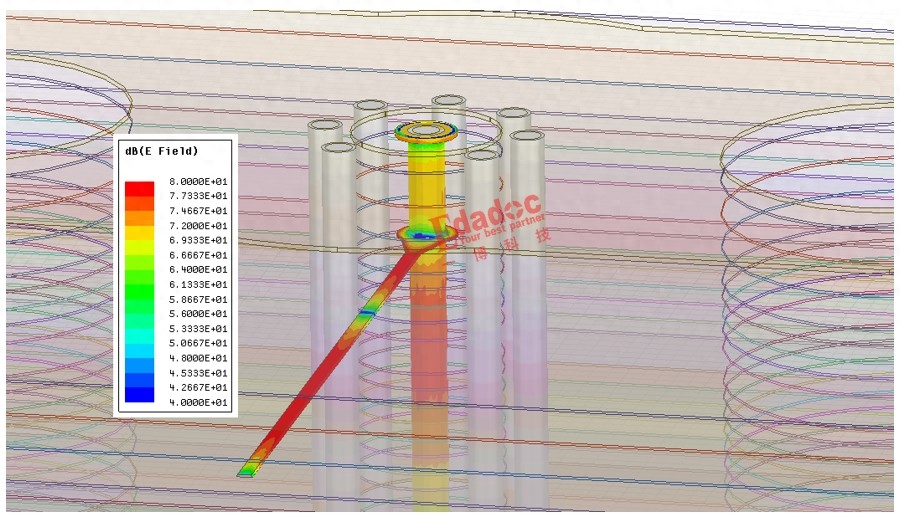

這個柱子影響信號的通路,在通訊信號會引起信號完整性問題。所以將這個多余的柱子(業內叫STUB)從反面鉆掉(二次鉆)。所以叫背鉆,但是一般也不會鉆那么干凈,因為后續工序會電解掉一點銅,且鉆尖本身也是尖的。所以PCB廠家會留下一小點,這個留下的STUB的長度叫B值,一般在50-150UM范圍為好。

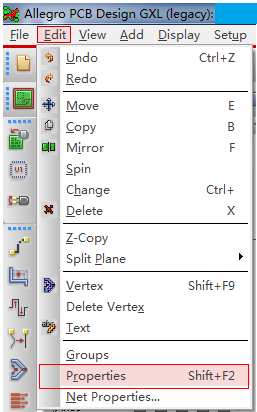

1、執行菜單命令,選擇Edit->Properties,激活屬性命令,如圖2所示。

▲圖1 背鉆孔示意圖

▲圖2 背鉆孔示意圖

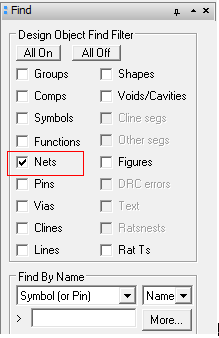

2、在激活“property edit”的命令狀態下,find面板中只勾選nets對象。

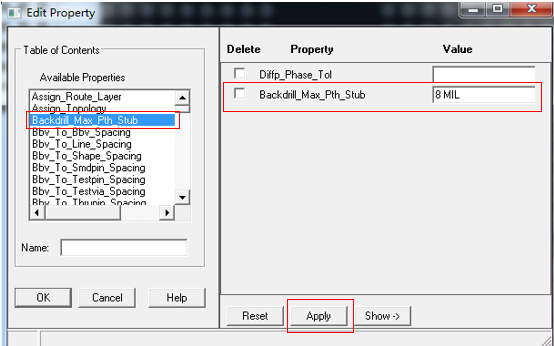

3.然后選擇要背鉆的網絡,隨即會自動彈出“Edit Properties”對話框,左邊的選項欄中選擇“Backdrill_max_pth_stub”選項增加背鉆屬性,背鉆Stub值可以填8,但是工廠加工能力可能達不到,此Stub值意義不大,隨后點擊”Apply”

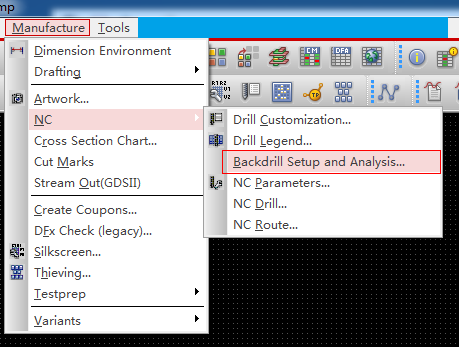

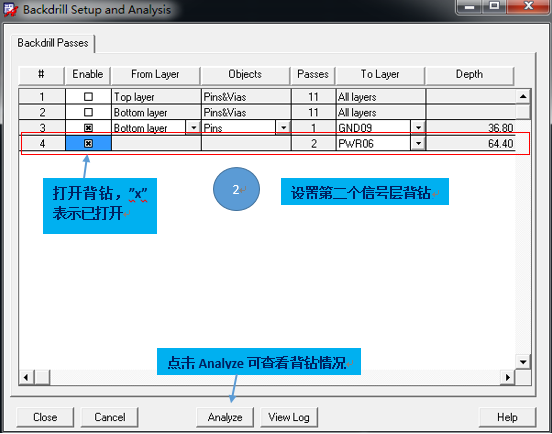

4.選擇Manufacture->NC->Bacdrill Setup and Analysis…進入背鉆層設置

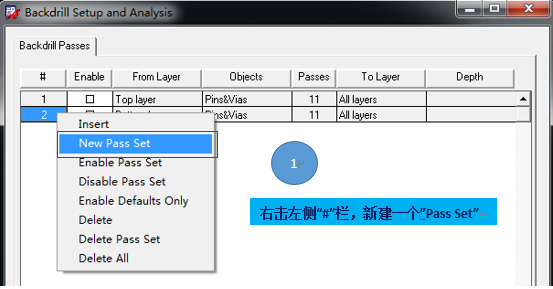

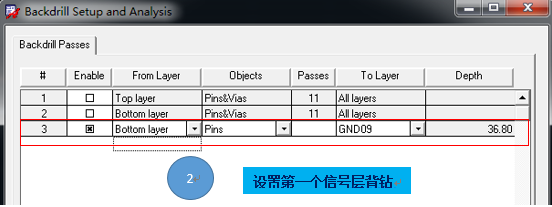

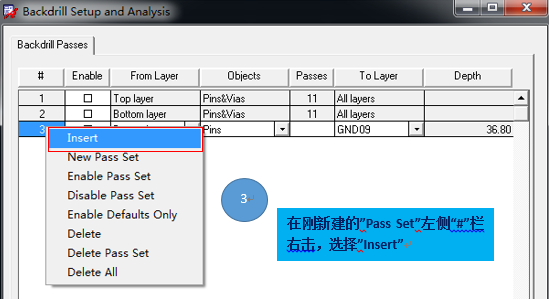

5.設置需要背鉆的層,如需要背鉆的信號分布在Layer5、Layer8,背鉆從Botom->Top方向背鉆,將要鉆掉的層設置分別設置為Bottom->Layer6、Bottom->Layer9,設置如下。

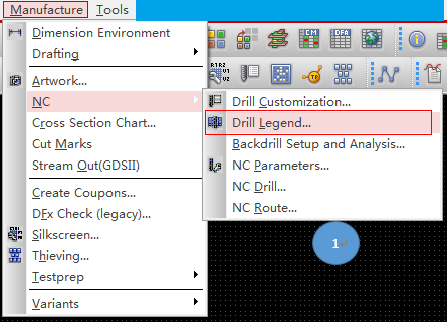

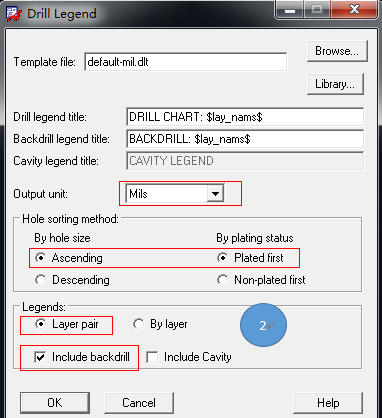

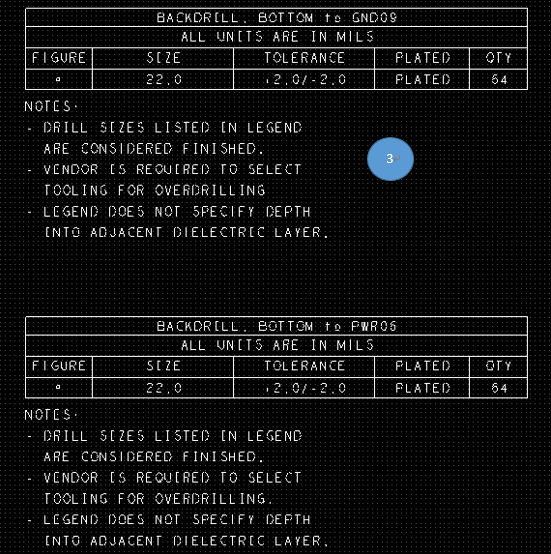

6、選擇Manufacture->NC->Drill Legend輸出背鉆符號

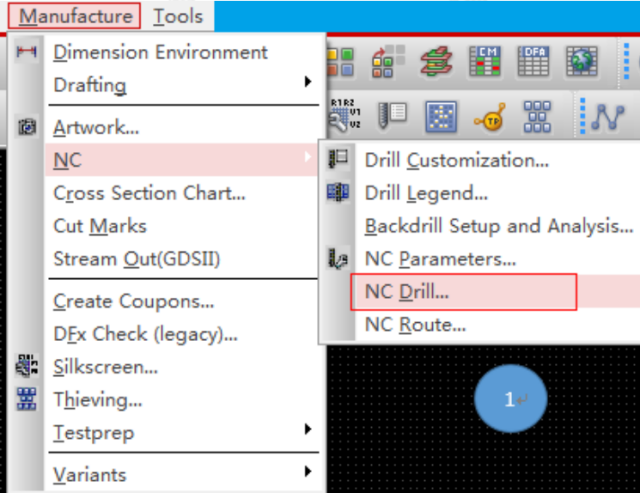

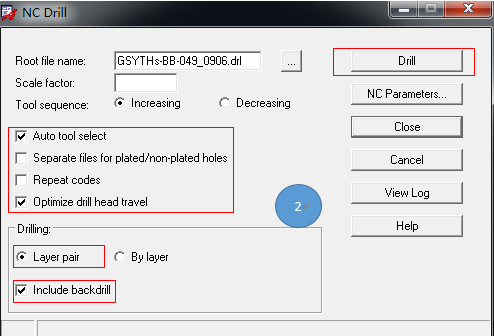

7.選擇Manufacture->NC Drill輸出鉆孔文件

審核編輯 :李倩

-

pcb

+關注

關注

4404文章

23877瀏覽量

424231 -

電解

+關注

關注

1文章

83瀏覽量

18346 -

allegro

+關注

關注

42文章

767瀏覽量

150131

原文標題:Cadence Allegro背鉆設置詳細介紹教程

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

KiCad 10 探秘(三):引入三大全新導入器:Allegro、PADS 與 gEDA

PCB 背鉆塞孔翻車記!綠油凸起竟讓焊接 “手牽手” 短路

2025 Cadence 中國技術巡回研討會即將開啟 ——系統設計與分析專場研討會(上海站)

高速PCB板DDR5數據信號的長STUB要背鉆嗎?

PCB為啥現在行業越來越流行“淺背鉆”了?

毫米之間定成敗:PCB背鉆深度設計與生產如何精準把控

毫米之間定成敗:PCB背鉆深度設計與生產如何精準把控

別讓孔偏毀了信號!PCB 背鉆的 XY 精準度如何做到分毫不差?

別讓孔偏毀了信號!PCB 背鉆的 XY 精準度如何做到分毫不差?

眾陽電路背鉆工藝技術簡介

Cadence SPB OrCAD Allegro22.1安裝包

Cadence SPB OrCAD Allegro24.1安裝包

信號完整性的守護者:背鉆技術

Cadence Allegro背鉆設置詳細介紹教程

Cadence Allegro背鉆設置詳細介紹教程

評論