本文主要講解在 PL 中從 IP 核到 PS 之間需要完成含超 16 次中斷的布線的情況下,該如何使用 AXI Interrupt Controller (INTC)。其中使用的AMD Xilinx外設包括 Vivado 設計中的 GPIO、IIC、UART 以及定時器。

設計示例是使用 Vivado 2020.1 版本,以 ZCU106 評估板為目標而創建的。中斷在 PetaLinux 2020.1 上經過測試,此處隨附了設計 Tcl 和 system-user.dtsi 文件。

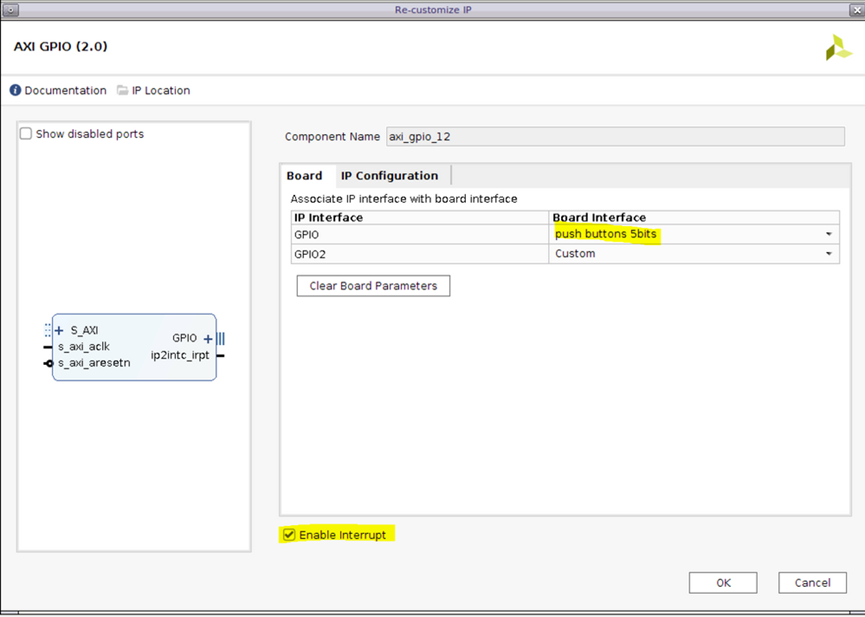

AXI GPIO:

General Purpose Input/output (GPIO) 核是支持輕松訪問器件內部屬性的接口。該核還可用于控制外部器件的行為。

中斷:

中斷控制可從 GPIO 通道獲取中斷狀態,并向主機生成中斷。在 Vivado 中設置“Enable Interrupt”(啟用中斷)選項后,即可啟用中斷控制。

對于輸入模式,gpio_input 管腳連接到 ZCU106 的如下按鈕 (PUSH BUTTON):

gpio_input(0) = GPIO_SW15

gpio_input(1) = GPIO_SW14

gpio_input(2) = GPIO_SW16

gpio_input(3) = GPIO_SW17

gpio_input(3) = GPIO_SW18

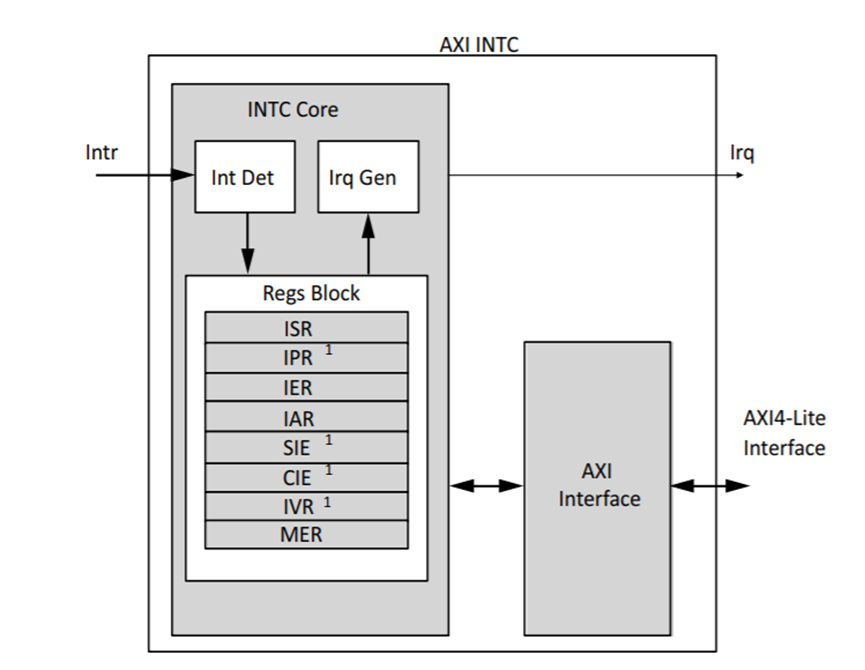

AXI INTC:

AXI Interrupt Controller (INTC) 核可將來自外設器件的多個中斷輸入集中到系統處理器的單一中斷輸出。使用寄存器來檢查、啟用和確認中斷。

此示例的主要目的是將超過 16 個中斷連接到 PS。AXI INTC 核可支持我們滿足此需求。使用單一 AXI INTC 塊的情況下最多可連接 32 個中斷,并且您還可使用級聯。(我們可能會通過另一篇博文來提供此操作示例。)

在下文描述 Concat IP 的多個圖例中,您可以看到中斷的連接方式。

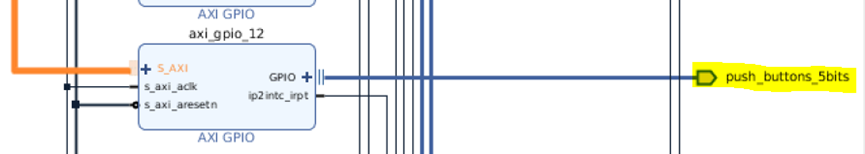

塊設計:

由于設計太大了,我并沒有添加完整設計的示意圖,因此下面會逐一展示必要的連接示意圖。

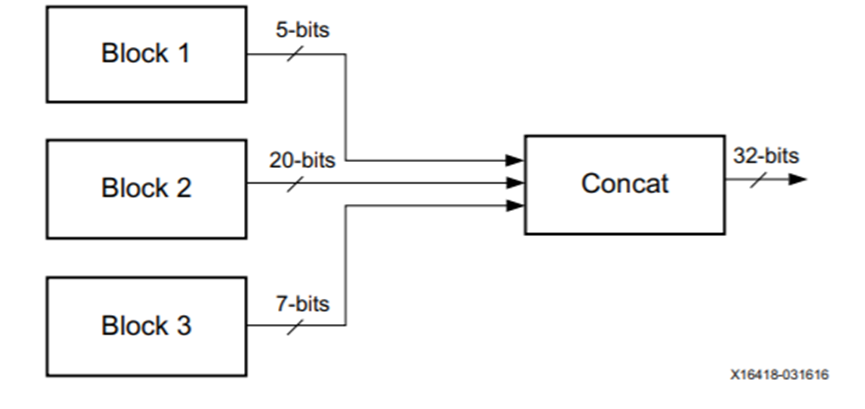

Concat IP:

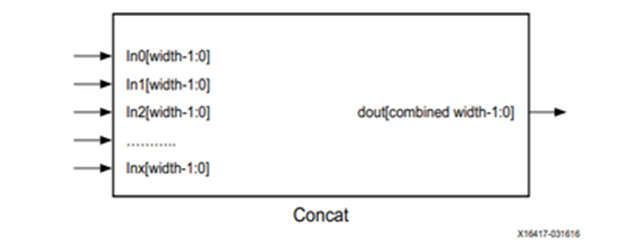

Concat IP 核可提供相應機制來將不同寬度的總線信號組合到單一總線內。

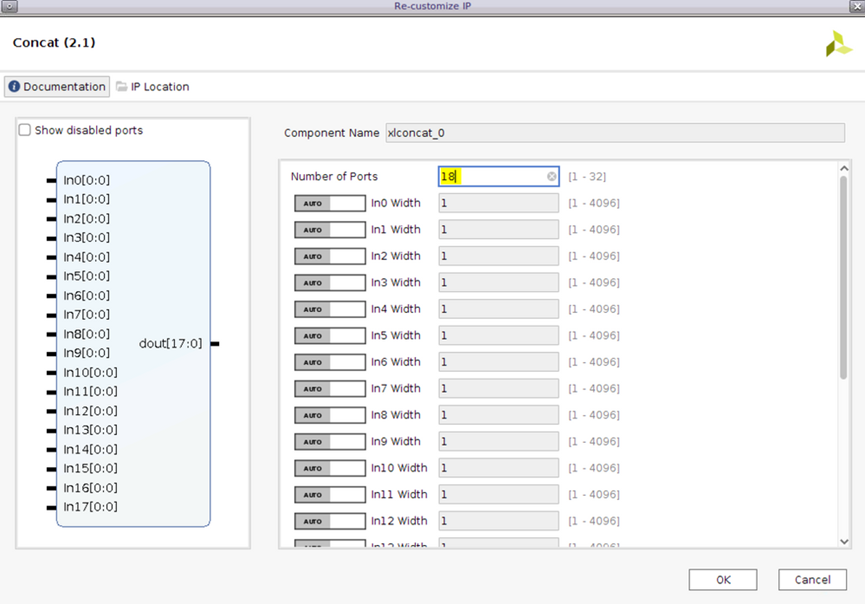

從 IP catalog(IP 目錄)添加 Concat 塊,然后雙擊 IP(如下所示)以打開“Re-customize IP”(重新自定義 IP)對話框。

將“Number of Ports”(端口數)參數設置為期望的輸入端口數。在此示例中,所選數量為 18。

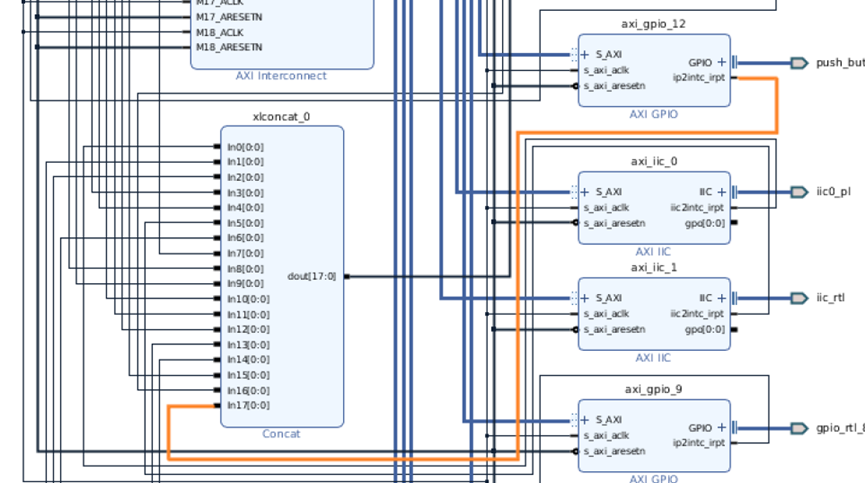

完成自定義 IP 后,結果如下所示,第 18 個端口連接到如前文所述的 GPIO_PUSH_BUTTONS 中斷行。

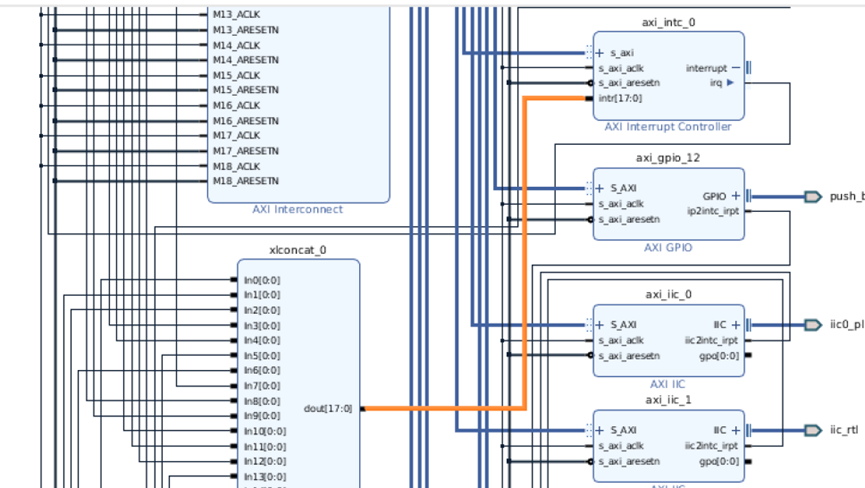

dout 為輸出端口,其位寬等于所有輸入端口的位寬總和,該輸出端口布線到 AXI INTC 核的輸入 intr 端口。

AXI INTC 的輸出連接到 Zynq MPSoC 塊的 pl_ps_irq_0 端口:

請驗證設計并遵循其余步驟進行操作以生成比特流。導出硬件,用于構建 PetaLinux 鏡像。

PetaLinux:

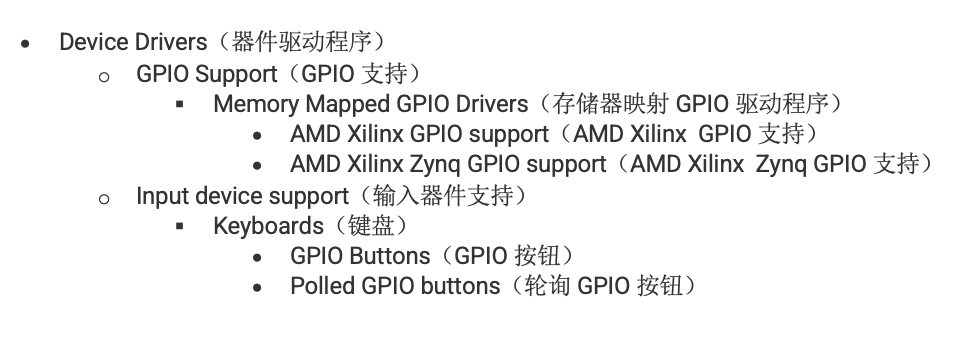

內核配置:

在 menuconfig 中啟用以下選項。默認情況下,這些選項均已啟用,但您應核實其狀態,以防萬一。

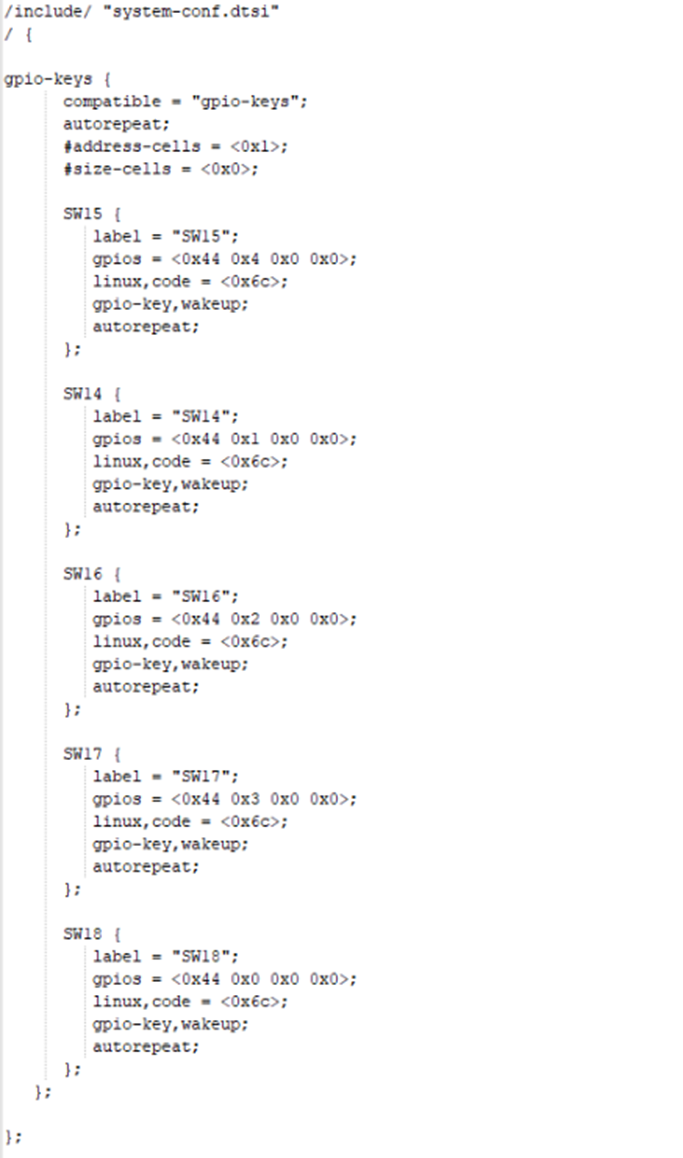

向設備樹添加按鈕:

按鈕僅可用于 Input GPIO 應用。

創建的每個子節點均可控制 GPIO 的單個位。在 dts 文件中的“gpio-keys”鍵節點下,根據設計,為按鈕 (Push Buttons) 創建含如下名稱的子節點:

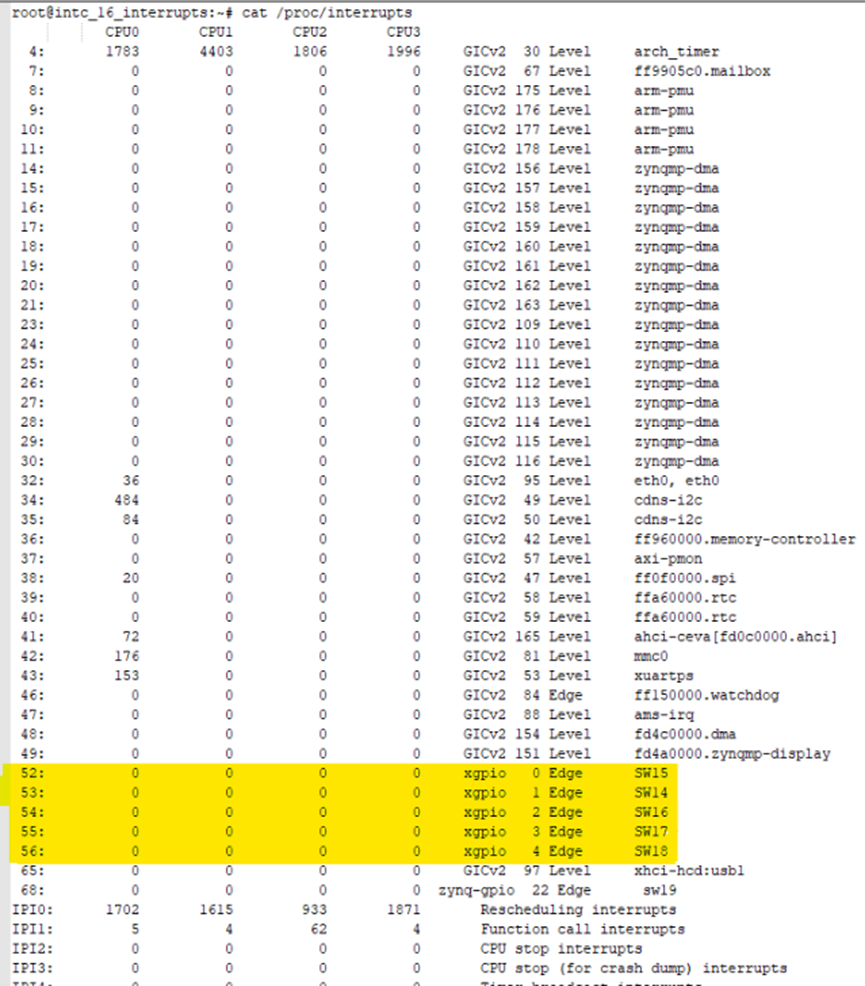

完成此操作后,請啟動 Linux。您可在 cat /proc/interrupts 中看到按鈕 SW15 到 SW18 的標簽。

隨機按下按鈕后,觸發器計數會按如下所示方式增加:

-

接口

+關注

關注

33文章

9520瀏覽量

157032 -

Xilinx

+關注

關注

73文章

2200瀏覽量

131139 -

定時器

+關注

關注

23文章

3368瀏覽量

123626

原文標題:開發者分享|如何使用 AXI Interrupt Controller 處理超過 16 次中斷

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

AMD Versal自適應SoC上的級聯模式示例

S5PV210中斷配置詳解

S5PV210中斷配置

STM32外部中斷簡介

單片機C51中interrupt和using應該如何使用詳細方法說明

關于MPSoC的中斷處理介紹

C51 interrupt 中斷

STM32 中斷原理及外部中斷的實現

STM32中斷與DMA通信編程

STM32中斷與DMA通信編程

STM32中斷與DMA通信編程

AMD Xilinx AXI Interrupt Controller中斷優先級

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

如何使用 AXI Interrupt Controller完成含超16次中斷的布線

如何使用 AXI Interrupt Controller完成含超16次中斷的布線

評論