下一代芯片會什么樣子,什么時候能實現?

芯片制造商正在為架構、材料和基本結構(如晶體管和互連器件)的根本性變革做好準備。最終結果將是有更多的流程步驟、每個步驟的復雜性增加,以及全面成本上升。

在前沿,FinFET會在3nm節點之后的某個地方前進困難。仍在這些節點工作的三家代工廠 ——臺積電,三星和英特爾,以及行業研究機構 imec正在尋求某種形式的柵極全能晶體管作為下一個晶體管結構 ,以便對柵極泄漏進行更嚴格的控制。

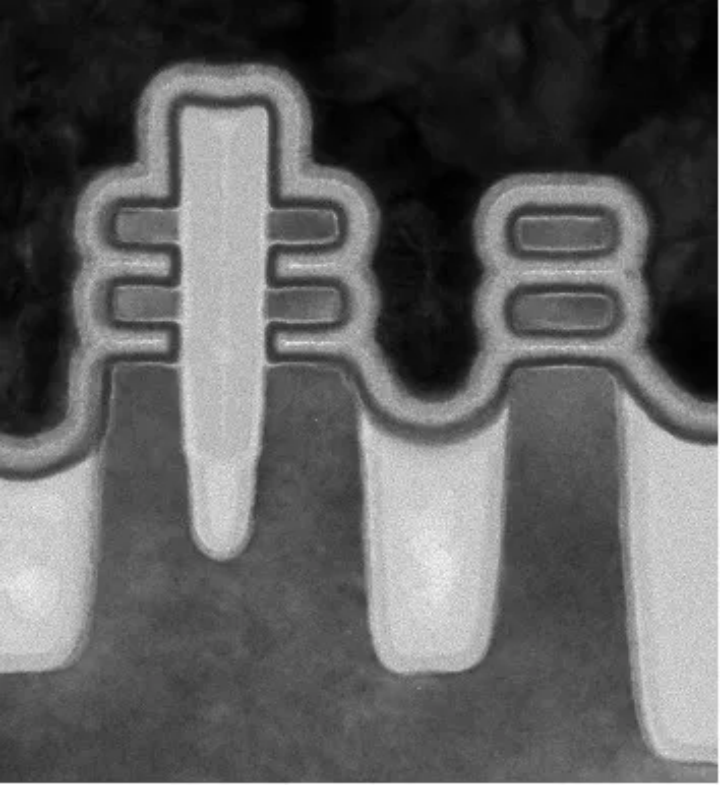

在此之后,這種方法可能至少適用于更多的節點,并可能隨著由imec開發的中間步驟forksheet FET的推出而進一步發揮作用。(見圖1)然而每家公司都在使用不同的命名,時間表和技術組合,因此很難確定哪個公司在什么時候處于技術領先地位。

圖1:N型和P型 forksheet FET對(左)

和nanosheet FET(右)。來源:imec

“回顧過去,我們從雙極器件開始,然后我們轉向平面CMOS和3D FinFET,”臺積電業務發展高級副總裁Kevin Zhang說。“現在我們正在轉向nanosheet柵極全能晶體管。但晶體管結構將會演變。不是每一代或每一個節點都需要引入新的架構,因為新的晶體管或架構需要很長很長的時間。我們已經投資nanosheet技術超過10年,以便有足夠的信心在2nm節點上引入它。”

代工廠將盡可能長時間地擴展現有技術 ,因為每次更換升級都是昂貴的。除了代工廠開發的新制造工藝外,還需要微調涉及制造設備的數百個工藝步驟。這里的關鍵指標是制造每個晶圓所花費的時間,這會影響成本,以及獲得足夠良率的時間。每個步驟都需要更改所有內容,從EDA工具(需要在每個節點和每個鑄造廠的半節點進行認證)到各種設備何時插入制造環流。復雜芯片可以有多個插入點。這使得實際的時間表難以確定,代工廠可能不會推到下一個技術節點,直到他們使用現有技術進行改進。

臺積電是目前流程的領導者,也是唯一處于領先地位的純代工廠,計劃遷移到2nm的GAA FET。臺積電研發高級副總裁Yuh-jier Mii在最近的一次演講中表示,3nm的finFET在使用相同的功率時將速度提高18%,或在相同的性能下降低34%的功率。使用nanosheet,速度將提高約10%至15%,功耗降低25%至30%,密度增加1.1倍。他還指出,現有的設計規則將在N2兼容,這將降低IP的重用率。

英特爾將遵循類似的路徑,使用其版本的GAA FET,稱為帶狀FET。英特爾同樣表示,它的finFET技術還有足夠的改進,可以將finFET擴展到另一個節點。

“我們在當前的生產節點上提供先進的 finFET ,”英特爾副總裁兼產品和設計生態系統支持總經理Rahul Goyal說。“我們還在研究下一代節點,它將在明年左右推出。然后,我們的sweet spot——這是最先進的節點,我們相信我們可以在這里實現差異化,目前正在與幾個客戶一起開發。這讓我們更好的規定好了2024年至2025年的發展歷程,并更好地了解了客戶的需求以及如何實現這一目標。挑戰在于如何確保我們在早期階段與客戶合作,以盡可能加快我們的學習速度,然后使我們的生態系統和合作伙伴能夠為我們的客戶服務。”

與此同時,三星將在3nm引入GAA技術,稱為多橋通道FET。該公司聲稱,與5nm FinFET相比,該技術可以將功耗降低45%,將性能提高23%,并將面積減少16%。下一代產品將降低高達50%的功耗,并將性能提高30%,占地面積減少35%。三星吹捧的關鍵改進之一是可調節的通道寬度,它可以降低驅動信號所需的功率。

下一步是什么?

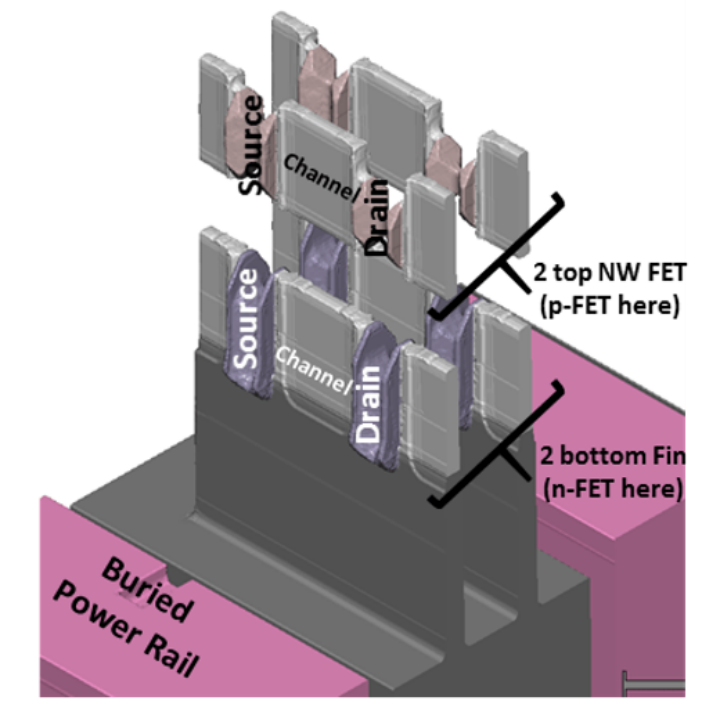

在GAA FET之后,下一個技術版本可能包括堆疊的GAA FET,也稱為complementary FET(CFET),可擴展高達50%。這種變化至少將nanosheet擴展了幾個節點。可以堆疊多少層可能決定了這項技術的可擴展性。

“我們正在研究橫向nanosheet以及未來幾代技術中橫向nanosheet某種程度的堆疊,” Lam Research計算產品副總裁David Fried說。“每個人都喜歡調查先進設備的完整列表,并查看垂直和橫向設備和堆棧,但是進行任何這些更改所需的投資都非常巨大,以至于制造商必須確信,在他們進行過渡之前,他們將從重大過渡中獲得至少幾個節點。你盡量不要一次一個節點地做出這些決定。”

預計CFET將開始出現在1.4nm左右。CFET已經在繪圖板上存在了十多年,被認為是nanosheet和forksheet FET的進化步驟 。對于CFET,nFET和pFET導線采用單線或雙線配置,在提供面積和密度優勢的同時,仍可限制柵極處的電流泄漏。這種泄漏就是即使設備關閉,電池也會耗盡或電力繼續流動的原因。

圖 2:CFET 架構。來源:科文托,

Lam Research旗下研究公司

重新思考一些基礎知識

與過去不同,當一個過程可以在數十億個相同設計的單元上完成時,最終用戶需要針對特定應用的更定制的解決方案。在某些情況下,這些是為內部消費而設計的,例如超大規模數據中心。這限制了特定設計的行業體量,并進一步減少了量。

更糟糕的是,其中一些設備正被用于安全和任務關鍵型應用。因此,除了數量有限之外,還需要在更長的使用壽命內提高可靠性。

為此,正在制定一些有趣的戰略來處理這些問題和相關問題。例如,與其期望設計中的每個晶體管或互連都能以100%的良率完美地工作, 不如期望能夠在芯片生命周期的任何時候識別出哪些是壞的。這里的重點是彈性。過去,這是通過冗余實現的,一般的態度是晶體管是免費的。但是,在異構設計中,這種方法太昂貴了,其中一些計算元素和內存是由不同的供應商創建的。

“有兩個問題,”PDF Solutions首席技術官 Andrzej Strojwas說。“首先,你如何很早就確定電路不起作用?其次,如何構建可重配置的互連?可以使用有源電路來重新配置該互連。這樣做的標準方法是在制造過程結束后進行測試,然后燒毀保險絲。但是,如果通過低級金屬水平的電子束掃描將信息內聯在內,則可以更有效地做到這一點。粒度是不同的。”

當索尼在2000年推出基于IBM的Cell處理器的Playstation 2時,它被設計成六個內核,盡管只需要五個。這種方法在當時被認為是革命性的。但是,可重構性增加了對從設計到制造的應用的能力,包括實時分析,根據需要重新路由信號的能力,以及更精確地劃分設計的能力。

光刻也即將經歷一個重大而昂貴的轉變。EUV在經過大約十年的延遲后,部署用于5nm的大批量生產,已經落后了。在3nm和2nm處,除非ASML(尖端光刻設備的唯一來源)能夠以合理的價格推出高數值孔徑EUV(HIGH NA EUV),否則將再次需要多圖案化。HIGH NA EUV的光圈為0.55,而EUV為0.33,它使用變形透鏡,能夠在晶片邊緣正確打印特征。但并非所有金屬層都需要HIGH NA EUV,這意味著它可能會作為一種點工具而不是一刀切地集成到制造流程中。

另一個正在獲得挑戰的策略是設計技術協同優化,它將前端設計與制造聯系起來,比過去更緊密地聯系在一起。DTCO已經存在多年,但它只在最先進的節點上使用。

“在平面CMOS時代,設計師和技術可以預測節點將如何擴展,”Synopsys硅工程集團的產品營銷總監Ricardo Borges說 。“隨著finFET的引入,這種預測變得不那么可信,FinFET在混合中引入了一些新事物,使得預測節點的特性變得更加困難。今天,有更多種類和更多的架構需要探索。例如,在短期內,我們看到gate全能技術的早期發布。除此之外,還有幾種類型的器件,更多的晶體管架構,更多的材料和系統需要評估。在某些時候,可以用其他材料代替硅。我們已經看到了新的金屬,如釕和鉬用于未來的互連,以及用于未來互連的鉍和銻,因為它們的電阻率較低。然后有一些結構,imec稱之為縮放助推器,這可能是一種新的過程技術,以減少圖案化方法的可變性。”

然而,另一種方法是根本不擴展到最先進的節點。聯華電子(UMC)和GlobalFoundries等代工廠正在進行大量投資,這些工廠正在使用替代方法來提高PPA。GlobalFoundries技術、工程和質量高級副總裁Gregg Bartlett表示,目前使用的芯片中有80%是在成熟節點上制造的,他預計隨著先進封裝、混合鍵合、小芯片和更多領域特定設計的增長,這一數字還會增加。

不過,這并沒有使成熟節點的設計變得不那么復雜。“我們從材料開始,然后設計芯片,而不是從 終端市場開始,弄清楚他們想用設計做什么,以及什么材料映射到其中,”Bartlett說。“SOITEC有27種不同類型的SOI(絕緣體上的硅)材料,具有不同的盒子厚度,不同的硅厚度和不同的晶體取向。了解為什么一種基板比另一種基材更好是一個非常重要的考慮因素。這并不是因為材料特性。這是因為當它完全集成到系統級別的性能中時,效果就是不同的。”

不同的選擇

令人驚訝的是,在所有工藝節點上都發生了多少研發,而不僅僅是在前沿,而且隨著美國芯片與科學法案和歐洲芯片法案的通過,這項研究可能會爆炸式增長,這些法案將總共投入超過1000億美元用于各種相關領域的研究。

這包括用于多芯片和多模塊/封裝通信的硅光子學,已在數據中心內部廣泛用于將服務器連接到存儲器。它將越來越多地用于越來越短的距離。光速非常快,需要最少的能量來實際傳輸信號,并且它產生的熱量非常少。但它也需要監測熱波動,這可能會將信號推到濾波器范圍之外,并檢查波導中的任何粗糙度,這會影響信號。與電子不同,光子不喜歡角落,這是將電音頻構建成芯片的挑戰之一。

“對我們來說,我們希望能夠模擬以某種形狀或方式裝瓶在一起的兩個設備,并能夠模擬和模擬這兩者的組合,”Bartlett說。“EDA的工作人員在后臺做得很好。我們剛剛與一家EDA供應商在我們的45CLO平臺上發布了一個公告(C,L和O是不同的波長波段,每個波長段都有不同的損耗)。這些都是處于行業前沿的領域,我們正在努力為客戶提供正確的設計工具。”

行業都在蓬勃發展。“強勁的晶圓需求使我們的晶圓廠保持滿負荷運轉,并且價格高于我們整體收入的平均混合定價,”聯華電子總裁Jason Wang在最近的業績發布會上表示。“SoC技術,如非易失性存儲器、電源管理、RF-SOI和OLED顯示驅動器,是5G、AIoT和汽車領域的必要應用。我們專注于特種技術的戰略取得了成功,它現在貢獻了我們硅片收入的一半以上。”

Jason Wang指出,汽車的持續電氣化也是未來增長的催化劑。

其他選擇

也許最大的轉變來自封裝選項和小芯片。有許多方法可以將不同的部分放在一起,包括在最先進的節點上開發的數字邏輯與其他邏輯、模擬和在成熟節點上開發出的各種類型的存儲器的混合。事實上,隨著設計變得越來越異構,并針對特定應用和用例進行定制,人們越來越需要為它們增加更大的靈活性。

“我們采訪的一位客戶有一個非常復雜的中斷控制器,”Flex Logix銷售、營銷和解決方案架構副總裁Andy Jaros說。“他們需要預測客戶想要啟動芯片的所有不同排列,包括連接哪些外圍設備或使其可用于外部世界,他們正試圖在軟件控制下做到這一點。他們發現,無論他們如何配置它,或者中斷控制器有多復雜,中斷控制器都不受支持。這就是嵌入式FPGA發揮作用的地方。你可以擁有一個更簡單的中斷控制器,并且該中斷控制器是針對每個客戶精心設計的。因此,現在不必預測每個潛在的引導情況或引導序列或組合變化。基本上,當客戶需要它時,就會生成一些新的RTL,并將其放入該客戶的排序要求中。”

混合和匹配各種組件和過程也會產生一些意想不到的結果。考慮混合鍵合,它提供了一種比將它們焊接在一起更直接的方式來連接不同的組件。

“由于焊料的低溫工藝,它限制了許多下游應用,”Brewer Science晶圓級加工業務部執行董事Kim Yes說。“我們還看到客戶在進行焊球集成的地方,有很多的變形或斷裂,他們現在正在考慮混合粘合。這將比真正的異構集成更快。”

銅到銅混合鍵合是最遠的,但目前正在進行使用電介質進行鍵合的工作。“我們正在與聚合物電介質并行工作,以做同樣的事情,” Brewer Science的科學家Dongshun Bai說。“它仍處于早期發展階段”。

混合鍵合的另一個優點是它減少了粘接中的應力點,這可能導致焊球出現裂紋,特別是在拐角處。“我們聽說過橫向對齊等重大挑戰,” Bai說。“如果對準小于2微米,他們可能會有一些問題。如果微凸塊連接變小,穩定性將是一個問題”。

未來

與過去不同,當整個芯片行業步調一致地走向下一個工藝節點時,有許多可能的途徑在考慮之中。現有節點的工作是使用曲線掩模形狀在光掩模上更準確地打印特征。“今天,即使你畫了一個圓圈,它最終也會在面具上扭曲,”D2S首席執行官Aki Fujimura說。“為了每次都始終如一地做到這一點,它必須大得多,而這不會有用。所以你必須走到生存能力的邊緣,但是如果根據常規,想要可靠它必須更大。但你的工作是讓它盡可能小。”

這就是曲線面罩的適用范圍。使用多光束電子束,可以更準確地打印掩模形狀,以基本上關閉為解釋這些不準確而創建的空白。如果操作正確,這些技術可以幫助擴展節點。

如果這還不夠,那么目前正在進行開發工作,涉及碳納米管FET的2D材料,這些材料在所有領先的代工廠都受到關注。這些結構是否真的會為主流應用、特種芯片實現,還是根本就要不會實現,還有待觀察。雖然使用特殊材料對不同晶體管結構的研究仍在繼續,但領先的 代工廠正在尋求架構和先進封裝作為可能的前進道路,無論是否有OSAT的幫助。

看起來,競爭正在升溫而不是消退,并且正在以盡可能低的成本和最大的可靠性快速“大規模定制”半導體。現在的問題是,哪條路是最好的前進道路,這還有待證明。

審核編輯 :李倩

-

芯片

+關注

關注

463文章

54010瀏覽量

466096 -

晶體管

+關注

關注

78文章

10396瀏覽量

147765 -

繪圖板

+關注

關注

0文章

3瀏覽量

3083

原文標題:根本性變革:芯片架構、晶體管、材料的巨大變化

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

英飛凌下一代電磁閥驅動器評估套件使用指南

英飛凌下一代電磁閥驅動器評估套件使用指南

安森美SiC器件賦能下一代AI數據中心變革

Microchip推出下一代Switchtec Gen 6 PCIe交換芯片

Telechips與Arm合作開發下一代IVI芯片Dolphin7

用于下一代 GGE 和 HSPA 手機的多模式/多頻段功率放大器模塊 skyworksinc

適用于下一代 GGE 和 HSPA 手機的多模/多頻段 PAM skyworksinc

SiLM94112FMG-AQ 12通道高集成半橋驅動,SPI精準控制賦能下一代車身域控

四維圖新加速打造基于地平線征程6B的下一代輔助駕駛系統

安森美攜手英偉達推動下一代AI數據中心發展

下一代高速芯片晶體管解制造問題解決了!

下一代PX5 RTOS具有哪些優勢

外媒稱三星與英飛凌/恩智浦達成合作,共同研發下一代汽車芯片

光庭信息推出下一代整車操作系統A2OS

下一代芯片會什么樣子,什么時候能實現?

下一代芯片會什么樣子,什么時候能實現?

評論