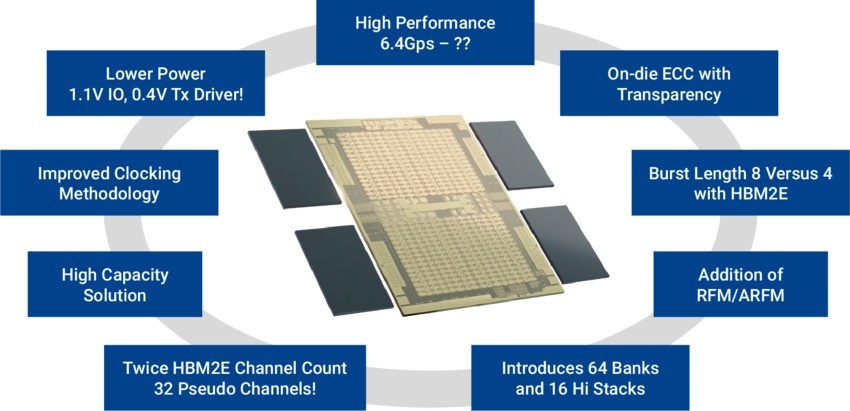

2022 年 1 月,JEDEC 發布了新標準 JESD238“高帶寬內存 (HBM3) DRAM”。與現有的 HBM2E 標準 (JESD235D) 相比,HBM3 標準提出了多項增強功能,包括支持更大的密度、更高速運算、更高的 Bank 數、更高的可靠性、可用性、可維護性 (RAS) 功能、低功耗接口和新的時鐘架構。HBM3 存儲器很快就會被用于 HPC 應用,例如 AI、圖形、網絡,甚至可能用于汽車。本文重點介紹了 HBM3 標準的一些關鍵功能,例如高容量、低功耗、改進的信道和時鐘架構以及更先進的 RAS 選項。圖 1 中突出顯示了一些關鍵功能。

圖 1:HBM3 與 HBM2E 相比具有多項改進,包括更高的容量、更先進的 RAS 功能和更低的功耗

更大、更快、更低功耗

HBM2E標準的每個裸片的最大容量為2GB,每個堆棧可以放置12層裸片,從而可實現24GB的最大容量。雖然標準是允許的,但我們尚未看到市場上出現任何 12 層的 HBM2E 堆棧。HBM3 標準支持裸片的最大容量是4GB,以及高達 16 層的堆棧,總存儲空間可以做到 64 GB,相比HBM2E有近 3 倍的增長。Synopsys 預計 8 層和 12 層堆棧選項中的 16 GB 和 24 GB HBM3 器件很快就會上市。 為了支持更高密度的器件,HBM3 增加了從 12 層堆棧到 16 層堆棧的可用 Bank 數,最多提供 64 個 Bank,增加了 16 個 Bank。 HBM3 標準的最高速度為 6.4 Gbps,幾乎是 HBM2E 的最高速度 3.6 Gbps 的兩倍。 在不久的將來,我們有理由期待第二代 HBM3 設備的出現。只需看看 HBM2/2E、DDR5(6400 Mbps 升級到 8400 Mbps)和 LPDDR5(最大速度為 6400 Mbps,并快速讓位于以 8533 Mbps 運行的 LPDDR5X)的速度歷史記錄,就可見一斑。HBM3 速度高于 6.4 Gbps?這只是時間問題。 除了提高容量和速度外,HBM3 還一直在專注于提高能效。HBM2E 已經提供了最低的傳輸每比特能耗,這主要是由于它是無端接接口,但 HBM3 在 HBM2E 上還有顯著改善。與 HBM2E 的 1.2V 核心電壓相比,HBM3 將核心電壓降低至 1.1V。除了 100mV 內核電源壓降外,HBM3 還可將 IO 信號從 HBM2E 的 1.2V 降低至 400mV。

通道架構

HBM2E 將通道定義為 128 位接口,由兩個 64 位偽通道組成。在從系統訪問內存方面,引腳接口基于每個通道進行定義,而設計人員則認為偽通道是一項關鍵功能。HBM2E 對偽通道的突發長度為 4 拍,允許以 32 字節數據包(8 字節寬,每次訪問 4 拍)訪問內存,該數據包的大小與大多數 GPU 緩存行相當。 HBM3 保持 HBM DRAM 的整體接口大小不變,即 1024 位數據。然而,該 1024 位接口現在被劃分為 16 個 64 位通道,更重要的是,被劃分為 32 個 32 位偽通道。由于偽通道的寬度已減小到 4 字節,因此對存儲器的訪問的突發長度增加到 8 拍,從而維持用于存儲器訪問的 32 字節數據包大小。 偽通道的數量翻倍,加上數據速率的翻倍提升,HBM3可提供比HBM2E更卓越的性能。

可靠性、可用性、可維護性 (RAS)

HBM3 沿襲了 HBM2E 的一些特征,例如數據總線上的 DBI(ac) 和奇偶校驗。命令和地址 (CA) 奇偶校驗等其他特征已發生改變,從命令中的編碼變為 CA 總線上的單獨信號。 HBM3 中 RAS 的最大變化之一是如何處理糾錯碼 (ECC)。我們首先來了解一下 ECC 的主機側。 HBM2E 為主機提供了一個選項,允許 DM 信號重新用作 ECC 存儲位置,從而啟用邊帶 ECC 實現。參考 HBM2E 的偽通道大小,這為用戶提供了非常熟悉的 ECC 選項,與 DDR4 ECC DIMM 非常相似 — 支持 64 位數據和 8 位 ECC。 HBM3 已通過多種方式改變了這種 ECC 方法。首先是完全移除 DM 信號。如果系統的目標是將少于 32 字節的數據傳輸到存儲器,則需要執行讀改寫操作,這可能會對性能造成不利影響。 從 HBM3 標準中刪除 DM 信號后,每個偽通道增加了兩個 ECC 信號。這并不能為用戶提供與 SECDED ECC 相同的功能,因為用戶必須真正考慮 32 字節數據(8 拍期間 4 字節數據)和 2 字節校驗位(8 拍期間 2 位數據)的整個數據包訪問,以匯編 34 字節/272 位代碼。 HBM3 標準還考慮了器件側,要求 HBM3 DRAM 具有片上 ECC。片上 ECC 使用 272 位數據字和 32 位校驗位構建,形成 304 位代碼字。HBM3 DRAM 的數據字大小是主機使用的代碼字大小。現在 HBM3 DRAM 不僅保護數據,還保護主機生成的校驗位。 HBM3 標準實時地提供 ECC 運算的結果。每個偽通道包括兩個嚴重性信號,當從 HBM3 DRAM 讀取時,這兩個嚴重性信號提供有關突發訪問的信息。所提供的信息是四個回答之一 — 所提供的數據沒有錯誤,所提供的數據更正了單個錯誤,所提供的數據更正了多個錯誤,或者所提供的數據有未更正的錯誤。 當器件處于“自刷新”狀態或主機發出“刷新所有 Bank”命令時,HBM3 DRAM 器件還支持錯誤檢查和ECS。ECS 操作的結果可通過 IEEE 標準 1500 測試訪問端口 (TAP) 訪問 ECC 透明度寄存器獲得。 HBM3 標準的新 RAS 功能支持刷新管理 (RFM) 或自適應刷新管理 (ARFM)。通常,RFM/ARFM 被用作一種有意或無意反擊 Row Hammer 的技術。當重復訪問 DRAM 行或行區域會影響未訪問的附近行時,會發生 Row Hammer,從而影響這些附近行中的數據。使用 HBM3 DRAM 中的信息,HBM3 控制器能夠確定何時需要額外的刷新管理來緩解 Row Hammer。

新的時鐘架構

HBM3 的主要功能之一是新的時鐘方案。在所有前幾代 HBM 中,從主機到器件的單個時鐘基本上同步了主機和器件之間的接口。該時鐘信號 (CK) 用于設置從主機傳遞到器件的 CA 信號的傳輸速率。此外,它還固定了數據 (DQ) 和數據選通 (WDQS/RDQS) 在主機和器件(寫入)或器件和主機(讀取)之間傳輸的速率。 在考慮 HBM2E 時,時鐘信號和數據選通均以 1.8 GHz 的最大速率運行,因此 CA 接口上信息傳輸的最大有效速率與數據一樣,都為 3.6 Gbps。 HBM3 通過將傳統時鐘信號從主機去耦到器件和數據選通信號來更改時鐘架構。事實上,雖然 HBM3 中 WDQS 和 RDQS 的全新最大速率為 3.2 GHz,可實現高達 6.4 Gbps 的數據傳輸速率,但 CK 從主機到器件的最快速率僅為 1.6 GHz(即使數據通道以 6.4 Gbps 運行)。 將時鐘信號與選通分離,能使時鐘信號的運行速度大幅度慢于數據選通。CA 總線上的最大信息傳輸速率現在為 3.2 Gbps,因為 CA 時鐘的最大傳輸速率已限制為 1.6 GHz。雖然 HBM2E 需要 3.6 Gbps 的 CA 傳輸速率,但 HBM3 只需要 3.2 Gbps 的 CA 傳輸速率。

高速內部時鐘

分離 CA 時鐘和數據選通的決定不僅會影響主機和器件之間的接口,還會影響主機內部 HBM3 控制器和 HBM3 PHY 的接口。 在典型主機內,控制器和 PHY 與外部存儲器通信。控制器和 PHY 之間的接口通常使用稱為 DDR PHY 接口 (DFI) 的規范來實現。DFI 規范允許 SoC 設計師把通常將系統命令轉換為 HBM 命令的 HBM3 控制器和通常將 SoC 上的數字域轉換為主機到器件接口的模擬域的 HBM3 PHY 的設計分開。在 HBM3 控制器和 HBM3 PHY 之間具有已定義的接口,為設計師和集成商提供了在數字(控制器)和模擬 (PHY) 之間拆分設計團隊的清晰描述。 在高性能 HBM2E 解決方案中,除了帶寬外,延遲也是控制器和 PHY 的重點。在 HBM2E 系統中,時鐘和選通以相同頻率運行,最高可達 1.8 GHz。HBM2E 系統的最低延遲解決方案是使用 DFI 1:1 頻率比 – 使控制器、DFI、PHY 和存儲器都在同一 1.8 GHz 時鐘上運行。 新的 HBM3 時鐘架構使用戶能夠在從 HBM2E 遷移到 HBM3 時專注于低延遲、高性能的解決方案。如上所述,帶 HBM3 的 CA 總線的最高定義頻率為 1.6 GHz,而數據選通以 3.2 GHz 運行。這使用戶能夠為 HBM3 控制器和 PHY 實現 DFI 12 頻率比。在這種情況下,控制器、DFI、PHY 和存儲器時鐘均以 1.6 GHz 運行,而選通頻率為 3.2 GHz。這為設計師提供了命令和地址接口的 DFI 1:1 頻率比以及數據的 DFI 1:2 頻率比,所有這些都最大限度地減少了延遲。

總結

HBM3 標準提供了優于 HBM2E 標準的多項改進。有些是預期的改進 - 更大、更快和功耗更低的器件,有些是意想不到的 – 信道架構變更、RAS 改進和更新的時鐘方法。新標準累計為用戶提供顯著改善的 HBM 存儲器,用于下一代 SoC。 新思科技提供完善的 HBM3 IP 解決方案,包括控制器、領先工藝節點中可用的 PHY 以及已驗證IP。新思科技是 JEDEC 的活躍成員,幫助推動了最新存儲器標準的制定和采用。新思科技的可配置存儲器接口 IP 解決方案可以進行定制以滿足 SoC 的確切要求,用于圖形、云計算、網絡、AI 等應用,甚至是汽車。

審核編輯 :李倩

-

存儲器

+關注

關注

39文章

7739瀏覽量

171676 -

gpu

+關注

關注

28文章

5194瀏覽量

135461 -

堆棧

+關注

關注

0文章

183瀏覽量

20525 -

HBM3

+關注

關注

0文章

75瀏覽量

485

原文標題:設計師需要了解的 HBM3 相關知識

文章出處:【微信號:elecfans,微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

消息稱英偉達HBM4訂單兩家七三分,獨缺這一家

HBM3E反常漲價20%,AI算力競賽重塑存儲芯片市場格局

關于六類網線一些問題的解答

蜂鳥E203的浮點指令集F的一些實現細節

Vivado浮點數IP核的一些設置注意點

HBM技術在CowoS封裝中的應用

傳英偉達自研HBM基礎裸片

求助,關于TC387使能以及配置SOTA 中一些問題求解

有償請教容性負載的放大電路的一些問題

極海APM32F407 uc/os3學習筆記之任務管理介紹

Debian和Ubuntu哪個好一些?

概倫電子芯片級HBM靜電防護分析平臺ESDi介紹

三星在4nm邏輯芯片上實現40%以上的測試良率

樹莓派在自動化控制項目中的一些潛在應用

介紹HBM3標準的一些關鍵功能

介紹HBM3標準的一些關鍵功能

評論