電子發燒友網報道(文/吳子鵬)在過去的數十年里,摩爾定律一直被視為半導體產業的金科玉律,特征尺寸的縮小,為芯片帶來了性能的提升和功耗的降低。同時,制造工藝的精進也讓消費電子和大算力需求受益匪淺,發展迅速。時至今日,摩爾定律看似還在延續,然而工藝數字已經越來越接近物理極限,成本、良率以及不斷壓縮的創新周期,更是給芯片設計公司帶來了巨大的挑戰。

EDA進入2.0時代

如何延續和超越摩爾定律,成為后摩爾定律時代整個半導體產業面臨的時代課題。在此過程中,EDA作為產業的最上游,串聯著設計、制造、封裝和應用,是產業實現超越摩爾的重要抓手。

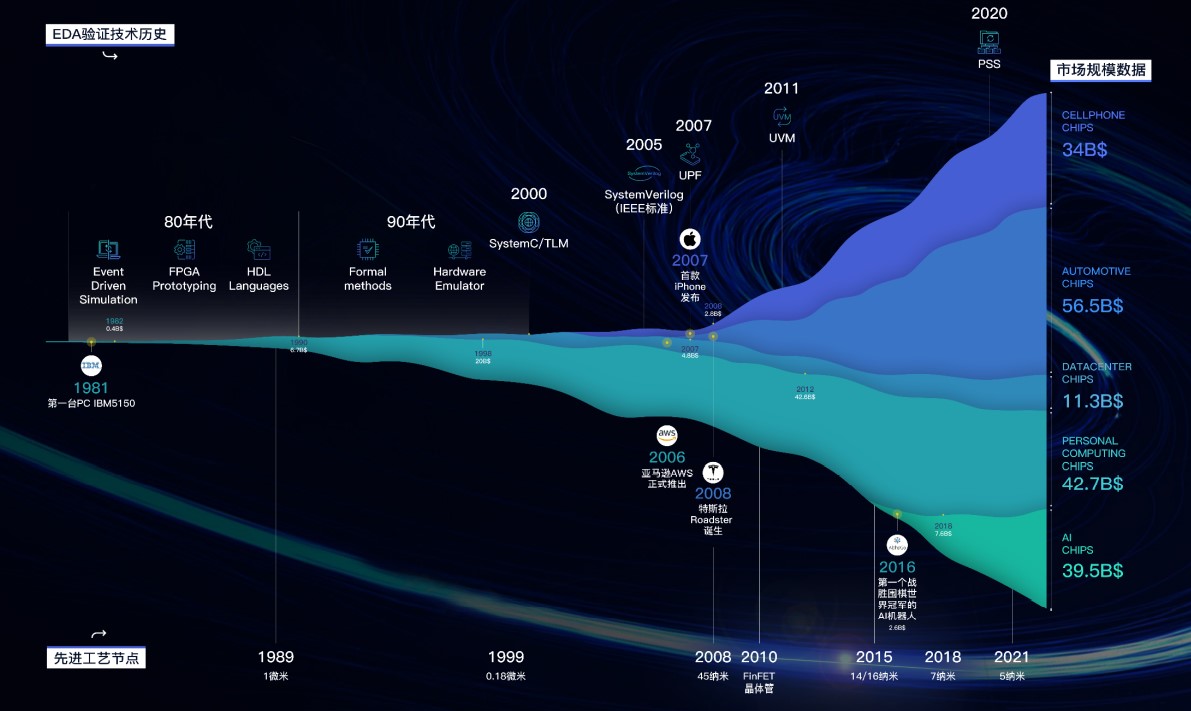

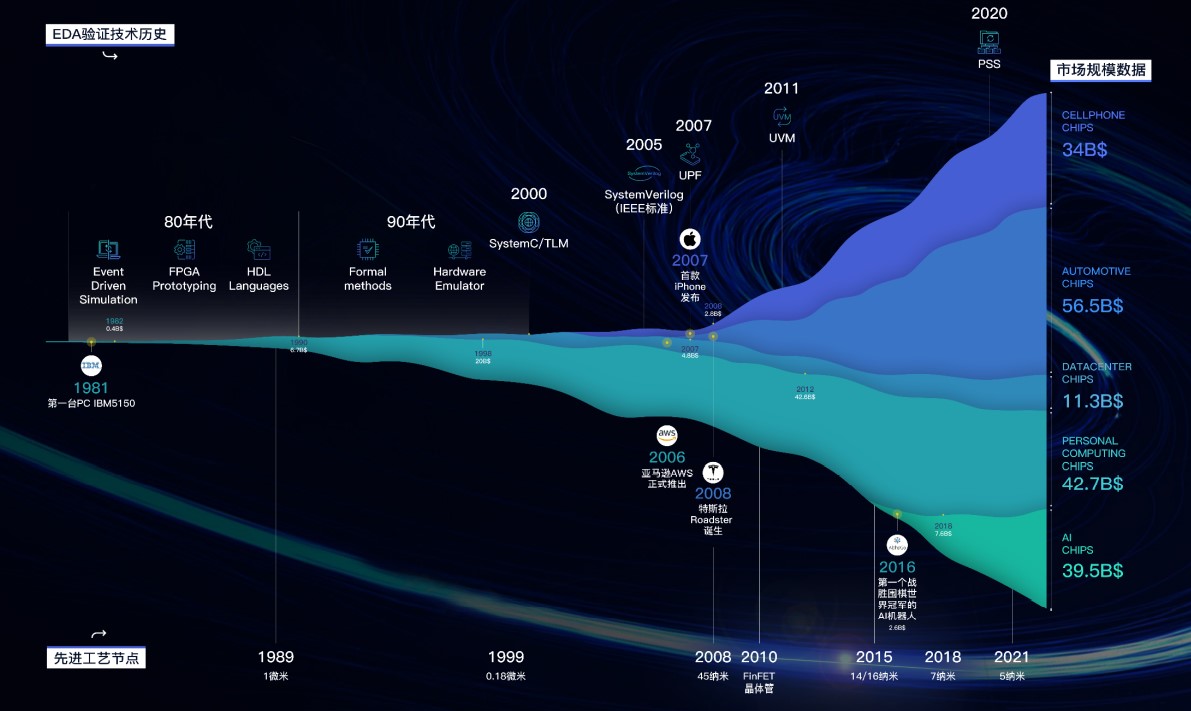

芯華章首席市場戰略官謝仲輝表示:“當前,新興領域在飛速發展,市場規模在急速擴大,這也意味著產業數字化需求越來越多,發展越來越快。在此過程中,近十年芯片驗證技術并沒有太大改進,然而架構創新和算法創新已然變得越來越重要。后摩爾定律時代,EDA工具不能只是支持芯片設計,更需要面向整個系統,滿足系統設計和應用創新需求。”

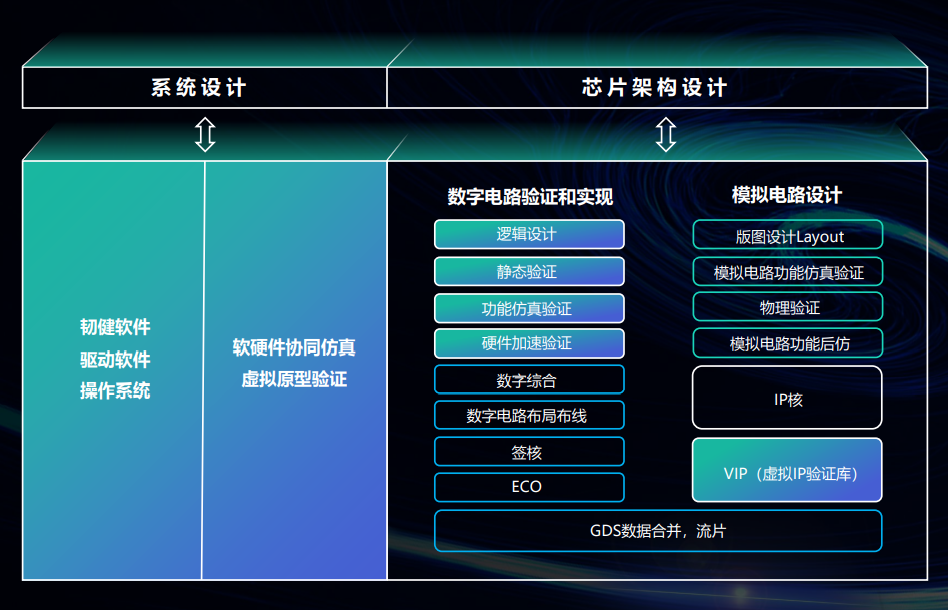

圖源:芯華章

謝仲輝認為,這是EDA 1.0向EDA 2.0時代的演進。

能夠看到,這是一個本質的改變,從傳統EDA定義來看,電子設計自動化是指借助計算輔助設計軟件,完成超大規模集成電路芯片的功能設計、綜合、驗證、物理設計等設計流程。在這里面,EDA工具面向的主要對象是芯片,幫助芯片在更先進的工藝上實現更強悍的功能。然而,我們已經提到,當工藝節點越小,這樣做的成本越高昂,且風險性極高。根據IBS的相關統計數據,從28nm到5nm,集成電路設計成本從5130萬美元暴漲到了5.422億美元。并且,3nm的集成電路設計成本接近甚至超過了10億美元,這樣高昂的成本讓小公司望而卻步,讓大公司更加謹慎。

而在后摩爾定律時代,在SoC層面為了能夠降低芯片的成本,異構集成和Chiplet成為產業的熱門話題,同時先進封裝讓系統級芯片的關注點從單位面積上的晶體管數量變為單位面積上的連接點數量。無疑,這些積極的改變都對EDA工具提出了全新的要求。

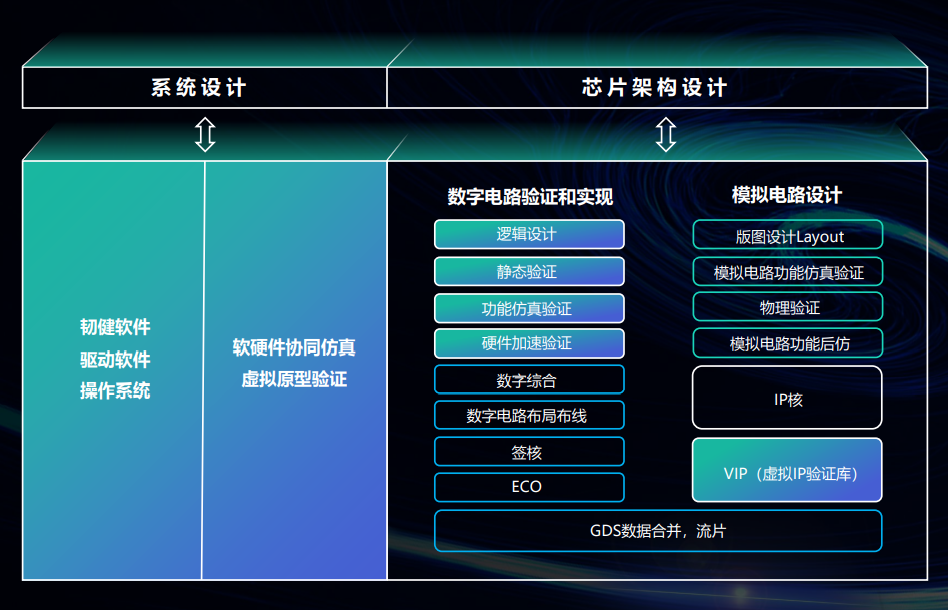

芯華章致力于面向未來的EDA 2.0智能化電子設計平臺的研究與開發,根據謝仲輝的介紹,芯華章打造從芯片到系統的驗證解決方案,在芯片架構設計方面,目前芯華章主要專注在數字前端驗證方面,并已基本建立可滿足完整數字驗證流程所需的產品線,得到中科院半導體所、燧原科技、芯來、鯤云等一眾業內知名企業實際項目采用,為賦能電子系統創新,提供了自主可信賴的底層技術支持。

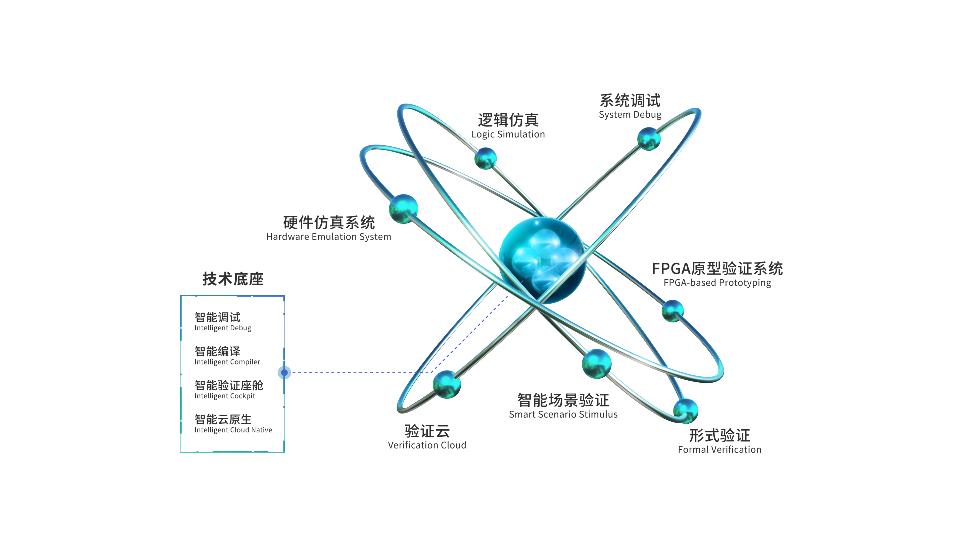

圖源:芯華章

國產EDA如何突圍?

我們看到在“EDA 1.0時代”,全球EDA行業高度集中,Synopsys(新思科技)、Cadence(楷登電子)和西門子旗下的Siemens EDA占據了主要市場份額,三家公司的產品覆蓋了傳統芯片設計的全流程,具有明顯的“寡頭效應”和極高的技術壁壘,在這樣的情況下,國產EDA該如何實現突圍呢?

芯華章董事長兼CEO王禮賓談到了公司的一些規劃,他講到:“芯華章具有三個特點,分別是高起點、厚積累、求創新。高起點是指芯華章了解產業幾十年發展下來的痛點,從一開始就可以用最新的架構去做EDA工具,并且應用人工智能、云原生等先進技術;厚積累是指芯華章成立之初,幾十個核心技術人員都具備15年以上的EDA工具研發經驗;求創新是指芯華章在積累的基礎上,有創新的意識,不斷去創新,因為只是模仿別人很難實現超越。”

在“厚積累”環節,王禮賓特別指出,積累分為資產的積累和知識的積累,對于EDA這樣的高科技產業而言,更重要的是知識的積累,很多技術的東西都在人的大腦里面,所以做EDA工具一定要去尋找那些有積累、有經驗的人。

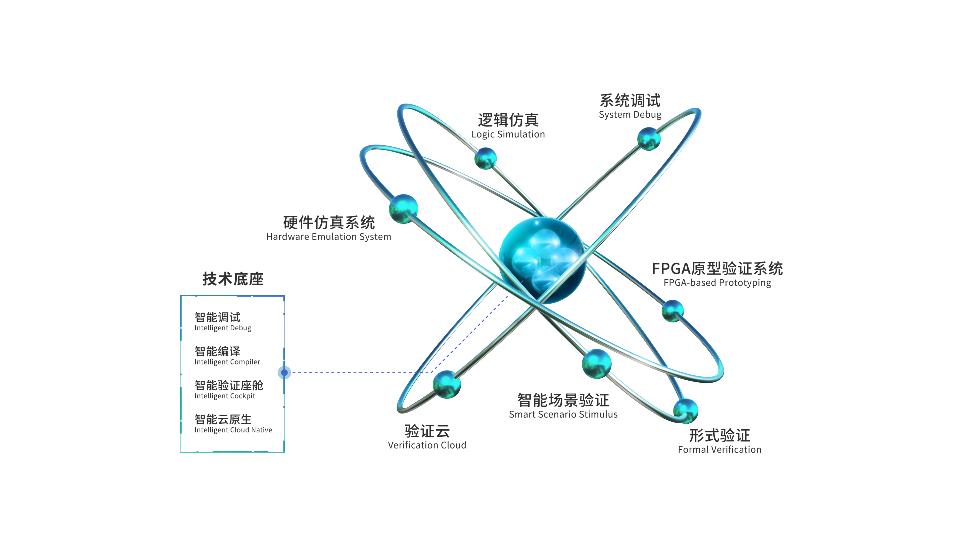

目前,芯華章已經集結了一支400余人的全球化精英團隊,其中八成為尖端研發人員,碩博比例高達80%,已獲得專利授權25件。得益于扎實的人才與技術積累,芯華章已經打造了具備統一底層框架的智V驗證平臺,并成功發布了五款自研數字驗證EDA產品,涵蓋邏輯仿真、形式驗證、原型驗證、場景驗證、系統調試等多個領域。

芯華章七大產品系列

人才一直都是EDA行業的熱門話題,同時人才問題也是國產EDA發展的痛點。有行業人士表示,EDA人才培養周期至少是十年,主要的人才需求是軟件、芯片、數學及微電子學科這幾大類中的至少兩種以上的復合型人才。為了構筑人才及技術創新戰略優勢,7月28日芯華章研究院正式成立,中國工程院院士沈昌祥出任榮譽院長,并邀請中國科學院院士毛軍發出任首席專家顧問。

王禮賓表示:“芯華章必將堅定地支持、持續投入那些前瞻性、方向性,能夠引領未來的技術。芯華章研究院將打造一流的創新環境、樹立清晰的技術路標,承擔起推動前沿技術突破的職責。下一步,我們將重點引入包含自然語言處理、深度學習等領域的高端技術人才,同時深入探索與高等院校、科研院所的深度合作機制,以體系化的方式共同探索EDA 2.0,實現全面的自主技術創新突破。”

而在求創新方面,近幾年EDA行業也在需求通過AI(人工智能)提升工具的效率,在EDA工具中采用人工智能技術,已經成為了EDA技術創新的關鍵。芯華章科技產業和業務規劃總監楊曄表示:“AI 在后端的布局以及光刻版圖設計兩個方面是落地最快,也是利用最成功的。從某種意義上來說,AI跟EDA的結合,最容易解決的一些問題已經被初步地解決了,下一步就是在更傳統的EDA計算領域應用AI技術。AI在EDA前端,特別是驗證以及仿真里,大體上是用來縮小求解空間,快速地進入精確計算的過程,從而縮短整個驗證周期,以及減少驗證過程當中的人力投入,加快芯片上市。在芯華章目前的產品中,仿真、形式化驗證、原型驗證等方向上都應用到了AI。”

EDA被稱為“芯片設計之母”,而芯片又是信息產業的基礎,因此EDA軟件的重要性是不言而喻的。目前,我國非常重視EDA產業的發展,在國家和地方提出的《十四五規劃》等相關政策中,都提到了要大力發展EDA。在政策和資金的助力下,國產EDA迎來了黃金發展期。

然而,我們也不得不思考一個根本性的問題,EDA工具成本不低,重要性更是不需多說,如何讓廠商相信和選擇使用國產EDA呢?

“傳統的EDA工具存在一些明顯的短板,比如工具碎片化問題,還有開放性、數據互通等方面的問題,對創新造成了很大的阻礙。我們在參加全球電子設計自動化盛會DAC時,芯華章的工具不僅得到了小公司的關注,還有很多大的系統公司也在關注,這就說明這些公司的需求并沒有被現有的工具滿足,意味著EDA還存在非常大的創新空間。” 謝仲輝談到,“芯華章是從底層架構搭建EDA工具,我們統一的數據庫有比較輕量的代碼,能夠帶來較為明顯的效率提升,同時在產品面和技術面能夠給到客戶廠商更好的支持。”

EDA進入2.0時代

如何延續和超越摩爾定律,成為后摩爾定律時代整個半導體產業面臨的時代課題。在此過程中,EDA作為產業的最上游,串聯著設計、制造、封裝和應用,是產業實現超越摩爾的重要抓手。

芯華章首席市場戰略官謝仲輝表示:“當前,新興領域在飛速發展,市場規模在急速擴大,這也意味著產業數字化需求越來越多,發展越來越快。在此過程中,近十年芯片驗證技術并沒有太大改進,然而架構創新和算法創新已然變得越來越重要。后摩爾定律時代,EDA工具不能只是支持芯片設計,更需要面向整個系統,滿足系統設計和應用創新需求。”

圖源:芯華章

能夠看到,這是一個本質的改變,從傳統EDA定義來看,電子設計自動化是指借助計算輔助設計軟件,完成超大規模集成電路芯片的功能設計、綜合、驗證、物理設計等設計流程。在這里面,EDA工具面向的主要對象是芯片,幫助芯片在更先進的工藝上實現更強悍的功能。然而,我們已經提到,當工藝節點越小,這樣做的成本越高昂,且風險性極高。根據IBS的相關統計數據,從28nm到5nm,集成電路設計成本從5130萬美元暴漲到了5.422億美元。并且,3nm的集成電路設計成本接近甚至超過了10億美元,這樣高昂的成本讓小公司望而卻步,讓大公司更加謹慎。

而在后摩爾定律時代,在SoC層面為了能夠降低芯片的成本,異構集成和Chiplet成為產業的熱門話題,同時先進封裝讓系統級芯片的關注點從單位面積上的晶體管數量變為單位面積上的連接點數量。無疑,這些積極的改變都對EDA工具提出了全新的要求。

芯華章致力于面向未來的EDA 2.0智能化電子設計平臺的研究與開發,根據謝仲輝的介紹,芯華章打造從芯片到系統的驗證解決方案,在芯片架構設計方面,目前芯華章主要專注在數字前端驗證方面,并已基本建立可滿足完整數字驗證流程所需的產品線,得到中科院半導體所、燧原科技、芯來、鯤云等一眾業內知名企業實際項目采用,為賦能電子系統創新,提供了自主可信賴的底層技術支持。

圖源:芯華章

國產EDA如何突圍?

我們看到在“EDA 1.0時代”,全球EDA行業高度集中,Synopsys(新思科技)、Cadence(楷登電子)和西門子旗下的Siemens EDA占據了主要市場份額,三家公司的產品覆蓋了傳統芯片設計的全流程,具有明顯的“寡頭效應”和極高的技術壁壘,在這樣的情況下,國產EDA該如何實現突圍呢?

芯華章董事長兼CEO王禮賓談到了公司的一些規劃,他講到:“芯華章具有三個特點,分別是高起點、厚積累、求創新。高起點是指芯華章了解產業幾十年發展下來的痛點,從一開始就可以用最新的架構去做EDA工具,并且應用人工智能、云原生等先進技術;厚積累是指芯華章成立之初,幾十個核心技術人員都具備15年以上的EDA工具研發經驗;求創新是指芯華章在積累的基礎上,有創新的意識,不斷去創新,因為只是模仿別人很難實現超越。”

在“厚積累”環節,王禮賓特別指出,積累分為資產的積累和知識的積累,對于EDA這樣的高科技產業而言,更重要的是知識的積累,很多技術的東西都在人的大腦里面,所以做EDA工具一定要去尋找那些有積累、有經驗的人。

目前,芯華章已經集結了一支400余人的全球化精英團隊,其中八成為尖端研發人員,碩博比例高達80%,已獲得專利授權25件。得益于扎實的人才與技術積累,芯華章已經打造了具備統一底層框架的智V驗證平臺,并成功發布了五款自研數字驗證EDA產品,涵蓋邏輯仿真、形式驗證、原型驗證、場景驗證、系統調試等多個領域。

芯華章七大產品系列

人才一直都是EDA行業的熱門話題,同時人才問題也是國產EDA發展的痛點。有行業人士表示,EDA人才培養周期至少是十年,主要的人才需求是軟件、芯片、數學及微電子學科這幾大類中的至少兩種以上的復合型人才。為了構筑人才及技術創新戰略優勢,7月28日芯華章研究院正式成立,中國工程院院士沈昌祥出任榮譽院長,并邀請中國科學院院士毛軍發出任首席專家顧問。

王禮賓表示:“芯華章必將堅定地支持、持續投入那些前瞻性、方向性,能夠引領未來的技術。芯華章研究院將打造一流的創新環境、樹立清晰的技術路標,承擔起推動前沿技術突破的職責。下一步,我們將重點引入包含自然語言處理、深度學習等領域的高端技術人才,同時深入探索與高等院校、科研院所的深度合作機制,以體系化的方式共同探索EDA 2.0,實現全面的自主技術創新突破。”

而在求創新方面,近幾年EDA行業也在需求通過AI(人工智能)提升工具的效率,在EDA工具中采用人工智能技術,已經成為了EDA技術創新的關鍵。芯華章科技產業和業務規劃總監楊曄表示:“AI 在后端的布局以及光刻版圖設計兩個方面是落地最快,也是利用最成功的。從某種意義上來說,AI跟EDA的結合,最容易解決的一些問題已經被初步地解決了,下一步就是在更傳統的EDA計算領域應用AI技術。AI在EDA前端,特別是驗證以及仿真里,大體上是用來縮小求解空間,快速地進入精確計算的過程,從而縮短整個驗證周期,以及減少驗證過程當中的人力投入,加快芯片上市。在芯華章目前的產品中,仿真、形式化驗證、原型驗證等方向上都應用到了AI。”

EDA被稱為“芯片設計之母”,而芯片又是信息產業的基礎,因此EDA軟件的重要性是不言而喻的。目前,我國非常重視EDA產業的發展,在國家和地方提出的《十四五規劃》等相關政策中,都提到了要大力發展EDA。在政策和資金的助力下,國產EDA迎來了黃金發展期。

然而,我們也不得不思考一個根本性的問題,EDA工具成本不低,重要性更是不需多說,如何讓廠商相信和選擇使用國產EDA呢?

“傳統的EDA工具存在一些明顯的短板,比如工具碎片化問題,還有開放性、數據互通等方面的問題,對創新造成了很大的阻礙。我們在參加全球電子設計自動化盛會DAC時,芯華章的工具不僅得到了小公司的關注,還有很多大的系統公司也在關注,這就說明這些公司的需求并沒有被現有的工具滿足,意味著EDA還存在非常大的創新空間。” 謝仲輝談到,“芯華章是從底層架構搭建EDA工具,我們統一的數據庫有比較輕量的代碼,能夠帶來較為明顯的效率提升,同時在產品面和技術面能夠給到客戶廠商更好的支持。”

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

摩爾定律

+關注

關注

4文章

640瀏覽量

80807 -

eda

+關注

關注

72文章

3108瀏覽量

182485

發布評論請先 登錄

相關推薦

熱點推薦

【「芯片設計基石——EDA產業全景與未來展望」閱讀體驗】--中國EDA的發展

,半導體產業鏈蓬勃興起,上下游企業緊密協作,從材料研發到芯片制造,再到產品應用,形成完整閉環,為EDA工具提供了廣闊的施展空間。芯片性能、功耗、尺寸等方面的嚴苛要求,讓EDA從幕后走向

發表于 01-20 23:22

【「芯片設計基石——EDA產業全景與未來展望」閱讀體驗】+ 全書概覽

不斷完善6.5.1企業數量與規模增長6.5.2技術創新能力提升6.5.3產業鏈上下游協同發展6.5.4市場認可度提高第7章啟航未來:全球EDA發展趨勢洞察 7.1EDA技術發展趨勢7.1.1后

發表于 01-20 19:27

70%營收砸向研發!這家EDA企業破局高密度存儲EDA、數字EDA

短板,構建覆蓋芯片設計全流程的自主工具鏈。 ? 聚焦存儲芯片EDA,實現全流程國產化突破 ? 后摩爾時代,芯片性能提升轉向“尺寸微縮、新原理器件、集成芯片”三路徑并行,推動

國產EDA的AI進程究竟到哪一步了

首當其沖,算力、存儲、網絡、電源等核心要素必須加速進階:一方面,AI 大模型訓練與推理需求爆發,面臨摩爾定律放緩、單芯片工藝微縮的性能提升有限,Chiplet 先進封裝成為延續算力增長的關鍵。EDA 工具需從單芯片設計擴展至封裝

后摩爾定律時代,3D-CIM+RISC-V打造國產存算一體新范式

電子發燒友網報道(文 / 吳子鵬)當前,AI 技術已深度融入生產生活,從 AI 手機、AI?PC 到云端大模型推理,再到未來的具身智能機器人,對算力的需求呈指數級增長。然而,在 AI 飛速發展的同時

發表于 09-17 09:31

?5730次閱讀

后摩爾定律時代,國產半導體設備的前瞻路徑分析

戰略引領,深化創新驅動,共筑半導體裝備產業新高地” 為主題,匯聚了國內半導體設備領域的頂尖專家與企業領袖。 ? 在大會的主題演講環節,中國電子專用設備工業協會副秘書長、工信部電子科技委專家委員李晉湘,中電科電子裝備集團有限公司黨委

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創新將繼續維持著摩爾神話

。那該如何延續摩爾神話呢?

工藝創新將是其途徑之一,芯片中的晶體管結構正沿著摩爾定律指出的方向一代代演進,本段加速半導體的微型化和進一步集成,以滿足AI技術及高性能計算飛速發展的需求。

CMOS工藝

發表于 09-06 10:37

當摩爾定律 “踩剎車” ,三星 、AP、普迪飛共話半導體制造新變革新機遇

,揭示行業正處于從“晶體管密度驅動”向“系統級創新”轉型的關鍵節點。隨著摩爾定律放緩、供應鏈分散化政策推進,一場融合制造技術革新與供應鏈數字化的產業變革正在上演。

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

在摩爾定律逐漸放緩的背景下,Chiplet(小芯片)技術和3D封裝成為半導體行業突破性能與集成度瓶頸的關鍵路徑。然而,隨著芯片集成度的提高,氣泡缺陷成為影響封裝良率的核心挑戰之一。

晶心科技:摩爾定律放緩,RISC-V在高性能計算的重要性突顯

運算還是快速高頻處理計算數據,或是超級電腦,只要設計或計算系統符合三項之一即可稱之為HPC。 摩爾定律走過數十年,從1970年代開始,世界領導廠商建立晶圓廠、提供制程工藝,在28nm之前取得非常大的成功。然而28nm之后摩爾定律

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

。 然而,隨著摩爾定律逼近物理極限,傳統掩模設計方法面臨巨大挑戰,以2nm制程為例,掩膜版上的每個圖形特征尺寸僅為頭發絲直徑的五萬分之一,任何微小誤差都可能導致芯片失效。對此,新思科技(Synopsys)推出制造解決方案,尤其是

電力電子中的“摩爾定律”(1)

本文是第二屆電力電子科普征文大賽的獲獎作品,來自上海科技大學劉賾源的投稿。著名的摩爾定律中指出,集成電路每過一定時間就會性能翻倍,成本減半。那么電力電子當中是否也存在著摩爾定律呢?1965年,英特爾

玻璃基板在芯片封裝中的應用

上升,摩爾定律的延續面臨巨大挑戰。例如,從22納米工藝制程開始,每一代技術的設計成本增加均超過50%,3納米工藝的總設計成本更是高達15億美元。此外,晶體管成本縮放規律在28納米制程后已經停滯。

瑞沃微先進封裝:突破摩爾定律枷鎖,助力半導體新飛躍

在半導體行業的發展歷程中,技術創新始終是推動行業前進的核心動力。深圳瑞沃微半導體憑借其先進封裝技術,用強大的實力和創新理念,立志將半導體行業邁向新的高度。 回溯半導體行業的發展軌跡,摩爾定律無疑是一個重要的里程碑

后摩爾定律時代,國產EDA如何“從0到1”做創新?

后摩爾定律時代,國產EDA如何“從0到1”做創新?

評論