電子發燒友網報道(文/周凱揚)對于近幾年推出的HPC系統來說,高能效已經成了大家無法規避的話題,就連TOP500上的超算,比如排名第一的超級計算機,美國能源部下屬國家實驗室的Frontier系統,也憑借單機柜原型機在GREEN500能效榜上拿下第一,整個系統拿下了第二的成績。與十多年前的那些HPC系統相比,現在的設計不僅是在性能上不可同日而語,連能效比也提升了百倍以上。

能做到如此高的能效,除了CPU、GPU本身的設計外,也要歸功于先進的冷卻系統和電源管理。對于已經走向多核異構時代的HPC系統而言,系統級別的電源與熱管理尤為重要,而且還得做到精心調校、針對負載進行智能調整的動態電源管理。

已有的電源控制器方案

針對不同的CPU系統,市面上已經有了不少商用電源控制器,比如英特爾的CPU有用于C-States管理的電源控制單元(PCU),ARM有幫助應用處理器卸載電源與系統管理任務的系統控制處理器(SCP)和可管理控制處理器(MCP),AMD有采集傳感數據進行快速調整的系統管理單元(SMU),IBM的Power處理器有片上控制器(OCC)等。

然而,不少已有的方案都是基于單核心的MCU打造的,在面對單片核心數越來越多以及逐漸普及的Chiplet設計時,這些方案就因為缺乏擴展性而顯得力不從心了。除此之外,主辦的尺寸、布局和成本的因素,進一步限制了HPC處理器本身的片上電源管理。正因如此,在擁有龐大核心數量的HPC系統上,我們需要一個可擴展的控制器方案。

在這些要求下,瑞士蘇黎世聯邦理工學院(ETH)的集成系統實驗室就基于開源的RISC-V架構,打造了這樣一個擁有并行控制規則計算加速的電源控制器IP——ControlPULP。

可擴展的電源控制器

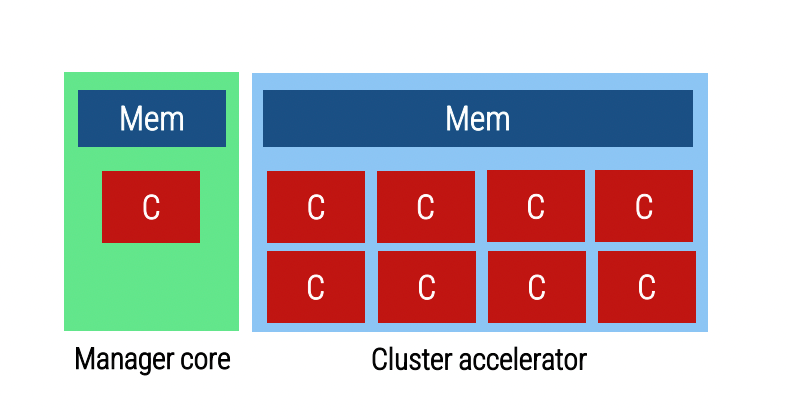

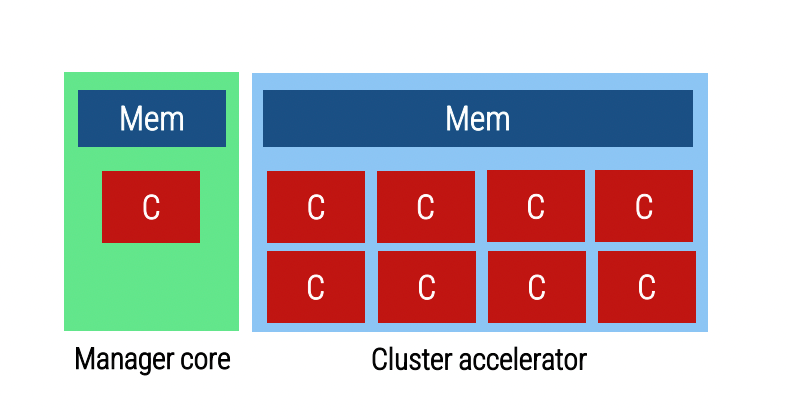

ControlPULP采用了九核的設計,一個單核管理器核心,和8核的加速器簇來加速電源控制固件的工作負載,而這九個核心全部基于CV32E40P,這是一個32位4級流水線的RISC-V開源核心,由瑞士蘇黎世聯邦理工學院和意大利博羅尼亞大學合作的PULP平臺維護,他們也將CV32E40P捐獻給了開放硬件聯盟OpenHW。

ControlPULP架構 / 瑞士蘇黎世聯邦理工學院

此外,ControlPULP集成了一個直接內存訪問引擎,用于獲取片上傳感器的數據,還有一個uDMA引擎,用于支持基于標準電源管理接口(比如電壓調節總線AVSBUS/PMBUS)的片外外圍設備以及通過I2C或MTCP協議的BMC通信。至于底層控制策略的調度,則靠PULP平臺自己開發的開源FreeRTOS來實現。

在其電源控制策略中,ControlPULP主要負責兩大主要控制任務,一個是定期控制任務,一個是電源控制任務。定期控制任務結合溫度傳感器、功耗傳感器內的數據,以及目標頻率、預期負載和總功耗預算等數據,來進行電源調度和熱管理。電源控制任務則是通過PMBUS/AVSBUS獲得的電壓軌功耗和BMC通信來完成快速電源控制。

根據他們測試的結果,這種多核加速器簇的結構相較過去的單核方案來說,在控制策略的執行速度上快了5倍,而且集成在HPC處理器中并不會占用多大的面積。他們在格芯的GF22FDX工藝下得到的綜合結果中,ControlPULP所占處理器面積甚至不到百分之一。

開源電源控制器的未來

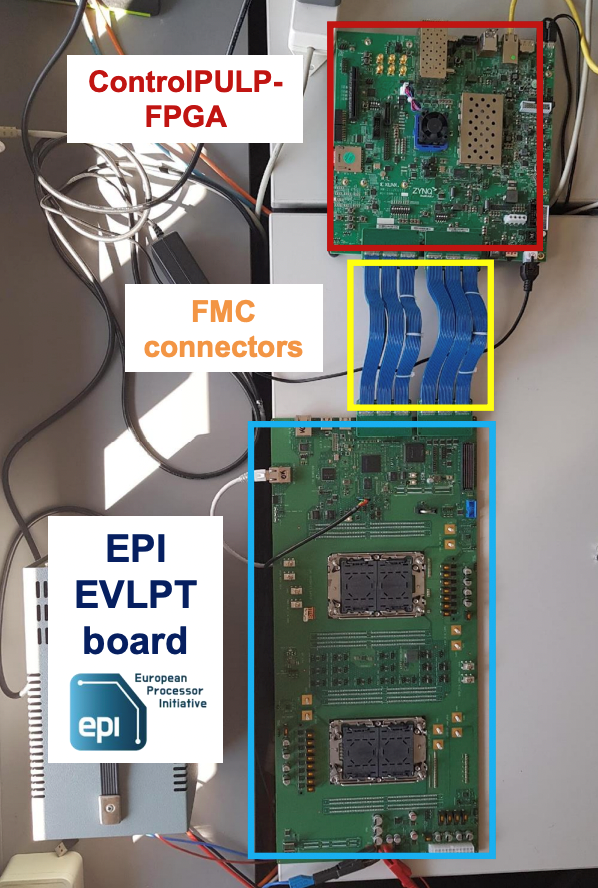

ControlPULP作為一個軟硬件完全開源的集成IP方案,不少人擔心是否真的會有人將其投入商用,事實上,這樣的案例已經快要面世了。根據ETH透露,歐洲處理器計劃(EPI)的先行者,法國企業SiPearl的E級HPC芯片,72核的Rhea處理器就將集成ControlPULP。

不過,這還只是ControlPULP邁出的第一步,未來PULP團隊還計算完成65nm的流片來進一步開展硬件驗證,并探索更先進的預測性電源控制策略。但不管怎么說,這都是首個RISC-V的HPC電源控制器方案,RISC-V在HPC市場也需要更多的亮相,而不僅僅只是作為加速器。

能做到如此高的能效,除了CPU、GPU本身的設計外,也要歸功于先進的冷卻系統和電源管理。對于已經走向多核異構時代的HPC系統而言,系統級別的電源與熱管理尤為重要,而且還得做到精心調校、針對負載進行智能調整的動態電源管理。

已有的電源控制器方案

針對不同的CPU系統,市面上已經有了不少商用電源控制器,比如英特爾的CPU有用于C-States管理的電源控制單元(PCU),ARM有幫助應用處理器卸載電源與系統管理任務的系統控制處理器(SCP)和可管理控制處理器(MCP),AMD有采集傳感數據進行快速調整的系統管理單元(SMU),IBM的Power處理器有片上控制器(OCC)等。

然而,不少已有的方案都是基于單核心的MCU打造的,在面對單片核心數越來越多以及逐漸普及的Chiplet設計時,這些方案就因為缺乏擴展性而顯得力不從心了。除此之外,主辦的尺寸、布局和成本的因素,進一步限制了HPC處理器本身的片上電源管理。正因如此,在擁有龐大核心數量的HPC系統上,我們需要一個可擴展的控制器方案。

在這些要求下,瑞士蘇黎世聯邦理工學院(ETH)的集成系統實驗室就基于開源的RISC-V架構,打造了這樣一個擁有并行控制規則計算加速的電源控制器IP——ControlPULP。

可擴展的電源控制器

ControlPULP采用了九核的設計,一個單核管理器核心,和8核的加速器簇來加速電源控制固件的工作負載,而這九個核心全部基于CV32E40P,這是一個32位4級流水線的RISC-V開源核心,由瑞士蘇黎世聯邦理工學院和意大利博羅尼亞大學合作的PULP平臺維護,他們也將CV32E40P捐獻給了開放硬件聯盟OpenHW。

ControlPULP架構 / 瑞士蘇黎世聯邦理工學院

此外,ControlPULP集成了一個直接內存訪問引擎,用于獲取片上傳感器的數據,還有一個uDMA引擎,用于支持基于標準電源管理接口(比如電壓調節總線AVSBUS/PMBUS)的片外外圍設備以及通過I2C或MTCP協議的BMC通信。至于底層控制策略的調度,則靠PULP平臺自己開發的開源FreeRTOS來實現。

在其電源控制策略中,ControlPULP主要負責兩大主要控制任務,一個是定期控制任務,一個是電源控制任務。定期控制任務結合溫度傳感器、功耗傳感器內的數據,以及目標頻率、預期負載和總功耗預算等數據,來進行電源調度和熱管理。電源控制任務則是通過PMBUS/AVSBUS獲得的電壓軌功耗和BMC通信來完成快速電源控制。

根據他們測試的結果,這種多核加速器簇的結構相較過去的單核方案來說,在控制策略的執行速度上快了5倍,而且集成在HPC處理器中并不會占用多大的面積。他們在格芯的GF22FDX工藝下得到的綜合結果中,ControlPULP所占處理器面積甚至不到百分之一。

開源電源控制器的未來

ControlPULP作為一個軟硬件完全開源的集成IP方案,不少人擔心是否真的會有人將其投入商用,事實上,這樣的案例已經快要面世了。根據ETH透露,歐洲處理器計劃(EPI)的先行者,法國企業SiPearl的E級HPC芯片,72核的Rhea處理器就將集成ControlPULP。

不過,這還只是ControlPULP邁出的第一步,未來PULP團隊還計算完成65nm的流片來進一步開展硬件驗證,并探索更先進的預測性電源控制策略。但不管怎么說,這都是首個RISC-V的HPC電源控制器方案,RISC-V在HPC市場也需要更多的亮相,而不僅僅只是作為加速器。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

電源控制器

+關注

關注

0文章

177瀏覽量

34313 -

HPC

+關注

關注

0文章

346瀏覽量

24979 -

RISC-V

+關注

關注

48文章

2886瀏覽量

53029

發布評論請先 登錄

相關推薦

熱點推薦

Renesas R9A02G021:32位RISC-V MCU的全方位解析

Renesas R9A02G021:32位RISC-V MCU的全方位解析 作為一名電子工程師,在日常的硬件設計開發中,選擇合適的微控制器(MCU)至關重要。今天,我們就來深入探討一下

RISC-V怎么實現核間中斷?核心本地中斷控制器(CLINT)深度解析

全稱為Core Local Interruptor(核心本地中斷控制器),是 RISC-V 特權架構規范(Privileged Architecture Specification)中明確定義的內建

探索RISC-V在機器人領域的潛力

的硬件配置給人留下了深刻的第一印象:

? 核心處理器: 搭載了進迭時空的K1系列高性能RISC-V處理器,具備強大的通用計算能力和AI加速特性。

? 內存與存儲: 板載LPDDR4

發表于 12-03 14:40

易靈思Sapphire SoC中RISC-V平臺級中斷控制器深度解析

隨著 RISC -V處理器在 FPGA 領域的廣泛應用,易靈思 FPGA 的 Sapphire RISC-V 內核憑借軟硬核的靈活支持,為開發者提供多樣選擇。本文深入探討 Sapph

為什么RISC-V是嵌入式應用的最佳選擇

最近RISC-V基金會在社交媒體上發文,文章說物聯網和嵌入式系統正在迅速發展,需要更高的計算性能、更低的功耗和人工智能。RISC-V是為未來而建的,包括超高效的MCU到高性能應用處理器

提高RISC-V在Drystone測試中得分的方法

性能:內存的讀寫速度、延遲和帶寬等都會影響到 Drystone 的性能。

指令集優化:對RISC-V指令集的優化也會影響性能。例如,對于特定的應用或計算任務,可以通過定制指令集來提高性能。

編譯

發表于 10-21 13:58

RISC-V B擴展介紹及實現

某個方向移位并將結果存儲在目標寄存器中;后者則用于為一個值生成一個位掩碼。

此外,B擴展還增加了一組壓縮指令,可以使指令占用更少的內存空間,從而提高

發表于 10-21 13:01

2025新思科技RISC-V科技日活動圓滿結束

新思科技深度參與2025 RISC-V中國峰會并于2025年7月16日舉辦同期活動“新思科技RISC-V科技日”技術論壇,聚焦“從芯片到系統重構RISC-V創新”主題,議題覆蓋當前最前

RISC-V 發展態勢與紅帽系統適配進展

,硬件情況有了改善,紅帽也成為最早支持 RISC-V 系統的企業之一,當時已能搭建支持桌面的系統,這在當時是很大的突

發表于 07-18 10:55

?4075次閱讀

RISC-V International CEO:RISC-V 應用全面開花,2031 年滲透率將達 25.7%

and RISC-V Adoption in 2025》。 ? 當前,RISC-V 的成功已從嵌入式計算領域加速向存儲技術與高性能計算(HPC)領域滲透,展現出跨行業的顛覆性潛力。Andrea Gallo 分享了 The SH

發表于 07-17 10:28

?3700次閱讀

【好書推薦】RT-Thread第18本相關書籍!RISC-V嵌入式系統設計 | 技術集結

內容簡介《RISC-V嵌入式系統設計》是一本專為嵌入式系統初學者編寫的實用入門教材,圍繞當前熱門的國產RISC-V微

HPM5E31IGN單核 32 位 RISC-V 處理器

HPM5E31IGN單核 32 位 RISC-V 處理器在當今嵌入式系統領域,RISC-V架構正以開源、靈活和高性價比的優勢快速崛起。HPM5E31IGN作為先楫半導體的

發表于 05-29 09:23

FPGA與RISC-V淺談

RISC-V處理器的SoC數量在2024年約為20億顆,到2031年有望突破200億顆。 RISC-V的概念與優勢 RISC-V是一種全新的

發表于 04-11 13:53

?677次閱讀

芯來科技攜手芯芒科技發布RISC-V CPU系統仿真平臺

專業RISC-V處理器IP及解決方案公司芯來科技與杭州芯芒科技深入合作,共同研發推出芯來全系列RISC-V CPU

HPC系統的電源控制器,RISC-V也來插一腳?

HPC系統的電源控制器,RISC-V也來插一腳?

評論